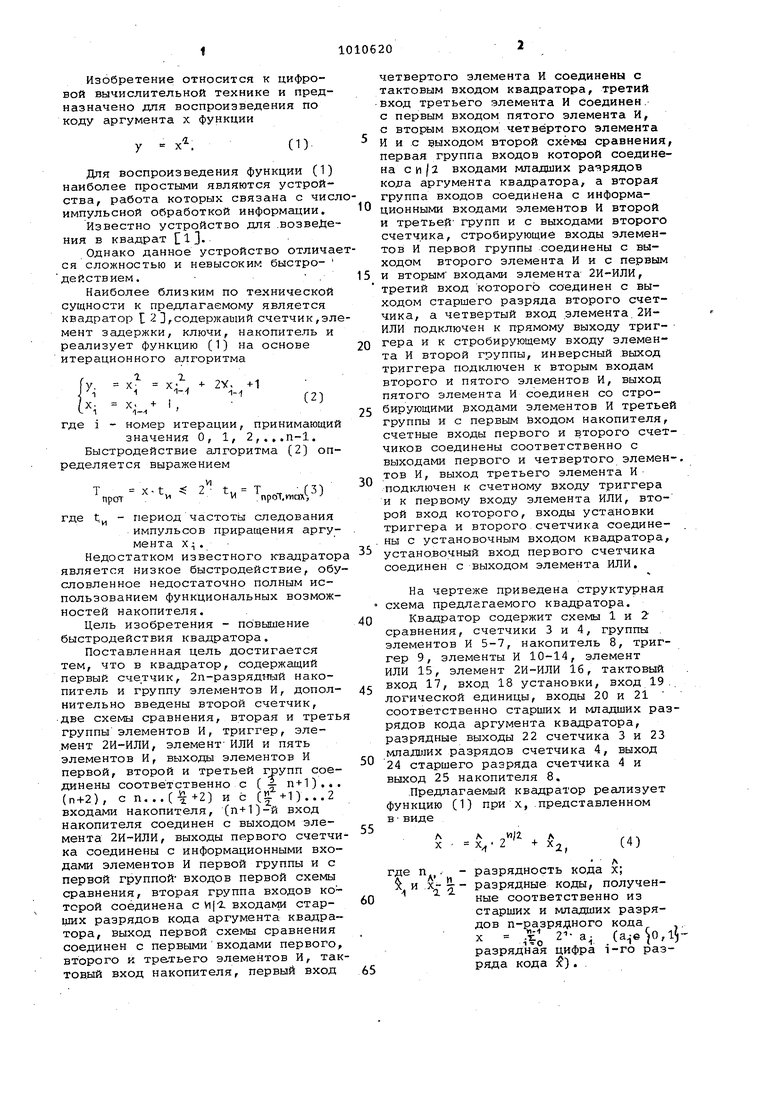

Изобретение относится к цифровой вычислительной технике и предназначено для воспроизведения по коду аргумента х функции у х.(1). Для воспроизведения функции (1) наиболее простыми являются устройства, работа которых связана с чис импульсной обработкой информации, Известно устройство для .возведе ния в квадрат ClJОднако данное устройство отлича ся сложностью и невысоким быстродействием. . Наиболее близким по технической сущности к предлагаемому является квадратор I 2 ,.содержащий счетчик,эл мент задержки, ключи, накопитель и реализует функцию (1) на основе итерационного алгоритма 1 X у. х 2У. +1 t 1 1-1 -1х- х- +I . 11--. /1где 1 - номер итерации, принимающи значения О, 1, 2,...п-1. Быстродействие алгоритма (2) оп ределяется выражением Т x-t, 2 t.. Т , (3) прот . npoT.vnaxS где t - период частоты следования импульсов приращения аргу мента х:; . Недостатком известного квадрато является Низкое быстродействие, об словленное недостаточно полным использованием функциональных возмож ностей накопителя. Цель изобретения - повышение быстродействия квадратора. Поставленная цель достигается тем, что в квадратор, содержащий первый счетчик, 2п-разрядный накопитель и группу элементов И, дополнительно введены второй счетчик, две схемы сравнения, вторая и треть группы элементов И, триггер, элемент 2И-ИЛИ, элемент- ИЛИ и пять элементов И, выходы элементов И первой, второй и третьей групп соединены соответственно с ( п+1),, (п+2), с n,..(-t-2) и с (S. +1)...2 входами накопителя, (п+1)-й вход накопителя соединен с выходом элемента 2И-ИЛИ, выходы первого счетчи ка соединены с информационными входами элементов И первой группы и с первой группой- входов первой схемы сравнения, вторая группа входов которой соединена с входаг-м старших разрядов кода аргумента квадратора, выход первой схемы сравнения соединен с первымивходами первого второго и третьего элементов И, так товый вход накопителя, первый вход четвертого элемента И соединены с тактовым входом квадратора, третий вход третьего элемента И соединен, с первым входом пятого элемента И, с BTojftjM входом четвёртого элемента И и с выходом второй схемы сравнения, первая группа входов которой соединена сц|2 входами младших разрядов кода аргумента квадратора, а вторая группа входов соединена с информационными входами элементов И второй и третьей групп и с выходами второго счетчика, стробирующие входы элементов И первой группы соединены с выходом второго элемента И и с первым и вторым входами элемента 2И-ИЛИ, третий вход которого соединен с выходом старшего разряда второго счетчика, а четвертый вход элемента.2ИИЛИ подключен к прямому выходу триг- гера и к стробирующему входу элемента И второй группы, инверсный выход триггера подключен к вторым входам второго и пятого элементов И, выход пятого элемента И соединен со стробирующими рходами элементов И третьей группы и с nepBfcOM йходом накопителя, счетные входы первого и второго счетчиков соединены соответственно с выходами первого и четвертого элемен-. тов И, выход третьего элемента И подключен к счетному входу триггера и к первому входу элемента ИЛИ, второй вход которого, входы установки триггера и второго счетчика соединены с установочным входом квадратора, устано.вочный вход первого счетчика соединен с выходом элемента ИЛИ. На чертеже приведена структурная схема предлагаемого квадратора. Квадратор содержит схемы 1 и 2 сравнения, счетчики 3 и 4, группы элементов И 5-7, накопитель 8, триггер 9, элементы И 10-14, элемент ИЛИ 15, элемент 2И-ИЛИ 16, тактовый вход 17, вход 18 установки, вход 19 .. логической единицы, входы 20 и 21 соответственно старших и младших разрядов кода аргумента квадратора, разрядные выходы 22 счетчика 3 и 23 младишх разрядов счетчика 4, выход 24 старшего разряда счетчика 4 и выход 25 накопителя 8. .Предлагаемый квадратор реализует функцию (1) при X,.представленном ввиде где п. . - разрядность кода х; 1 и х- разрядные коды, полученные соответственно из старших и младших разрядов п-разрядного кода X 1 а- (,разрядная цифра i-ro разряда кода ). При условии (5) функция (.1) принимает вид . Л1 . л л t. 2 X х- X а - i Работает квадратор циклически, В течение каждого цикла можно выделить два. периода Т1 и Т2 работы квадратора по формуле (5). В течение Т1 прои ходит вычисление сум№а квадратов 2 + $с, а в течение Т2 вычисляется произведение 2 . Перед началом каждого цикла вычис лений на разрядные входы 20 -я 21 квадратора соответственно подаются коды 0 20 и 0 20 2. Период Т1 начинается с поступления на вход 18 импульса установки, по-которому, триггер 9, счетчик 4, накопитель 8, счетчик 3 через элемент ИЛИ 15 устанавливаются в ноль, -После окончания импульса, установки на вход 17 начина ют поступать тактовые импульсы,которые при нулевых выходных сигналах со схем 1 и 2 сравнения через элементы И 10 -и 13 поступают на счетные входы счетчиков 3 и 4 соответственно. При этом на разрядных выходах 22 счетчик 3.формируется код Х;,, поступающий на информационные входы группа элементо И 5 и на первую группу входов схемы 1 сравнения, а на выходах 24 и 23 счетчика 4 формируются соответственн код старшего разряда 0 4 и код млад ших разрядов ф 23 кода .1- Код х, поступает на информационные входы группы элементов И 7 и первую группу I входов схеглы 2 сравнения. Кроме того, коды ( 54 и 02з поступают соответственно на вход элемента 2И-ИЛИ 16 и на информационные входы группы элементов И 6, Схема 1(2) сравнения вырабатывает сигналы единица при Ф22 ($21 ) 0 () и ноль при ( (. В начале вычислений триггер 9 находится в нулевом состоянии, поэтому элементами 11 и 14 И разрешено прохождение выходных кодов счетчика 3 и 4 через- группы элементов И 5 и 7 и соответственно на входы с ( I п+1) по (п + 2) и с ( I -И) по два накопителя 8, а также прохождение единичных сигнсшов через элемент 2И-ИЛИ 16 на вход ( разряда, а через элемент И 14 - на вход младщего разряда накопителя 8. При этом одновременно реализуется алгоритм (2) для функций Л ДЧУт. . xz 2.(5 Период Т1 заканчивается, когда произойдет срайнение на обоих схемах сравнения и вырабатываются сигналы, равные 1, по которым элемент И 12 формирует импульс, устанавливаю 1;ий триггер 9 в 1, а счетчик 3 через элемент ИЛИ 15 - в О. Таким образом, за время ,Ч. . Т1 « 2 на кодовых выходах 25 накопителя 8 формируется код Состояние 1 триггер 9 разрешает работу квадратора в периоде Т2, т.е.. запрещает работу элементов И 11 и 14, групп элементов И 5 и 7 и через элемент 2И-ИЛИ 16 группы элементов И 6 подключает на соответствующие входы накопителя 8 код х Таким образом формируется произведение х до тех пор, пока выход схемы 1 сравнения не станет равным 1. . Процесс вычисления заканчивается при единичном состоянии выходов схем 1 и 2 сравнения и триггера 9, при этом прекращается подача тактовых импульсов на вход 17 квадратора, а с выходов 25 накопителя 8 можно снимать код функции (1) до прихода следующего импульса установки. Длительность периода Т2 определя-. ется так -Гц Из сказанного выше следует, что общее время вычисления функции (1) определяется выражением т Т1 + Т2 : 2 - t., Сравнивая выражения (3) и (8) получим.л11а. , Так, при п 8 . YMf -о Таким образом, быстродействие предлагаемого квадратора (см. оценку (9) выше быстродействия известного.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Квадратор | 1983 |

|

SU1092501A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Цифровой функциональный преобразователь | 1978 |

|

SU742951A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Квадратор | 1980 |

|

SU955043A1 |

КВАДРАТОР, содержащий первый счетчик, 2п-разрядный накопитель и группу элементов И, от ли ч d ющ и и с я тем, ч-Ьо, с целью повышения быстродействия, в него введены второй счетчик, две схемы сравнения, вторая и третья группы элементов И, триггер, элемент 2И-ИЛИ, элемент ИЛИ и йять элементов И, выходы эле«яентов И первой, второй и третьей групп соединены соответственно с (п-ь1)...(п+2), с п...(+2) и с (). ..2 входами накопителя, ()-й вход накопителя соединен с выходом элемента 2И-ИЛИ, быходы первого счетчика соединены с информационными входами элементов И первой группы и с первой группой входов первой схемы сравнения, вторая группа входов которой соединена: с йД входами старших разрядов кода аргумента квадратора, выход первой схемы сравнения соединен с первыми входами первого второго и третьего элементов И, тактовый вхол накопителя, первый вход четвертого элемента И соединены с тактовым входом квадратора, третий вход.третьего элемента И соединен с первым входом пятого элемента И, с вторым входом четвертого элемента И и с выходом второй cxehojсравнения, первая группа входов которой соединена с hji входами младших разрядов кода аргумента квадратора, а вторая группа входов соединена с информационньшк входами элементов И второй и третьей групп и с выходами йторого счетчика, стробирукяцйе входы элементов И первой группы соединены с выходом второго элемента И и с первым и вторым входами элемента 2И-ИЛИ, третий,вход которого соединен с выходом Старшего разряда второго счетчика, а четвертый вход элемента 2И-ИЛИ подключен к прямому выходу триггера и к стробирующему входу элементов И второй группы, инверсный выкод триггера подключен к вторым входам второго и пятого элементов И, выход пятого элемента -И соединен со стробируюцими входами элементов И третьей группы , и с первым входом накопителя, счет ные входы первого и второго счетчиков соединены соответственно с выходами первого и четвертого элемеЯ ; О тов И, выход третьего элемента И подключен к счетному входу триггера ф ft к первому входу элемента ИЛИ, . второй вход которого, входы установки триггера и.второго с4втчя ка соединены с установочным входом квадратора, установочный бход первого счетчика соединен с выхо1;ом элемента ИЛИ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-07—Публикация

1981-11-11—Подача