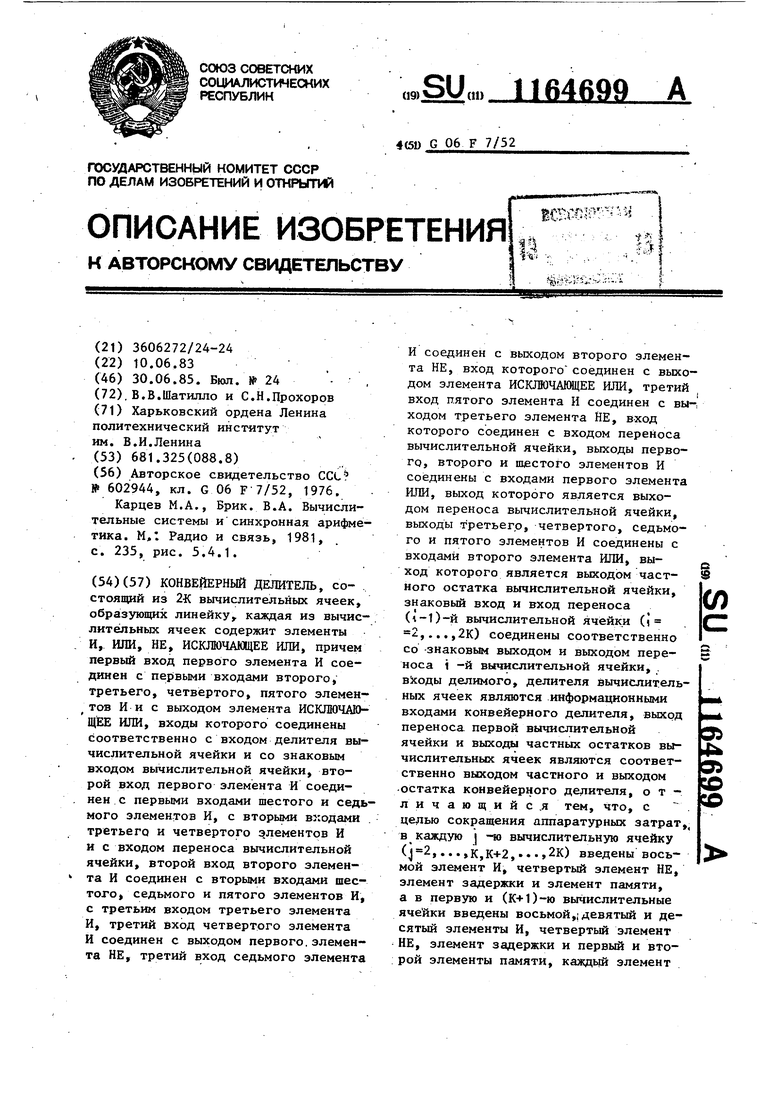

памяти содержит четьфе элемента И, элемент ИЛИ, элемент НЕ и. элемент задержки, выход которого соединен с входом элемента НЕ, а вход является входом разрешения подачи информации па элемент памяти, с которым соединены первые входы первого и второго элементов И, первый вход третьего элемента И соединен с выходом элемента НЕ, второй вход первого элемента И и второй вход третьего элемента И, соединенный с первым входом четвертого элемента И, являются информационными входами элемента памяти, второй вход второго элемента И является входом сброса элемента памяти, третий вход второго элемента И соединен с вторым входом четвертого элемента И и с выходом элемента ИЛИ, который является информационным вы- ходом элемента памяти, выходы первого, второго, третьего и четвертого элементов И соединены с входами элемента ИЛИ, причем вход разрешения подачи Ш1формации и вход сброса элемента памяти являются соответствующими управляющими входами вычислительной ячейки,информационные входы первого элемента памяти всех вычислительных ячеек являются соответственно информационными входами делимого и частного остатка вычислительной ячейки, информационные входы второго элемента памяти первой и (К4-1)-й вычислительных ячеек являются соответственно входами установки единицы и знакового сигнала этих вычислительных ячеек, выход первого элемента памяти в каждой вычислительной ячейке соединен с третьими входами третьего, седьмого и пятого элементов И и с входом первого элемента НЕ первый вход восьмого элемента И соединен с выходом второго элемента ЮИ, второй вход восьмого элемента И соединен с первым управляющим входом вычислительной ячейки, четвертые входы третьего, четвертого, седьмого и пятого элементов И соединены с выходом четвертого элемента НЕ, вход которого соединен с выходом элемента задержки, вход которого соединен с первым управляющим входом вычислительной ячейки, выход восьмого элемента И соединен с входом .второго элемента ИЛИ, выходы вторых элементов памяти первой и (К+1)-и вычислительных ячеек являются выходами их знаковых сигналов,входы девятого элемента И в первой и (К+1)-й вычислительных ячейках соединены соответственно с выходом первого элемента ИЛИ и с первым управляющим входом вычислительной ячейки, входы десятого элемента И в первой и (К+1)-й вычислительных ячейках соединены соответственно с первым управляющим входом и входом установки единицы вычислительной ячейки, выходы девятого и десятого элементов И соединены с входами первого элемента ИЛИ, входы знаковых сигналов всех вычислительных ячеек, кроме первой и (К+1)-и соединены между собой, выход частного остатка каждой последующей вычислительной ячейки с входом частного остатка предыдущей вычислительной ячейки, вход разрешения подачи информации каждой вьгчисли -ельной ячейки кроме К-й соединен с входом разрешения подачи информации каждой последующей вычислительно ячейки, .вход сброса каждой вычислительной ячейки соединен с входом сброса последующей вычислительной ячейки, выход переноса первой вычислительной ячейки соединен с входом переноса и знаков.ым входом 2 К-й вычислительной ячейки, вход частного остатка 2К-й вычислительной ячейки является информационным входом конвейерного делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1683009A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления | 1988 |

|

SU1681303A1 |

| Ячейка однородной структуры | 1990 |

|

SU1805461A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Матричное устройство для деления | 1987 |

|

SU1511748A1 |

| Матричное устройство для деления /его варианты/ | 1981 |

|

SU1035602A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

КОНВЕЙЕРНЫЙ ДЕЛИТЕЛЬ, состоящий из 2К вычислительных ячеек, образующих линейку, каждая из вычислительных ячеек содержит элементы И, ШШ, НЕ, ИСКЛЮЧАЮЩЕЕ ШШ, причем первый вход первого элемента И соединен с первыми входами второго, третьего, четвёртого, пятого элемен, тов И и с выходом элемента ИСКЛЮЧАЮЩЕЕ ШШ, входы которого соединены соответственно с входом делителя вычислительной ячейки и со знаковым входом вычислительной ячейки, второй вход первого элемента И соединен .с первыми входами шестого и седьмого элементов И, с вторьми вводами третьего и четвертого элементов И и с входом переноса вычислительной ячейки, второй вход второго элемента И соединен с вторыми входами шестого седьмого и пятого элементов И, с третьим входом третьего элемента И, третий вход четвертого элемента И соединен с выходом первого,элемента НЕ, третий вход седьмого элемента И соединен с выходом второго элемента НЕ, вход которого соединен с выходом элемента ИСКЛЮЧАНЩЕЕ ИЛИ, третий вход пятого элемента И соединен с выходом третьего элемента НЕ, вход которого соединен с входом переноса вычислительной ячейки, выходы первого, второго и шестого элементов И соединены с входами первого элемента ИЛИ, выход которого является выходом переноса вычислительной ячейки, выходы третьего, четвертого, седьмого и пятого элементов И соединены с входами второго элемента ИЛИ, выход которого является выходом частного остатка вычислительной ячейки, О) знаковый вход и вход переноса

Изобретение относится к вычислительной технике и может быть исполь

зован.о в специализированных цифровых вычислительных устройствах.

Целью изобретения является сокращение аппаратурных затрат.

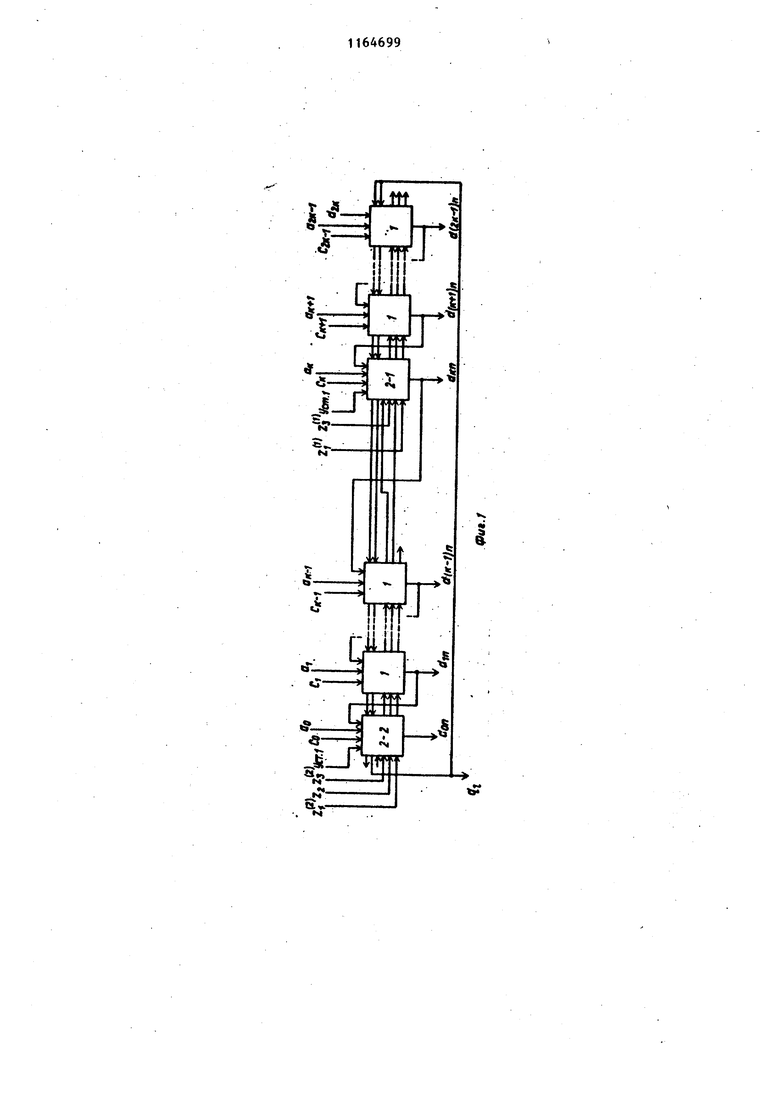

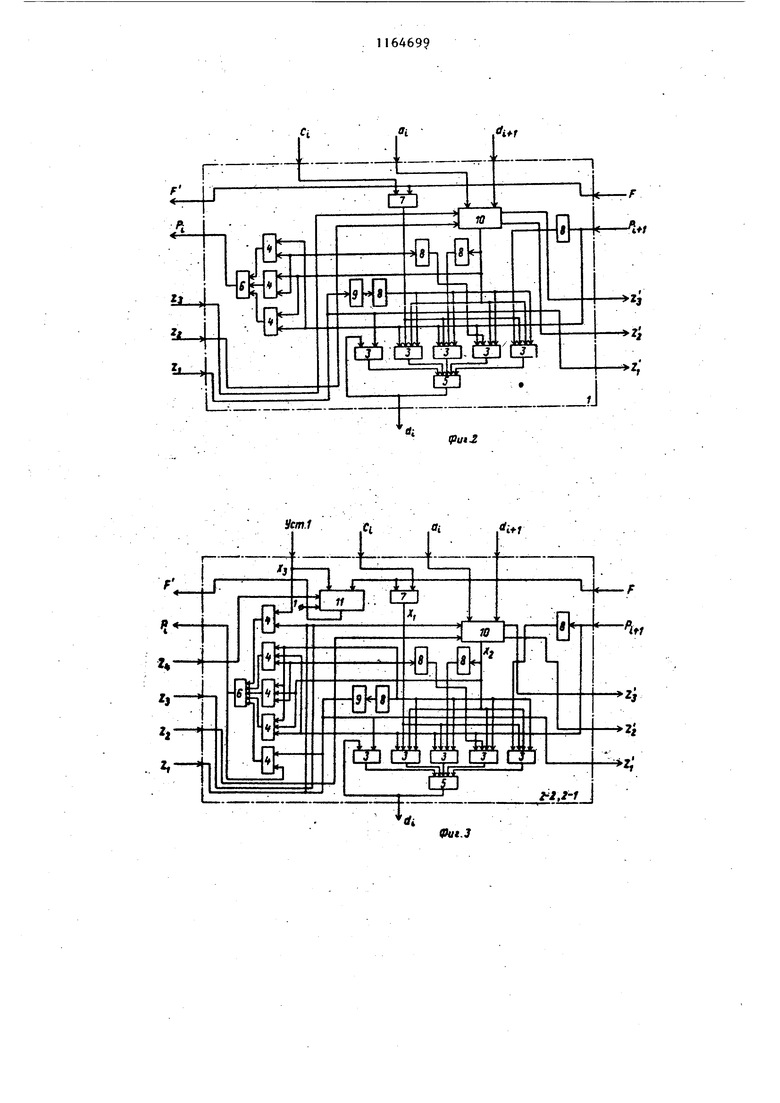

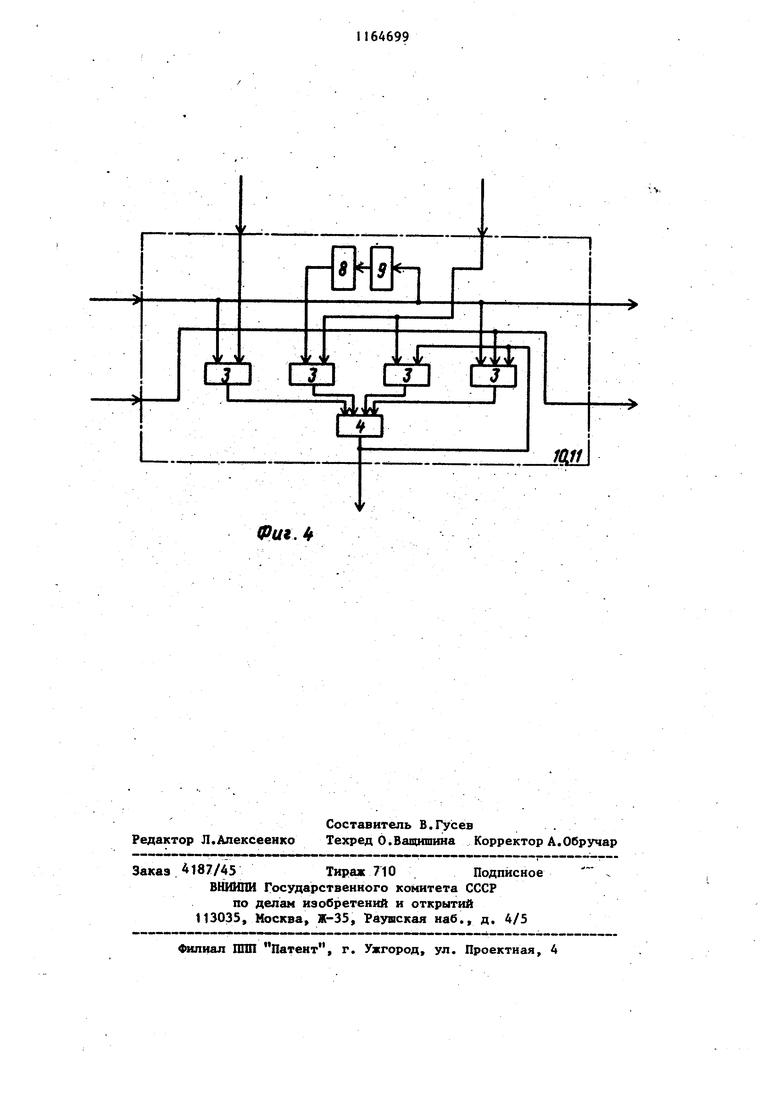

На фиг,.1 представлена функциональная схема предлагаемого конвейерного делителя; на фиг.2 - функциональ- 5 ная схема вычислительной ячейки первого типа; на фиг.З - функциональная схема вычислительных ячеек второго типа; на фиг.4 - функциональная схема элементов памяти.

Конвейерный делитель состоит из 2К вычислительных ячеек 1-2, образующих линейку, каждая i -я (,...,2K) вычислительная ячейка 1 содержит группы из пяти злементов.И. 3, группу 5 из трех элементов И 4, элементы ИЛИ 5 и 6, элемент ИСКЛЮЧАЩЁЕ-ИЛИ 7, четыре элемента НЕ 8, элемент.9 задержки и элемент 10 памяти, а первая и (К+1)-я вычислительные ячейки 2 Ч) содержат группу из пяти элементов ИЗ, группу из пяти элементов И 4, элементы ИЛИ, 5 и 6, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, четыре элемента НЕ 8, элемент 9 задержки и элементы Ю и- 11 памяти.

Работа делителя организована еледующим образом.

Две ступени конвейера, замкнутые информационно друг от друга, рабо- 30 тают поочередно: пока в одной вдет подготовка к вычислению, в другой вычислительный процесс, и наоборот.. При этом для достижения максимальной производительности, минимальное чис- 35 ло ячеек в ступени конвейера выбирается так, чтобы время, необходимое .на подготовку одной ступени конвейера к вычислению, не превышало времени вычислительного процесса в другой 40 ступени конвейера.

В исходном состоянии на управляющих входах Z, , Z2,.Zj, Z j установлен сигнал l, на управляющем вхо- де - сигнал О.45

Эти управляющие воздействия в первой и второй ступени конвейера готовят элемент Ю памяти к приему информации о делимом, разрешают работу схемам формирования суммы 50 первой ступени конвейера и схеме формирования переноса вычислительной ячейки 2-1.,

Процесс вычисления начинается с подачи на информационные входы Со 55

ответствующих разрядов чисел С и А,

а на управляющие входы Zg и Установка 1 - соответственно сигналов О или 1. Сигнал О на управляющем входе Zg осуществляет сброс элементов Ю и 11 всех вычислительных ячеек. Сигнал 1 на входе Установка 1 устанавливает в исходное состояние схему формирования переноса вычислительной ячейки 2-2 и элемента 11 памяти, на выходах которых устанавливается сигнал 1.

Для правильной установки начальной информации длительность t сигнала О на входе Z(после чего установлен в l) и длительность t хранения разрядов числа А на входах конвейерного делителя и 1 на входе Установка 1 (тюсле чего установлены в О) должны удовлетворять условиям

i.

jV

moiic или)

( 1 , л Г .

Xj Т/, niaK и-«тпщ И J

2 Unioix и -пг)01« ИЛИ «а net.ил или ,мц максимальное время переходного процесса соответственно, в логическом элементе ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ.

Разряды делителя С хранятся на входах конвейерного делителя в течение всего времени деления.

После установления на выходах элементов 10 и 11 памяти начальных состояний, т.е. соответственно раз- .рядов делимого и единицы, и на схеме формирования переноса вычислительной ячейки 2-2 начального состояния, соответствующего единице на выходе, схемы формирования суммы и схемы формирования переноса первой ступени конвейера начинают вычисление младщих разрядов первого остатка dj,

CK4i5i (2i:-i)f переноса из первой ступени конвейера, котороезаканчивается верез время Т, определяемое временем распространения переходного процесса сквозь все схемы формирования переноса, первой ступени конвейера и равное

f

Vi-mciir и тпо )твхио.или

В момент времени Т, равный

7 Т + .

V-niaxv inair или}

появляется сигнал переноса на выходе схеь;ы формирования переноса вычислительной ячейки 2-1, который является сигналом переноса из первой ступени конвейера. Одновременно с ним появляется сигнал на выходе схемы

формирования суммы вычислительной ячейки- 2-1, последней из схем формирования суммы в первой ступени конвейера, остальные к этому моменту времени уже закончили работу.

В момент времени Т первая ступень конвейера заканчивает работу и на управляющий вход Z подается сигнал 1, который осуществляет запоминание информации на выходах схем формирования суммы вычислительных ячеек 1 и 2-1 первой ступени конвейера и на выходе схемы формирования переноса вычисрительной ячейки 2-1, и запрещает отработку сигналов на их входах. Независимо от этого в вычислительных ячейках второй ступени конвейера продолжается вычисление в течение времени Т-1 j „(.

Пока во второй ступени конвейера идет вычисление, в первой ступени конвейера производится подготовка к второму циклу вычислений, заключающаяся в переписи К-1 младших-разрядов первого частного остатка dfj,) 1(((п-л)1 полученного на соответствующем выходе V -и вычислительной ячейки, в элемент 10 памяти (1-1)-й вычислительной ячейки, где , К-ь2,... ,2К-1, при этом одновременно на вход делителя d подается следующий разряд делимого A-aj который записывается в элемент 10 памяти (2К-1)-и вычислительной ячейки 1. Запись производится с помощью отрицательного импульса, длительностью t, на управляющем входе Z, подаваемом в момент времени ., определяемый

;Ц -Л rnciv Мб та-х И man ил« з t Ь v; max min и «ли) л

где ь,пахне максимальное время переходного процесса в эле« пЧпили менте НЕ; mib не минимальное время переходного процесса соответственно в элементах ИЛИ

и НЕ. В момент времени Т + tj, где

tj & НЕ . на управляющий вход Z подается сигнал О, который разрещает работу схемам формирования суммы второй ступени конвейера и схеме формирования переноса вычислительной ячейки 2-2. К этому моменту времени во второй ступени конвейера происходит

распространение переноса через все схемы формирования переноса вычислительных ячеек 1, в первой ступени 5 конвейера заканчивается запись в элементы 10 памяти, т.е. первая ступень конвейера готова к следующим вычислениям и поэтому, хотя 0 сбрасывает установленное на выходе схемы формирования переноса вычислительной

ячейки 2-2 единичное значение знакового сигнала F, необходимое для первого цикла деления, это уже не отражается на правильности результата 5 первой ступени конвейера. Единичное значение зчакового сигнала F, необ-ходимое для правильной работы второй ступени конвейера в первом цикле деления, об.еспечивае.тся выходом элемента 11 памяти вычислительной ячейки 2-1.

Поскольку схемы формирования суммы работают параллельно, к моменту времени т+Т -с ,зaкaнчивaeтcя

5 работа второй ступени конвейера, т.е. формируется сигнал переноса и заканчивается формирование старших разрядов частного остатка d, d,... d()(.,) . Первый цикл деления на этом

0 закончен. Сигнал переноса из второй ступени конвейера является первым разрядом частного q( и одновременно знаковым сигналом F для второго цикла деления. В момент вpieмeни Т+Т5 -пах исх.илцНа управляюп1Ий вход Z, подается сигнал 1, который осуществляет запоминание информации на выходах схем формирования суммы второй ступени конвейера и навыходе

0. схемы формирования переноса вычислительной ячейки. 2-2 и запрещает отработку сигналов, которые проявляются на их входах. ,

Сразу послепоявления первого

5 разряда частного q процесс вычисления продолжается в элементах ИСКШОЧАЮЩЕЕ ИЛИ .и схемах формирования переноса первой ступени конвейера. Пока идет вычисление в первой ступени конвейера, независимо от этого осуществляется считывание первого разряда частного q, с выхода qj конвейерного делителя и перезапись К старщих разрядов d,,,d,,. vi ,d(,, первого частного остатка с соответствующего выхода 1 -и вычислительной ячейки в элементы 10 памяти ((-1)-й вычислительной ячейки второй ступени, где i 1,2,...,К. Разряд частного остатка dp. до этого момента времени хранится на выходе схемы формирования суммы вычислительной ячейки 2-1, поскольку Z еще равен l. Перезапись осуществляется подачей отрицательного импульса дли тельностью tj на вход ZJB момент времени т+Ц, где J.T- о -nia vic(. илиСигнал управления второй ступени конвейера является для элемента 11 памяти вычислительной ячейки 2-1 си налом управления Z (фиг.З), осущес вляющим запоминание знакового сигна ла F для второй ступени во втором цикле деления q. В момент времени Т +t5 сигналом О на входе разрешается работасхем формирования суммы первой сту-пени конвейера и схемы формировангЫ переноса вычислительной ячейки 2-4 Процесс продолжается циклически пока не вводятся все m-ZK+1 младших разрядов делимого А и не считываются все ра.зряды частного Q с выхода Для обеспечения правильной работы делителя, максимального быстродействия, а также возможности счи.тывЯния разрядов частного и коммута ггаи разрядов делимого минимальное . 98 количество вычислительных ячеек К в ступени конвейера определяется из следуннцей системы неравенств: - , так Иск. или С2 min к или max и max илиг rnqn исг.или ) Т Ц .,, У 13 гаа не то И глох И АИ i HE(f4jn и или)) НС ; & (-«lin HEjj где ),( частота, с которой могут коммутироваться разряды де-. Tgj - время, необходимое для считывания одного разряда дели- мого f Если подача разрядов А и считывание разрядов частного Q осуществляется с прмощыо сдвиговых регистров, то учитывая их быстродействие относительно быстродействия логических элементов И, ШШ, ИСКПЮЧАЮ1ЦЕЕ ИЛИ, НЕ, минимальное количество ячеек К в ступени.конвейера, необходимое для,правильной работы делителя, равно трем ()

Уап.1 liOi

tfi

9ut.3 .

| Устройство для деления | 1975 |

|

SU602944A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Карцев М.А., Брик | |||

| В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| М,: Радио и связь, 1981, с | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-06-30—Публикация

1983-06-10—Подача