мент НЕ - к первому входу второго сумматора, второй вход которого соединен со вторым входом ячейки, вход и выход переноса, второго сумматора соединены соответственно с дополнительным входом и выходом переноса ячейки,

2. Матричное устройство для деления., содержащее матрицу ячеек из п строк.и m столбцов, причем первые входы ячеек первой строки подключены к входам делителя устройства, а атбрые входы ячеек первой строки и столбца - к входам делимого устройства, управляющий вход ячеек каждой строки, за исключением ячеек первого столбца, подключен к выходу управления ячейки предыдущего столбца той же строки, второй вход каждой ячейки, эа исключением ячеек первой строки и т-го столбца, подклю чен к выходу суммы ячейки предыдущей строки и последующего столбца, первый вход каждой ячейки всех стоЯб цов, за исключением ячеек первой строки, подключен к первому выходу. ячейки того же столбца предыдущей строки, вход переноса каждой ячейки всех строк, за исключением ячеек т-го столбца., подключен к выходу переноса ячейки последующего столбца этой же строки, управляющий вход первой ячейки первого столбца подклю чен к входу сигнала единичного уровня устройстваS выхода переноса ячеек первого столбца нечетных строк подключены к выходам нечетных разря,дов частного устройства, выход управления каждой ячейки т-го столбца, за исключением ячеек четных строк, подключен к входу переноса той же ячейки, выходы суммы ячеек п-й строки соединены с выходом остатка устройства, причем каждая из ячеек нечетных строк матрицы содержит сумматор и элемент ИСКЛЮЧАОДЕЕ ИЛИ, выход которого подключен к входу сумматора, первый вход - к управляющему входу и выходу управления, а второй вход - к первому входу и пеовому выходу ячейки, второй вход которой подключен ко второму входу сумматора, вход переноса, выход переноса и выход суммы которого подключены соответственно к входу и выходу переноса и к выходу суммы ячейки, а каждая из ячеек четных строк матрицы содержит первый сумматор, первый вход которого подключен ко

35602

второму ВХОДУ ячейки, вход и выход переноса со.единены соответственно с входом и выходом переноса ячейки, отличающееся тем, что, с целью повышения быстродействия, оно содержит и/2. элементов НЕ, выхо.ды которых подключены к выходам четных .разрядов частного устройства и управляющим-входам соответствующих ячеек первого столбца нечетных строк, за исключением пер{зой ячейки первого столбца, а вход - к выходам суммы ячеек первого столбца предыдущих четных строк, дополнительный вход переноса каждой ячейки четных строк, за исключением ячеек т-го столбца, подключен к дополнительному выходу переноса ячейки последующего столбца той же стройки, входы переноса и дополнительные входы переноса ячеек четных строк лп-го столбца подключены соответственно к входам сигналов нулевого и единичного уровней , а выход суммы каждой ячейки первого столбца нечетных строк подключен к упра8ляюи1ему входу ячейки последующей строки того же столбца, а ячейка устной строки матрицы дополнительно содержит, второй сумматор, элемент НЕ, коммутатор причем первый и второй входы коммутатора соединены соответственно с выходами первого и второго сумматоров, вход управления коммутатора соединен с управляющими входом и выходом ячейки, а выход соединен с ыходом суммы ячейки, первый вход которой подключен к второму входу первого сумматора, первому выходу ячейки и через элемент НЕ - к первому входу второго сумматора, второй вход которого соединен со вторым входом ячейки, вход и выход переноса второго сумматора соединены соответственно с дополнительными входом и выходом переноса ячейки.

3. Матричное устройство ,аля деления, содержащее матрицу ячеек из п строк и m столбцов, причем первые входы ячеек первой строки подключе-. ны к входам делителя устройства, а вторые входы ячеек первой строки и гп-го столбца - к входам значащих разрядов делимого устройства, управляющий вход ячеек каждой строки, за исключением ячеек первого, столбца, подключен к выходу управления ячейки предыдущего столбца той же строки, второй вход каждой ячейки

всех строк, за исключением ячеек первой стройи и т-го столбца, подключен к выходу суммы ячейки предыдущей строки и последующего столбца, первый вход каждой ячейки всех столбцов, за исключением ячеек первой строки, подключен к первому выходу ячейки того же столбца предыдущей строки, вход переноса каждой ячейки всех строк, за исключением ячеек т-го столбца, подключен к выходу переноса ячейки последующего столбца этой же строки, ячейка содержит первый сумматор, первый вход которого подключен к второму входу ячейки, вход и выход переноса соединены соответственно с входом и выходом переноса ячейки, отличающееся тем, что, с целью повышения быстродействия, оно-содержит п+1 элементов ИСКЛЮЧАЮУ1ЕЕ ИЛИ, элемент НЕ и дополнителную строку из п-1 ячеек, выходы суммы ячеек которой подключены к выходам значащих разрядов частного устройства, выход знакового разряда которого подключен к выходу первого элемента ИСКЛЮЧАОДЕЕ ИЛИ и управляющему входу первой ячейки первого столбца, первый вход которой подключен к первому входу первого элемента ИСКЛЮЧАВДЕ.Е ИЛИ, второй вход которого подключен к входу знакового разряда делимого устройства,входы каждого из остальных элементов ИСКЛЮЧАЩЕЕ ИЛИ подключены к выходу суммы и первому выходу соответствующей ячейки первого столбца, а выхо .элементов ИСКЛЮЧАОДЕЕ ИЛИ, за иск Йочением первого и последнего элементов, подключены к соответствующи первым входам ячеек дополнительной

строки, вход переноса и дополнительный вход переноса каждой ячейки дополнительной строки, за исключением последней ячейки этой же строки, подключен к выходу переноса и дополнительному входу переноса последующей ячейки этой же-строки, управляющие входы и выходы управления

ячеек дополнительной строки попарно соединены между собой, а управ ляющий вход первой ячейки этой же строки подключен к входу сигнала нулевого уровня, выход последнего элемента ИСКЛЮЧАЮСЦЕЕ ИЛИ через элемент НЕ подключен к дополнительному входу переноса последней ячейки дополнительной строки, вторые входы ячеек которой подключены к входу сигнала нулевого уровня устройства, входы переноса и входы дополнительного переноса ячеек т-го 1 столбца подключены соответственно к входам сигналов нулевого и единичного уровней, ячейка дополнительно содержит второй сумматор, элемент НЕ, комму татор, причем первый и второй входы коммутатора соединены соответственно с выходами первого и второго сумматоров, вход управлений коммутатора соединен с управляющими входом и выходом ячейки, а выход коммутатора соединен с выходом суммы ячейки, рервый вход которой подключен ко второму входу первого сумматора, первому выходу ячейки и через элемент НЕ - к первому входу второго сумматора, второй вход которого соединен со вторым входом ячейки, вход и выход переноса второго сумматора соединены соответственно с дополнительными входом и выходом переноса ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1134948A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1024910A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750485A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

1. Матричное устройство для деления, содержаи(ее матрицу ячеек из п строк и п1 столбцов, причем первые входы ячеек первой строки подключены к входам делителя устройства, вторые входы ячеек первой строки и столбца подключены к входам делимого устройства, выходы суммы ячеек п-й строки являются выходом остатка устройства, управляющий вход ячеек каждой строки, за исключением ячеек первого столбца, подключен к выходу управления ячейки предыдущего столбца той же строки, второй вход каждой ячейки всех строк, за исключением ячеек первой строки и т-го столбца, подключен к выходу суммы ячейки предыдущей строки и последующего столбца,первый вход каждой ячейки всех столбцов, за исключением ячеек первой строки, подключен к первому выходу ячейки того же столбца предыдущей строки, вход переноса каждой ячейки всех строк за исключением ячеек т-го столбца, подключен к выходу переноса ячейки последукнцего столбца этой же строки, а управляющий вход первой ячейки первого столбца подключен к входу сигнала единичного уровня устройства, каждая ячейка содержит первый сумматор, первый вход которого подключен ко второму-входу ячейки, вход и выход переноса соединены соответственно с входом и выходом переноса ячейки, отличающееся тем, что, с целью повышения быстродействия, оно содержит п-1 элементов НЕ, причем выходы элементов НЕ являются выходами частного устройства, вход каждого элемента НЕ о т подключен к выходу суммы соответствующей ячейки первого столбца и к управляюи;ему входу ячейки последуюЁ: щей строки того же столбца, дополнительные входы переноса каждой ячейки всех строк, за исключением ячеек т-го столбца, подключены к дополнительному выходу переноса ячейки последующего столбца той же строки, входы переноса и дополнительо ные входы переноса ячеек т-го столбоо ца подключены соответственно к вхоСП дам сигналов нулевого и единичного 05 уровней, каждая ячейка дополнительо ю но содержит второй сумматор, элемент НЕ, коммутатор, причем первый и второй входы коммутатора соединены соответственно с выходами первого и второго сумматоров, вход управления коммутатора соединен с управляющими входом и выходом ячейки, а выход соединен с выходом суммы ячейки, первый вход которой подключен ко второму входу.первого сумматора, первому выходу ячейки и через эле

1

1

Изобретение относится к вычислительной технике и может ,быть использовано в быстродействующих процессорах и специализированных вычислителях.

Известно матричное вычислительное устройство для выполнения деления двоичных чисел, представленных в дополнительных кодах, содержащее итеративную сеть сумматоров вычитателей, управляющие входы которых подключены к выходам соответствующих элементов ИСКЛЮЧАЩЕЕ ИЛИ, а выходы переноса - к блоку заключительной коррекции t 1 J.

Недостатком этого устройства является низкое быстродействие, обус3

ловленное последовательностью работы сумматоров-вымитателей.

Наиболее близким по технической сущности к предлагаемому является матричное устройство дл-я выполнения деления, содержащее матрицу ячеек из п строк и п столбцов, при.чем в первый, второй, третий и четвертый входы ячейки i-и строки j-ro столбца соединены соответственно с первым выходом ячейки i-и строки ()-ro столбца, вторым выходом ячейки (-1)-й строки j-ro столбца, третьим выходом ячейки i-и строки {j+l)-ro столбца и четвертым выходом ячейки (-1)-й строки (j+l)-ro столбца, первый вход ячейки i-й стрки первого столбца соединен с третьим выходом ячейки ()-й строки первого столбца, первый выход ячейки i-и строки п-го столбца соединен с третьим входом ячейки i-й строки п-го столбца, вторые входы ячеек первой строки являются входами делителя устройства, четвертые входы ячеек первой строки и п-го столбца являются входами делимого устройства, третьи выходы ячеек первого столбца являются выходами частного устройства, четвертые выходы ямеек п-й строки являются выходами остатка устройства (,n; ,n.) 2.

При этом каждая ячейка содержит одноразрядный сумматор и элемет ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход ячейки соединен с первым выходом ячейки и первым входом -элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен со вторым входом и втрым выходом ячейки, а выход соединен с первым входом сумматора, второй вход которого соединен с четвертым входом ячейки, а выход суммы, вход переноса и выход переноса соединены соответственно с четвертым выходом, третьим входом и третьим выходом ячейки 2.

Недостатком этого устройства является низкое быстродействие, обусловленное последовательной работой ямеек соседних строк, выраженной в необходимости совмеидения начала работы последующей строки с моментом получения результата и окочан11ем работы всех ямегК предыдущей строки.

Цель изобретения - увеличение быстродействия устройст ва,

35602 4

Поставленная цель достигается тем, что матричное устройство для деления, содержащее матрицу ячеек из л строк и m столбцов, причем первые 5 входы ячеек первой строки подключены к входам делителя устройства, вторые входы ячеек первой строки и столбца подключены к входам делимого устройства, выходы суммы ячеек п-й

О строки являются выходом остатка

устройства, управляющий вход ячейки каждой строки, за исключением ячеек первого столбца, подключен к выходу управления ячейки предыдущего столбца

15 той .же строки, второй вход каждой ячейки всех строк, за исключением ячеек первой строки и т-го столбца, подключен к выходу суммы ячейки предыдущей строки и последующего столбца, первый вход каждой ячейки всех

столбцов за исключением ячеек строки, подключен к первому выходу ячейки того же столбца предыдущей строки, вход переноса каждой ячейки всех строк, за исключением ячеек т-го столбца, подключен ч выходу переноса ячейки пocлeдyюu eo столбца Этой же строки, а управляющий вход первой ячейки первого столбца подключей к входу сигнала единичного уровня устройства, каждая ячейка содержит первый сумматор, первь й вход которого подключен ко второму входу ячейки, вход и выход переноса

соединены соответственно со входом и выходом переноса ячеыки, дополнительно содержит п-1 элементов НЕ, причем выходы элементов НЕ являются выходами частного устройства, вход

каждого элемента НЕ подключен к выходу суммы соответствующей ячейки первого столбца и к управляющему входу ячейки последующей строки того же столбца, дополнительные Е;ХОДЫ переноса каждой ячейки всех строк, за исключением ячеек т-го столбца, подключен к дополнительно му выходу переноса ячейки последующего столбца той же строки, входы

переноса и дополнительные входы пе- реноса ячеек т-го столбца подключены соответственно к входам сигналов нулевого и единичного уровней, каждая ячейка дополнительно содержит

второй сумматор, элемент НЕ, коммутатор, причем первый и второй входы коммутатора соединены соответственно с выходами первого и втоS

рого сумматоров, вход управления коммутатора соединен с управляющими входом и выходом ячейки, а выход соединен с выходом суммы ячейки, первый вход которой подключен ко второму входу первого сумматора, первому выходу ячейки и через элемент НЕ - к первому входу второго сумматора, второй вход которого соединен со вторым входом Тнчейки, вход и выход переноса второго сумматора соединены соответственно с дополнительными входом и выходом переноса ячейки.

Кроме того, матричное устройство для деления, содержащее матрицу ячеек из п строк и m столбцов, причем первые входы ячеек первой С1РОКИ подключены к входам делителя устройства, а вторые входы ячеек первой строки и т-го столбца к входам делимого устройства, управляющий вход ячеек каждой строки, за исключением ячеек первого столбца, подключен к выходу управления ячейки предыдуи)его столбца той же строки; второй ВХОД каждой ячейки, за исключением ячеек первой строки и т-го столбца, подключен к выходу суммы ячейки предыдущей строки и последующего столбца, первый вход каждой ячейки всех столбцов, за исключением ячеек первой строки, подключен к первому выходу ячейки того же столбца предыдущей строки, вход переноса каждой ячейки всех строк, за исключением ячеекщ-го столбца, подключен к выходу перенос ячейки последующего.столбца той же строки, управляющий вход первой яче ки первого столбца подключен к входу сигнала единичного уровня устройства, выходы переноса ячеек первого столбца нечетных строк подключены к выходам нечетных разрядов частного устройства, выход управления каждой ячейки т-го столбца, за исключением ячеек четных строк, подключен к входу переноса той же ячейки, выходы суммы ячеек строки соединены с выходом остатка устройства, причем нечетные строки матрицы содержат ячейки, каждая из которых содержит сумматор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к входу сумматора, первый вход - к управляющему входу и выходу управления ячейки, а второй входк первому входу и первому выходу

35602

ячейки, второй вход которой подключен к второму входу сумматор, вход переноса, выход переноса и выход суммы которого подключены соответственно к входу и выходу переноса и к выходу суммы ячейки, а четные строки матрицы содержат ячейки, каждая из которых содержит первый сумматор, первый вход которого подключен ко

10 второму входу ячейки, вход и выход переноса соединены соответственно с входом и выходом переноса ячейки, дополнительно содержит И/1 элементов НЕ, выходы которых подключены к выходам четных разрядов мастного устройства иуправляющим входам соответствующих ячеек первого столбца нечетных строк, за исключением первой ячейки первого столбца, а вход - к

20 выходам суммы-ячеек первого столбца предыдущих четных строк, дополнительный вход переноса каждой ячейки четных строк, за исключением ячеек Ж-го столбца, подключены к дополнительному выходу переноса ячейки последующего столбца той же строки, входы переноса и дополнительные входы переноса ячеек четных строк yirro столбца подключены соответственно к входам сигналов нулевого и единичного уровней, а выход суммы каждой ячейки первого столбца нечетных строк подключен к управляющему входу ячейки последующе й строки того же столбца.

ячейка четной строки дополнитель35

но содержит второй сумматор, элемент НЕ, коммутатор, причем первый и второй входы коммутатора соединены соответственно с выходами первого и 4Q второго сумматоров, вход управления коммутатора соединен с управляющими входом и выходом ячейки, а выход соединен с выходом суммы ячейки, первый вход которой подключен к рому входу первого сумматора, первому выходу ячейки и через элемент НЕ - к первому входу второго сумматора , второй вход которого соединен со вторым входом ячейки, вход и выход переноса второго сумматора соеди50нены соответственно с дополнитель ными входом и выходом переноса ячейки .

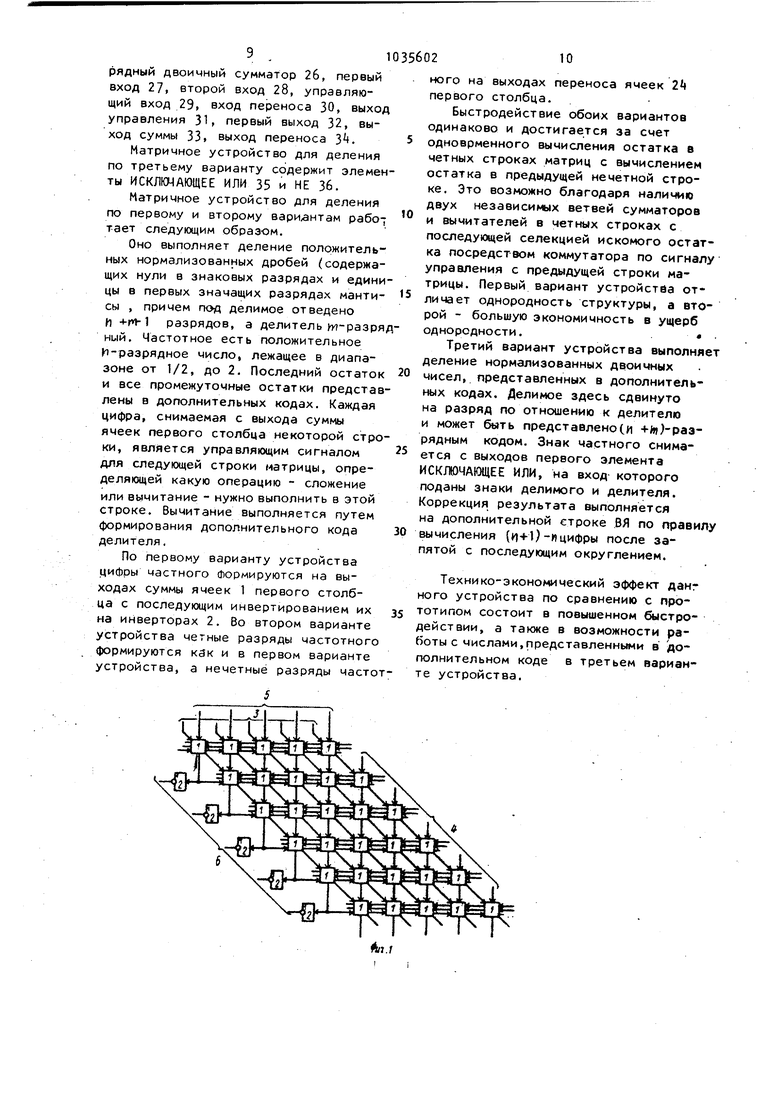

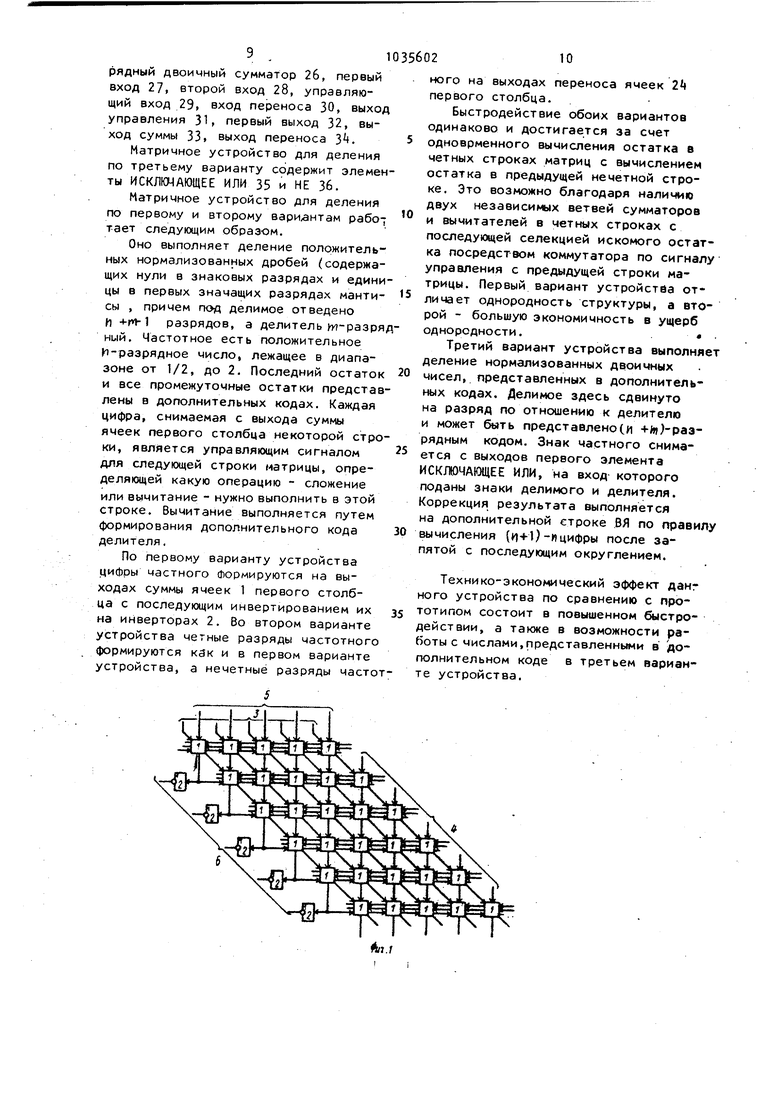

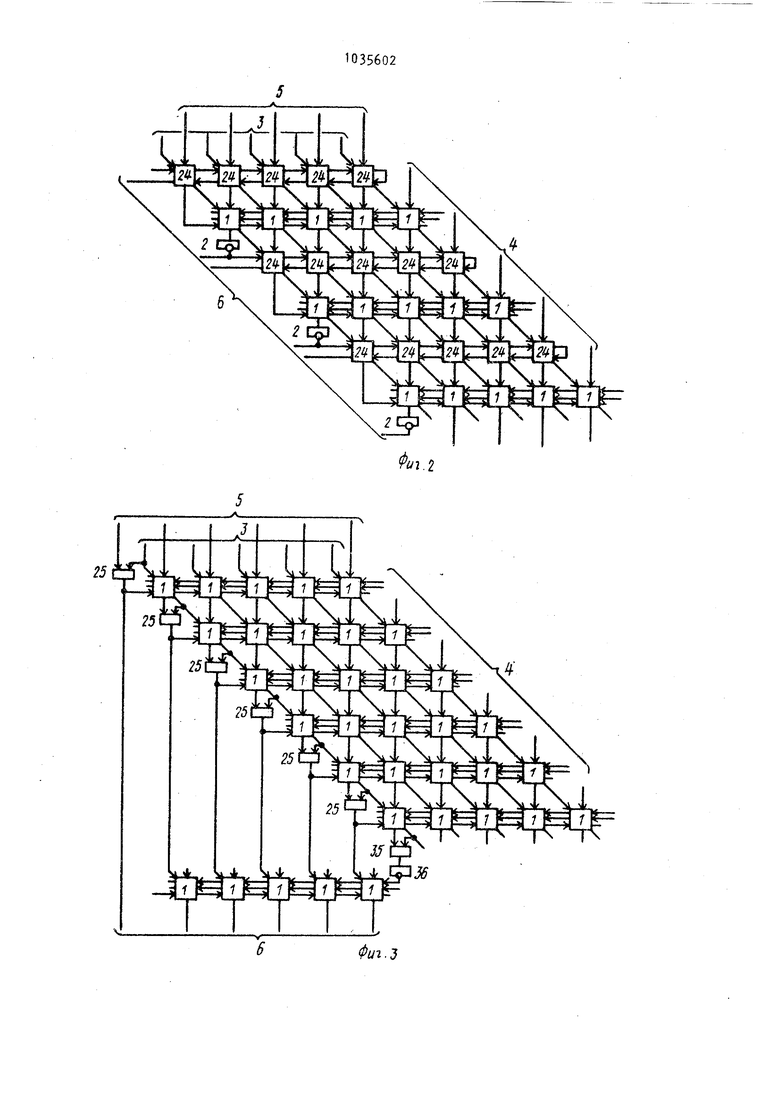

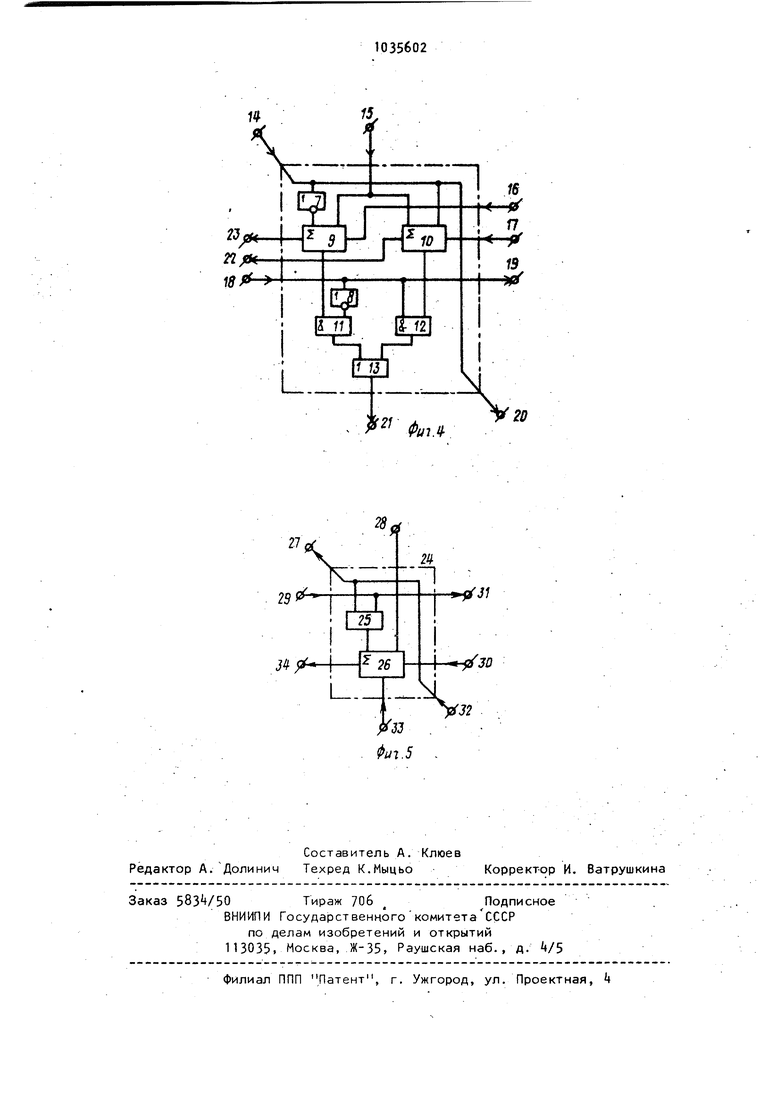

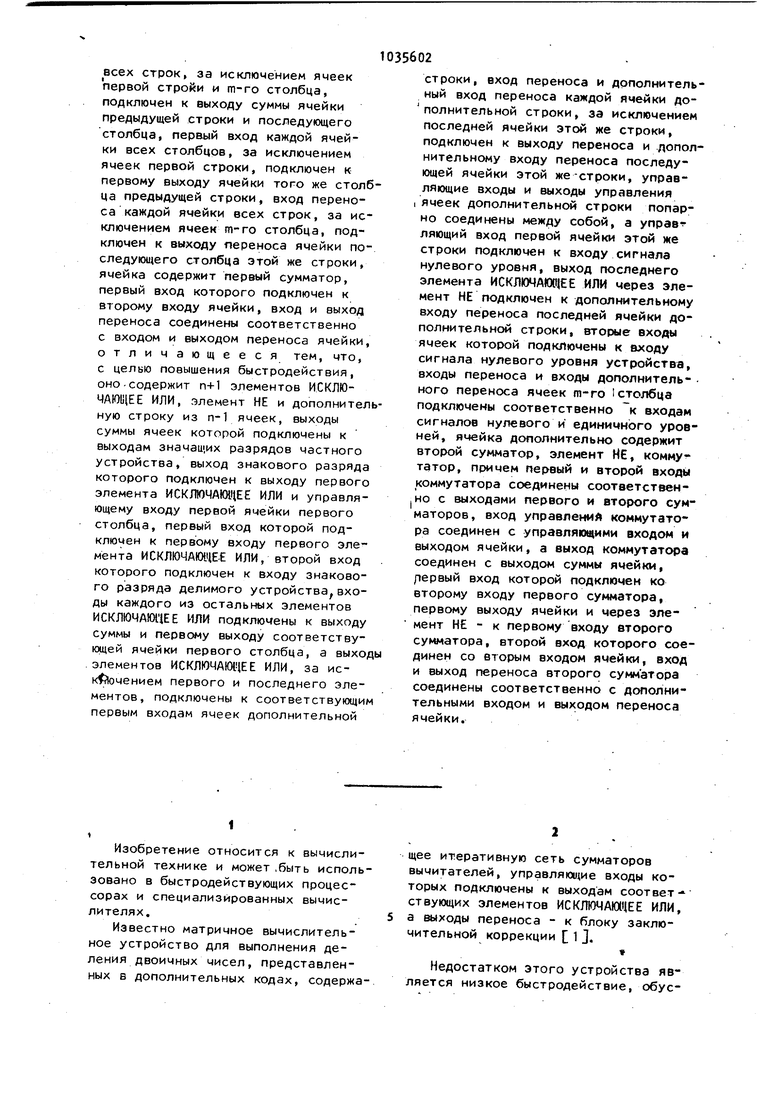

Кроме того, матричное устройство для деления, содержащее матрицу яче55ек из п строк и m столбцов, причем первые входы ячеек первой строки подключены к входам делителя устройства, а вторые входы ячеек первой строки и m-ro столбца - к входам значащих разрядов делимого устройства, управляющий вход ячеек каждой строки, за исключением ячеек первого столбца, noflkiiroMeH к,выходу управ ления ячейки предыдущего столбца той же строки, второй выход каждой ячейки всех строк, за исключением ячейки первой строки ищ-го столбца, подключен к выхйду суммы ячейки предыдущей строки и последующего столбцЪ, первый вход каждой ячейки всех столбцов, за исключением ячеек первой строки, подключен к первому выходу ячейки того же столбца предыдущей строки, вход Переноса каждой ячейки всех строк, за исключением ячейки tfi-столбца, подключен к выходу переноса ячейки последующего столбца этой же строки, ячейка содержит первый сумматор , первый вход которого подключен к второму входу ячейки, вход и выход переноса соедиг пены соответственно с входом и выходом переноса ячейки, дополнительно содержит и+ 1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, и дополнительную строку И- 1 ячеек, выходы суммы ячеек которой подключены к выхода значащих разрядов частного устройства, выход знакового разряда .которо го подключен к выходу первого элемен та ИСКЯЮЧАЩЕЕ ИЛИ и управляющему входу первой ячейки первого столбца, первый вход которой подключен к первому входу первого элемента ИСКЛЮЧАЮ ЩЕЕ ИЛИ, второй вход которого под..ключен к входу знакового разряда делимого устройства, входы каждого из остальных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходу суммы и первому выходу соответствующей ячейки первого столбца,а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, за исключением первого и последнего элементов, подключ ны к соответствующим первым входам ячеек дополнительной строки, выход переноса и дополнительный выход пере носа каждой ячейки дополнительной строки, за исключением последней ячейки этой же строки, подключен к выходу переноса и дополнительному входу переноса предыдущей ячейки этой же строки, управляющие входы и выходы управления ячейки дополнительной строки попарно соединены между собой, а управляющий вход первой ячейки этой же строки подключен к входу сигнала нулевого уров 028 ня, , выход последнего элемента 11СКЛЮЧАЮЩЕЕ ИЛИ через элемент НЕ подключен к дополнительному входу переноса последней ячейки дополнительной строки, вторые входы ячеек которой подключены к ВХОДУ сигнала нулевого уровня устройства, входы переноса и дополнительные входы переноса ячеек wf- столбца подключены соответственно к входам сигналов нулевого и единичного уровней, ячейка дополнительно содержит второй сумматор, элемент НЕ, коммутатор, причем первый и второй входы сумматора соединены соответственно с выходами первого и второго сумматоров, вход управления коммутатора соединен с управляющими входом и выходом ячейки, а выход коммутатора соединен с выходом суммы яц;ейки, первый вход которой подключен к второму входу первого сумматора, первому выходу ячейки и через элемент НЕ - к первому входу второго сумматора, второй вход которого соединен с вторым входом ячейки, вход и выход переноса второго сумматора соединены соответственно с дополнительными входом и выходом переноса ячейки. На фиг. 1 - 3 представлены структурные схемы вариантов матричного устройства для деления; на фиг. - функциональная схема ячейки, используемая в первом и третьем взриантах устройства, а также в четных строках второго варианта устройства, на фиг. 5 - то же, используемая для нечетных строк во втором варианте устройства. Матричное устройство для деления содержит ячейки 1, элементы НЕ 2, входы.делителя устройства 3, входы младших и старших разрядов делимого устройства k и S, выходы результата частотного устройства.6. Каждая ячейка содержит элементы НЕ 7 и 8, сумматор 9, сумматор 10, элементы И 11 и 12, элемент ИЛИ 13, первый вход 1, второй вход 15i дополнительный вход переноса 16, вход переноса 17, управляющий вход 18, выход управления 19, первый выход 20, выход суммы 21, выход переноса 22 и дополнительный выход переноса 23. Матричное устройство для деления по второму варианту содержит также ячейки 24, каждая из которых содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 25, однораз9 , рядный двоичный сумматор 26, первый вход 27, второй вход 28, управляющий вход 29, вход переноса 30, выход управления 31, первый выход 32, выход суммы 33 выход переноса З. Матричное устройство для деления по третьему варианту сс держит элемен ты ИСКЛЮЧАЮЩЕЕ ИЛИ 35 и НЕ 36. Матричное устройство для деления по первому и второму вариантам рабо тает следующим образом. Оно выполняет деление полржитель ных нормализованных дробей (содержащих нули в знаковых разрядах и едини цы в первых значащих разрядах мантисы , причем под делимое отведено И разрядов, а делитель -разря ный. Частотное есть положительное И-разрядное число, лежащее в диапазоне от 1/2, до 2. Последний остаток и все промежуточные остатки представ лены в дополнительных кодах. Каждая цифра, снимаемая с выхода суммы ячеек первого столбца некоторой стро ки, является управляющим сигналом для следующей строки матрицы, определяющей какую операцию - сложение или вычитание - нужно выполнить а этой строке. Вычитание выполняется путем формирования дополнительного кода делителя. По первому варианту устройства цифры частного Формируются на выходах суммы ячеек 1 первого столбца с последующим инвертированием их на инверторах 2. Во втором варианте устройства четные разряды частотного формируются как и в первом варианте устройства, а нечетные разряды часто 2 ного на выходах переноса ячеек Z первого столбца. Быстродействие обоих вариантов одинаково и достигается за счет одноврмеиного вычисления остатка в четных строках матриц с вычислением остатка в предыдущей нечетной строке. Это возможно благодаря наличию двух независимых ветвей сумматоров и вычитателей в четных строках с последующей селекцией искомого остатка посредством коммутатора по сигналу управления с предыдущей строки матрицы. Первый вариант устройства отличает однородность структуры, а второй - большую экономичность в ущерб однородности. Третий вариант устройства выполняет деление нормализованных двоичных чисел, представленных в дополнительных кодах. Делимое здесь сдвинуто на разряд по отношению к делителю и может быть представлено (и ч-й)}-раэрядным кодом. Знак частного снимается с выходов первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, на вход которого поданы знаки делимого и делителя. Коррекция результата выполняется на дополнительной строке ВЯ по правилу вычисления (H -U «цифры после запятой с последующим округлением. Технико-экономический эффект данг ного устройства по сравнению с прототипом состоит в повышенном быстродействии, а также в возможности работы с числами, представленными в дополнительном коде в третьем варианте устройства.

Н

2

gffL..

21

250

J«)2U-4

Ф,г

2Ц-9 J1

-fijD

t .. J

T

J2 .

Я Л

. .5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Рабинер Л | |||

| и др | |||

| Теория и применение цифровой обработки сигналов | |||

| М., Мир, 1978 | |||

| с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Карцев М.А., Брик В.Л | |||

| Вычислительные системы и синхронная арифметика | |||

| М., Радио и связь, 1981, с | |||

| Ручная тележка для грузов, превращаемая в сани | 1920 |

|

SU238A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| (прототип). | |||

Авторы

Даты

1983-08-15—Публикация

1981-12-05—Подача