агЛ

15П748

Изобретение относится к области иычислительной техники и предназначено для использования в быстродействующих вычислительных машинах раз- ,- ного назначения.

Целью изобретения является сокращение аппаратурных затрат,

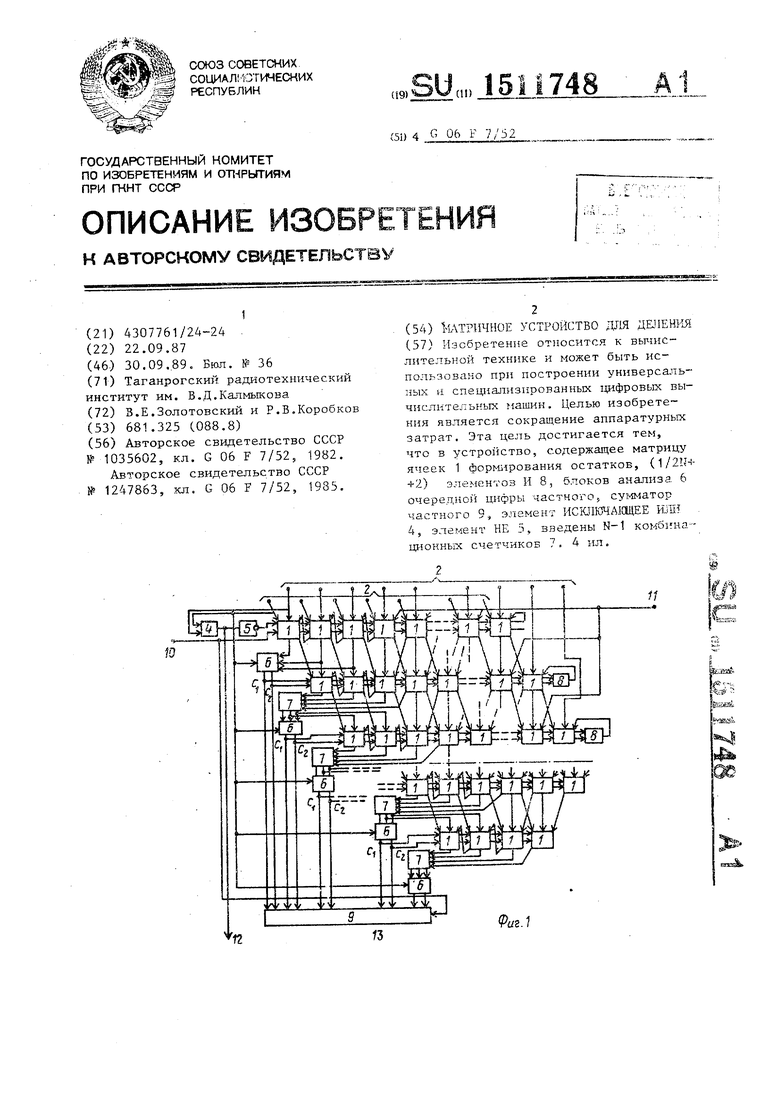

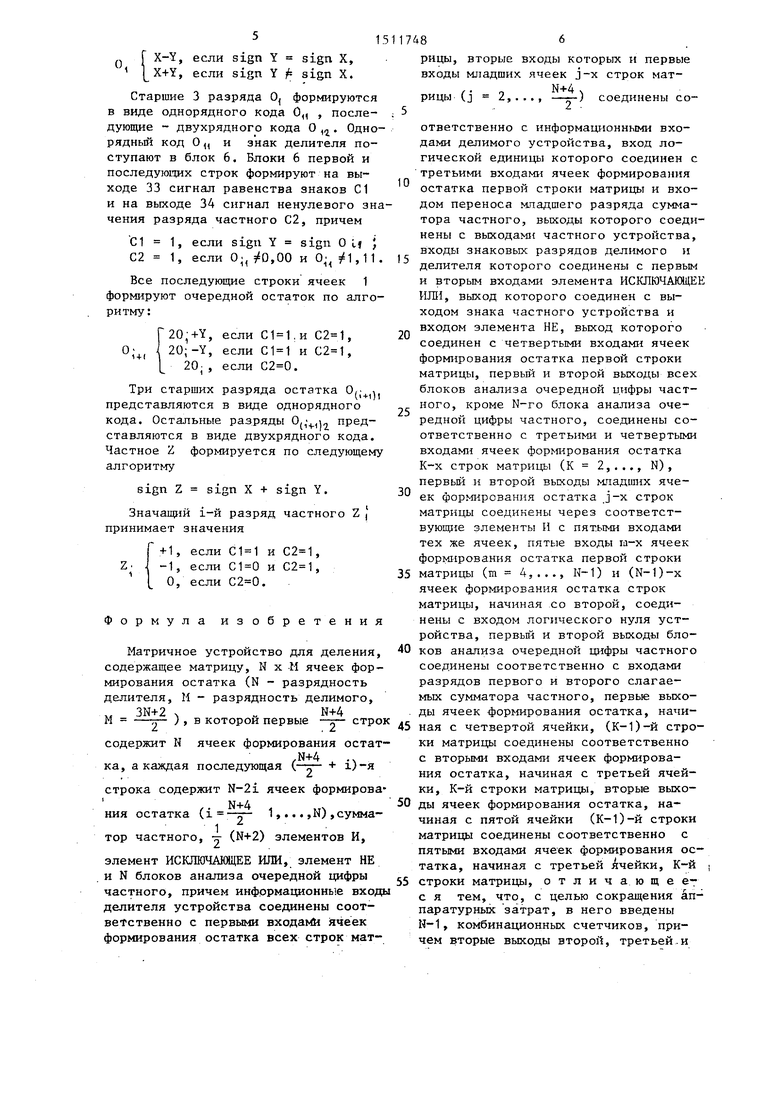

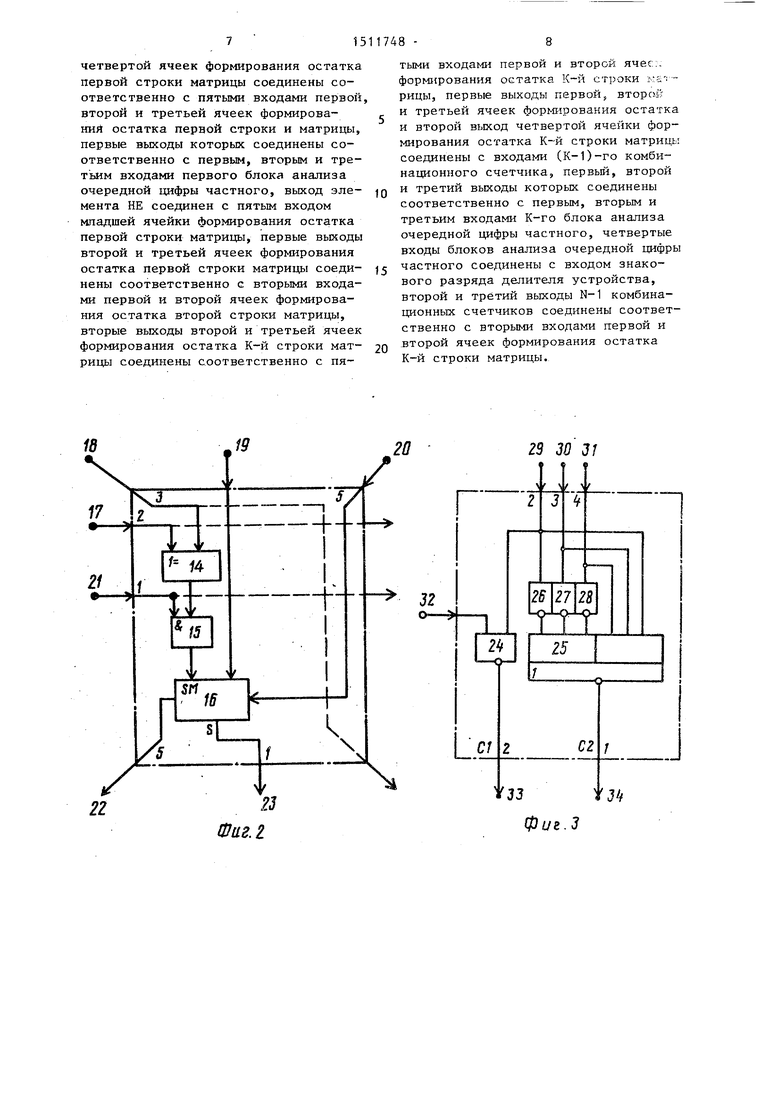

На фиг.1 приведена функциональная схема устройства; на фиг.2-4 - при- ю меры выполнения ячейки формирования остатка, блока анализа очередной цифры частного и комбинационного счетчика соответственно.

Матричное устройство для деле- 15 ния (фиг.1) содержит матрицу ячеек 1 формирования остатка, входы 2 делителя устройства, входы 3 делимого устройства, элемент ИСКЛЮЧАЩЕЕ НЛИ 4, элемент НЕ 5, блоки 6 анализа очеред-20 ной Щ1ФРЫ частного, комбинационные счетчики 7, элементы И 8, сумматор 9 частного, входы 1 10 и О 11 устройства, выходы знака частного 12 и частного 13 устройства. Ячейка формирования остатка (фиг.2) содержит элемент ИСЮШ ШОЦЕЕ 1-ШН 14, элемент И 15, сумматор 16, входы 17-21 ячеиделимого и делителя, В первой строке ячеек 1 формируется первьй остато 0|

X-Y, если sign X sign Y; X+Y если sign Y sign Y.

0,

Причем три старших разряда остатка формируются в однорядном коде, остальные - в двухрядном. Однорядный код остатка О, поступает на вход блока 6 анализа очередной цифры частного, KOTopbtft формирует сигналы С1 и С2, причем

С1 sign О, + sign Y;

С2 1, если однорядньш код О, не равен 1,11 или 0,00. Сигналы С1 и С2 управляют формированием остатка 0 во второй строке

20,+Y., если С, О, С 1,

0 20,-Y, если С 1, С 1,

20,

если С 0.

25

Три старших разряда остатка 0 также форг-шруются в однорядном коде, остальные в двухрядном.

Для формирования однорядного кода используются пятые входы первой и второй ячеек 1 и комбинационньй счетчик 7. Однорядный код из счетчика 7 Блок анализа очередной зщфры част- 30 поступает на вход блока 6 второй

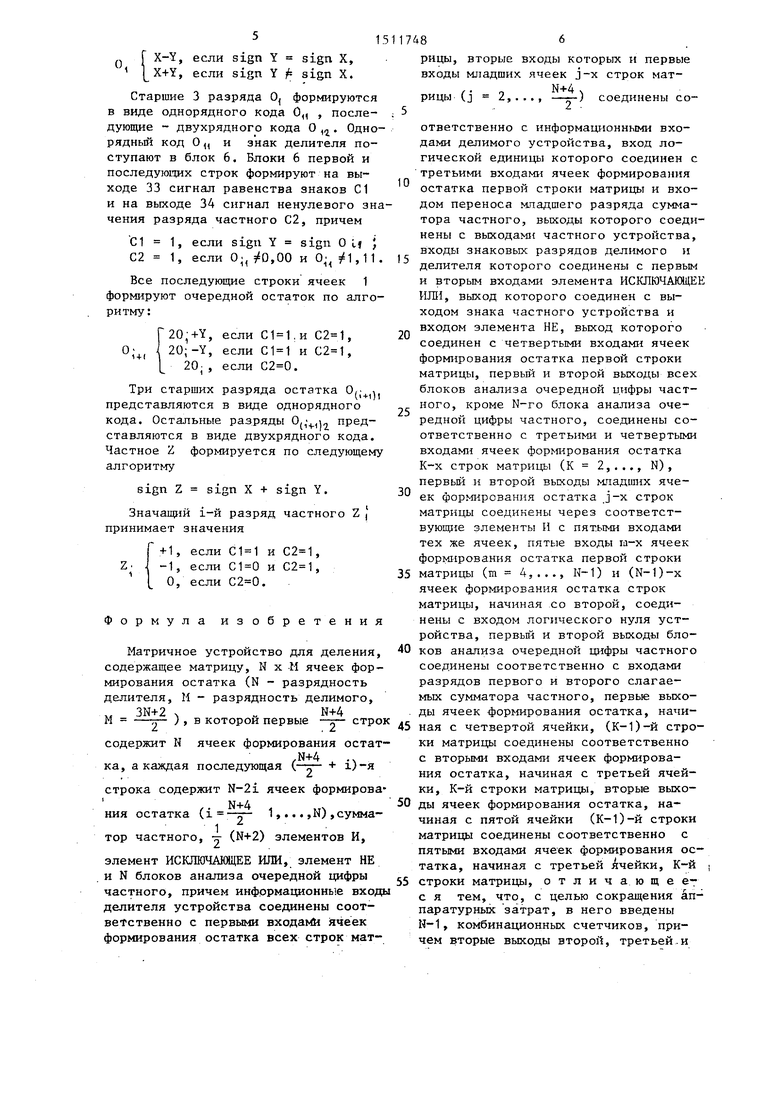

ного (фиг.З) содержит элемент 24 рав- строки, который формирует сигналы С1,

нозначности, элемент И-НЛИ-НЕ 25,

элементы НЕ 26-28, входы 29-32 блока,

выходы 33, 34 блока.

35

ки, выходы 22, 23 ячейки.

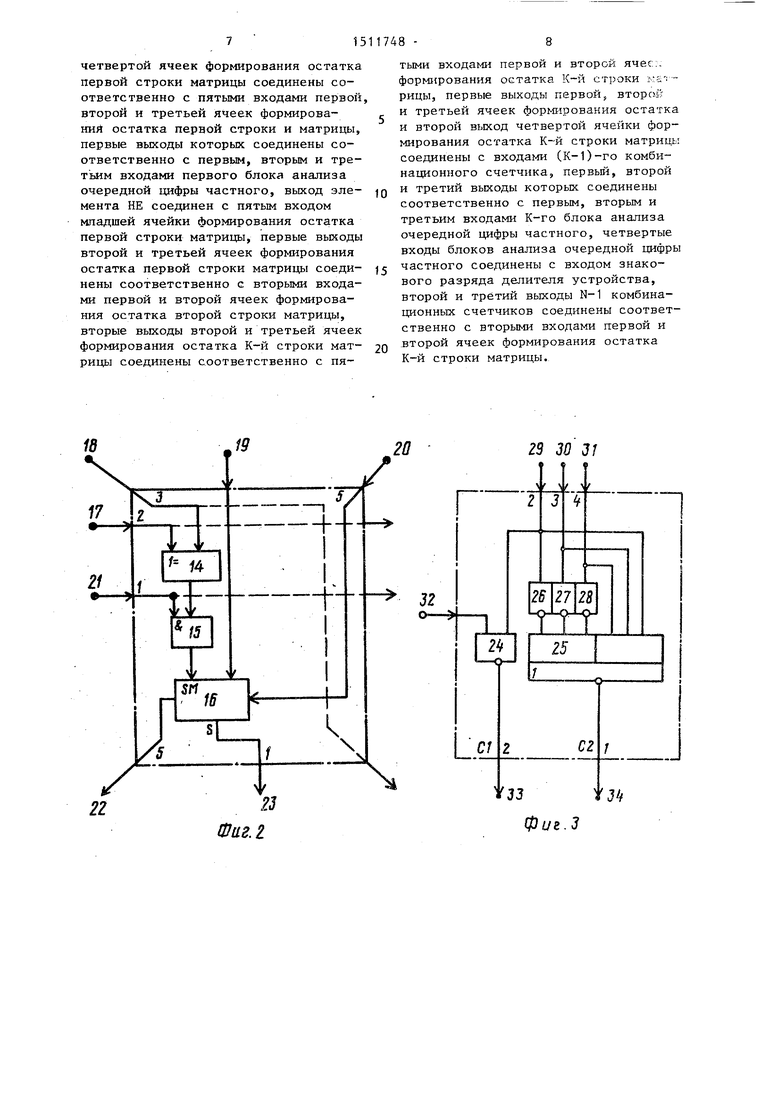

Комбинагт юнньй счетчик (фиг, 4) содержит элементы И 35, 36, элементы ИСКЛЮЧАЮЩЕЕ ШШ 37-39, входы 40-43 счетчика, выходы 44-46 счетчика.

Пусть разрядность делителя Y и частного Z равна N. Делимое X мо3N+2

40

жет иметь разрядность

ДальС2 для третьей строки. Аналогично устроены и последующие строки. Для обеспечения операции вычитания (посылки единицы в младший разряд разности) в младшей ячейке первой строки пятьш вход соединен с выходом элемента НЕ .5. Сигналы С1, С2, формируемые в блоках 6, поступают на сумматор 9 час тного. На вход 10 постепенно подается сигнал 1. На вход 11 постоянно Подается нулевой сигнал. С выхода 12 считывается знак частного, с выходов 13 - значаш;ие разряды.

нейшее увеличение разрядности X не сказывается на значении частного. Для формирования остатков используется матрица ячеек-1 формирования остатка. Hapaш вaниe укороченных строк до Ы ячеек не влияет на формирование частного, так как разряды остатков, формируемые в отброшенных ячейках, не принимают участия в формировании частного.

N-разрядный делитель поступает на входы 2 делителя в дополнительном коде. Делимое X также в дополнитель- ном коде поступает на входы 3. Ц элементе ИСКПЮЧЛ113ЩЕЕ ШШ 4 формируется знак частного. На выходе элемента НЕ 5 формируется сигнал равенства знаков

делимого и делителя, В первой строке ячеек 1 формируется первьй остато 0|

X-Y, если sign X sign Y; X+Y если sign Y sign Y.

0,

Причем три старших разряда остатка формируются в однорядном коде, остальные - в двухрядном. Однорядный код остатка О, поступает на вход блока 6 анализа очередной цифры частного, KOTopbtft формирует сигналы С1 и С2, причем

С1 sign О, + sign Y;

С2 1, если однорядньш код О, не равен 1,11 или 0,00. Сигналы С1 и С2 управляют формированием остатка 0 во второй строке

20,+Y., если С, О, С 1,

0 20,-Y, если С 1, С 1,

20,

если С 0.

5

0

5 С2 для третьей строки. Аналогично устроены и последующие строки. Для обеспечения операции вычитания (посылки единицы в младший разряд разности) в младшей ячейке первой строки пятьш вход соединен с выходом элемента НЕ .5. Сигналы С1, С2, формируемые в блоках 6, поступают на сумматор 9 час тного. На вход 10 постепенно подается сигнал 1. На вход 11 постоянно Подается нулевой сигнал. С выхода 12 считывается знак частного, с выходов 13 - значаш;ие разряды.

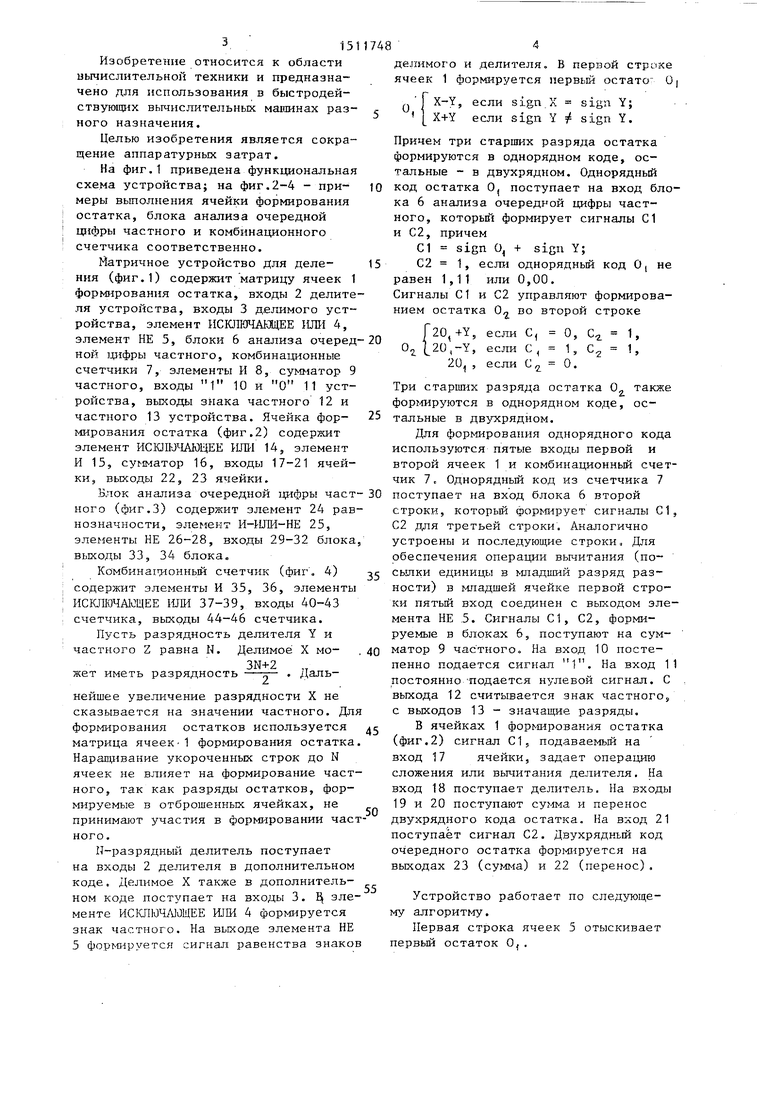

В ячейках 1 фop шpoвaния остатка (фиг.2) сигнал Cl, подаваемый на вход 17 ячейки, задает операцию сложения или вычитания делителя. На вход 18 поступает делитель. На входы 19 и 20 поступают и перенос двухрядного кода остатка. На вход 21 поступает сигнал С2. Двухрядный код очередного остатка фор№{руется на выходах 23 (сумма) и 22 (перенос).

Устройство работает по следующему алгоритму.

Первая строка ячеек 5 отыскивает первьй остаток О,,

15

.j Г X-Y, если sign Y sign X, , если sign Y sign X.

Старшие 3 разряда 0 формируются в виде однорядного кода О,, , после- дующие - двухрядного кода О ,. Одно- рядньй код О (, и знак делителя поступают в блок 6. Блоки 6 первой и последующих строк формируют на выходе 33 сигнал равенства знаков С1 и на выходе 34 сигнал ненулевого значения разряда частного С2, причем

С1 1, если sign Y sign О Ij J C2 1, если О;, ,00 и 0 1,11.

Все последующие строки ячеек 1 формируют очередной остаток по алгоритму:

0:

20,+Y, если .и , 20;-Y, если С 1 1 и ,

20-, если .

Три старших разряда остатка 0/-. представляются в виде однорядного кода. Остальные разряды представляются в виде двухрядного кода. Частное Z формируется по следующему алгоритму

sign Z sign X + sign Y.

Значащий i-й разряд частного Z I принимает значения

(+1, если С и , -1, если и , О, если .

Формула изобретения

Матричное устройство для деления, содержащее матрицу, N х -М ячеек формирования остатка (N - разрядность делителя, М - разрядность делимого,

м 3N+2 ч „ N+4

М -J- ) , в которой первые -г- строк

содержит N ячеек формирования остат,N+4 .. ка, а каждая последующая ( )я

строка содержит N-2i ячеек формироваN+4

НИН остатка (i 1

1,...,N),сумматор частного, -у (N+2) элементов И,

элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ и N блоков анализа очередной цифры частного, причем информационные входы делителя устройства соединены соответственно с первыми входами ячеек формирования остатка всех строк мат-

17486

рицы, вторые входы которых и первые входы младших ячеек j-x строк матN+4

рицы (J 2,. ..,

-)

соединены со0

5

5

5

0

0

ответственно с информационными входами делимого устройства, вход логической единицы которого соединен с третьими входами ячеек формирования остатка первой строки матрицы и входом переноса младшего разряда сумматора частного, выходы которого соединены с выходами частного устройства, входы знаковых разрядов делимого и делителя которого соединены с первым и вторым входами элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход которого соединен с выходом знака частного устройства и входом элемента НЕ, выход которого соединен с четвертыми входам ячеек формирования остатка первой строки матрицы, первьй и второй выходы всех блоков анализа очередной цифры частного, кроме N-ro блока анализа очередной цифры частного, соединены соответственно с третьими и четвертыми входаш ячеек фор шрования остатка К-х строк матрицы (К 2,,.., N), первый и второй выходы младших ячеек формирования остатка J-x строк матрицы соединены через соответствующие элементы И с пятыми входами тех же ячеек, пятые входы и-х ячеек формирования остатка первой строки

5 матрицы (т 4,..., N-1) и (N-l)-x ячеек формирования остатка строк матрицы, начиная со второй, соединены с входом логического нуля устройства, первый и второй выходы блоков анализа очередной цифры частного соединены соответственно с входами разрядов первого и второго слагаемых сумматора частного, первые выхо- . ды ячеек формирования остатка, начи5 ная с четвертой ячейки, (К-1)-й строки матрицы соединены соответственно с вторыми входами ячеек формирования остатка, начиная с третьей ячейки, К-й строки матрицы, вторые выхо0 ды ячеек формирования остатка, начиная с пятой ячейки (К-1)-й строки матрицы соединены соответственно с пятыми входами ячеек формирования остатка, начиная с третьей Ачейки, К-й строки матрицы, отличающе е- с я тем, что, с целью сокращения Аппаратурных затрат, в него введены Н-1, комбинационных счетчиков, причем вторые выходы второй, третьей,и

0

четвертой ячеек формирования остатка первой строки матрицы соединены соответственно с пятыми входами первой второй и третьей ячеек формирова- кий остатка первой строки и матрицы, первые выходы которых соединены соответственно с первым, вторым и третьим входами первого блока анализа очередной цифры частного, выход эле- мента НЕ соединен с пятым входом мпадшей ячейки формирования остатка первой строки матрицы, первые выходы второй и третьей ячеек формирования остатка первой строки матрицы соеди- нены соответственно с вторыми входами первой и второй ячеек формирования остатка второй строки матрицы, вторые выходы второй и третьей ячеек формирования остатка К-й строки мат- рицы соединены соответственно с пятыми входами первой и второй ячее;. формирования остатка К-й строки iv-a : - рицы, первые выходы первой второй и третьей ячеек формирования остатка и второй выход четвертой ячейки формирования остатка К-й строки матриць; соединены с входами (К-1)-го комбинационного счетчика, первьй, второй и третий выходы которых соединены соответственно с первым, вторым и третьим входами К-го блока анализа очередной цифры частного, четвертые входы блоков анализа очередной цифры частного соединены с входом знакового разряда делителя устройства, второй и третий выходы N-1 комбинационных счетчиков соединены соответственно с вторыми входами первой и второй ячеек формирования остатка К-й строки матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Устройство для деления | 1988 |

|

SU1681303A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении универсальных и специализированных цифровых вычислительных машин. Целью изобретения является сокращение аппаратурных затрат. Эта цель достигается тем, что в устройство, содержащее матрицу ячеек 1 формирования остатков, (1/2N+2) элементов И 8,N блоков анализа 6 очередной цифры частотного, сумматор частного 9, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, ЭЛЕМЕНТ НЕ 5, ВВЕДЕНЫ N - 1 КОМБИНАЦИОННЫХ СЧЕТЧИКОВ 7. 4 ИЛ.

WlLZ.l

п

Фиг.З

Фиг Л

| Матричное устройство для деления /его варианты/ | 1981 |

|

SU1035602A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-30—Публикация

1987-09-22—Подача