(54) УСТРОЙСТВО ДЛЯ ВЫБОРКИ МИКРОКОМАНД

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

| Устройство для контроля памяти | 1979 |

|

SU769641A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для восстановления работы процессора | 1977 |

|

SU696465A1 |

;

Изобретение отаЬсится к вычислитель-, ной технике и предназначено для использования в электронных цифровых вычислим тельных машинах (М),.

Известно устройство для выборки

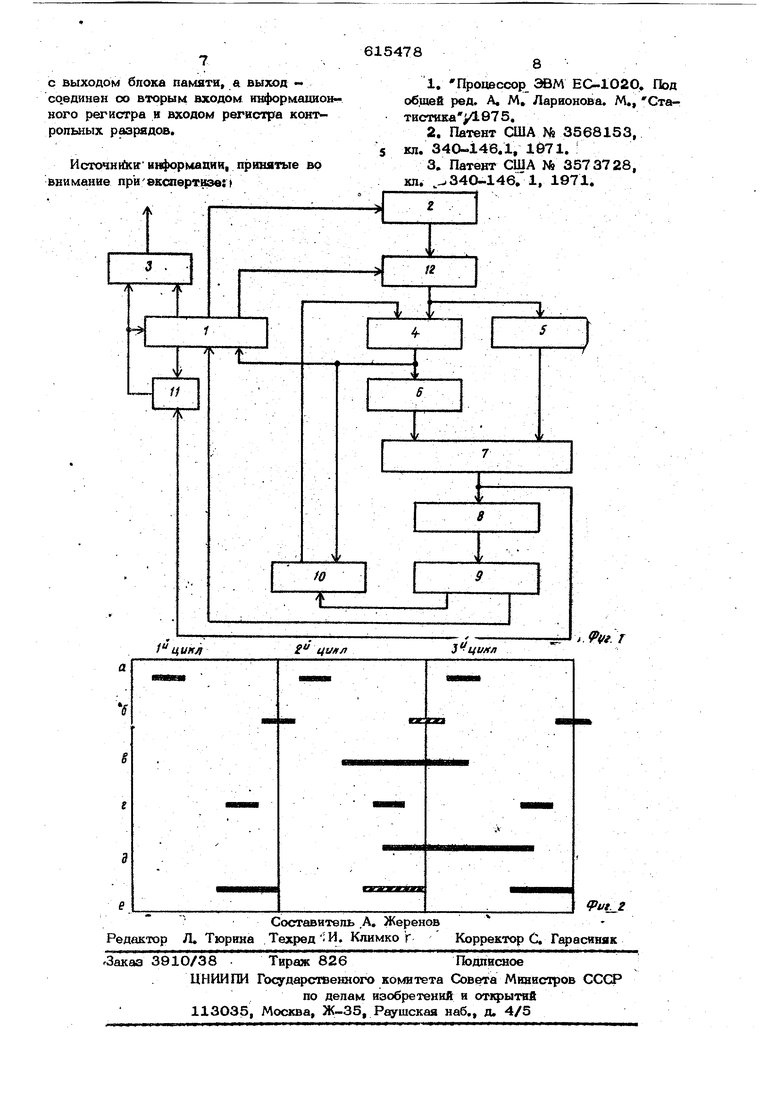

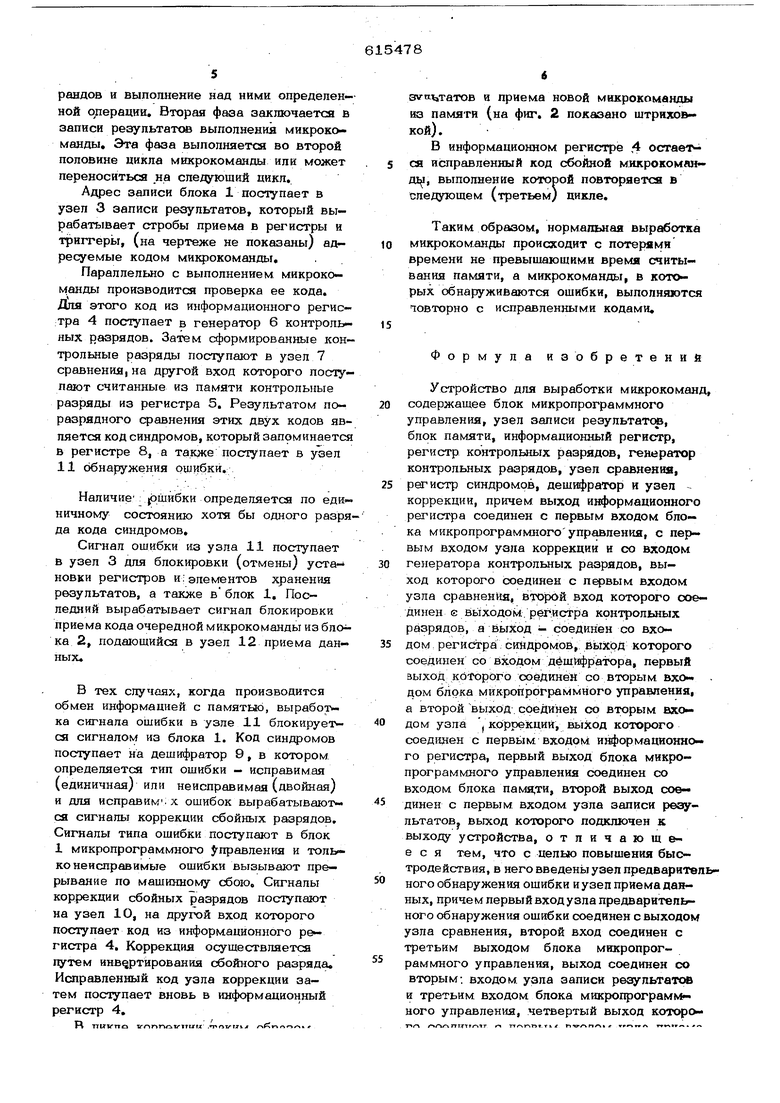

микрокоманд, входящее в состав ЭВМ, содержащее блок постоянной памяти, блок управления, блок локальной памяти, ияфор. мапионный регистр памяти и узел кон троля по четности l. Принцип действия устройства основан на считывании микрокоманд из управляюшей памяти с ио пользованием контроля считьтваемой ин- . формаций по четности. Это известное устройство характеризуртся невозмож ностью коррекции считываемой информации. Известно также устройство для выборки микрокоманд, содержащее Память, информационный регистр памяти, генератор контрольных, разрядов, узел сравнения, корректен, выходные вентили и выходной информационный регистр izj. Контроль информации в нем производит ся посредством корректирующего кода. Однако оно не имеет достаточного быст родействия. На известных устройств наиболее близким к изобретению по технической сушвости я&ляется устройство, содержащее блок микропрограммного управления, узел записи результатов, блок памяти, информационный регистр, регистр контрольных , генератор контрольных разрядов, узел сравнения, регистр синдромов, дещифратс и узел коррекции, гфичем выход информационн мго регистра соединен с первым входом блока микро; 1фограммнсяч управления, первым входом узла «.(рекияя и входом генератора контрольных разрядов, выход которого соеди нен с первым входом узла (равнения, второй вход которого соединен СХ выходом регистра контрольных разрядов, а выход соединен со входом регистра синдромов, выход которого соединен со входом дещи4 ратора, первый выход )го соединен со вторым входом блока микропрограмм ного у1фавления, а второй выход соединен со вторым входом узла коррекции, выход которого соединен с первым входом инфс)-« мационнся о регистра, первый выход бло- , ка микропрограммного управления соединен с входом блока памяти, второй выход соединен с первым входом уэла записи результатов, выход которого подклк чей к. выходу устройства (З. При считы вании иа памяти в информации может возникнуть ошибка, ддя обнаружения и коррекции которой требуется определенное время. Это время автоматически прибавляется ко времени считывания дан ных из памяти независимо от того, про.изошлаОшибка или нет. Информация, считанная из памяти, не используется для обработки до тех пор, пока не выпол нится цикл обнаружения и коррекции оши ки. Поскольку вероятность появления оши бок мала, постоянные затраты времени на обнаружение и коррекцию ошибок приводят к значительному снижению быстродействия. Целые изобретения является повышени быстродействия. В описываемом устройстве это достигается тем, что в него введены узел предварительного обнаружения ошибки и узел приема данных, причем первый вход узла предварительного обнаружения ошибки соединен с выходом узла сравнения, второй вход соединен с третьим выходЬм блока микропрограмм го управления, выход соединен со вторым входом узла записи результатов и третьим входом блока микропрограммн го управления, четвертый выход которого соединен с первым входом узлаприема данных, второй вход которого соединен с выходом блока памяти, а выход соединен со вторым входом информационного регистра и входом регистра контрольных разрядов, На .фиг, 1 представлена блок-схема описываемого устройства} на фиг, 2 - временная диаграмма : а - пути памяти} б - прием данных из памяти; в - сигнал ошибки; г - прием, скорректированныхданных; д - блокировка приема данных иа памяти; е - запись результатов. Устройство содержит блок 1 микропрограммного управления, блок 2 памяти узел 3 записи результатов, информационный регистр 4, регистр, 5 контрольных разрядов, генератор 6 контрольньзх разрядов, узел 7 сравнения, регистр 8 синдромов, дешифратор 9, узел 10 коррекции, узел 11 предварительного обна.руже ния ошибки и узел 12 приема данных. БЛОК 1 предназначен для выработки управляющих сигналов, необходимых для выполнения микрокоманд, поступаюших , из информационного .регистра 4, Генера-

J корректирующему (коду для информации, считываемой иа блока-2 памяти, который предывзначен для хранения микропрограмм, управляющих работой процессора. Узел 3 предназначен для выработки сигналов приема рв льтатов выполнения микрокомакаа в регистры или отдельные триггеры, адресуемые кодом микрокоманды, Информационнь1й регистр 4 предназначен для приема и хранения информации, считываемой из блока 2/и скорректированной информации ИЗузла 1О, Регистр 5 служит для приема и хранения контроль ных разрядов, считываемых из блока 2, Известными кодами, обладающими корректирующей способностыо являются коды Хэмминга, Наиболее целесообразным в описываемом устройстве является код, позволяющий исправлять одиночные и обнаруживать двойные ошибки. Узел 7 предназначен для сложения по модулю и контрольных разрядов из генератора 6 и контрольных разрядов, считываемых из блока 2, Результатом сложения являются синдромные биты. Регистр 8 служит для .звпоми.яания. синдромных битов, .образовйнньж в узле 7, Дешифратор 9 служит для дешифрации синдромныхбитов, запомненныхв регистре 8, указания типа ошибки и номера сбойного разряда данных в случае исправимой ошибки. Узел 1О предназначен для инвертирования сбойного разряда. Узел 11 предназначен для быстрой регистрации наличия ошибки в информации, считываемойИЗ блока 2, Узел 12 приема данных предназначен для передачи информации из блока 2 на вход информационного регистра 4. На временной диаграмме (см, фиг, 2) показаны три цикла работы устройства. Предполагается, что в первом цикле возникает исправимая ошибка при выборке кода микрокоманды, второй цикл - цикн коррекции ошибки, третий цикл являет- ся повторным для правильного выполнения сбойной микрокоманды, В начале каждого цикла блок 1 вырабатывает сигнал пуска блока 2 памяти. Считанный код поступает через узел 12 приема данных в информационный регистр 4 и регистр 5 контрол ных разрядов. Код из информационного регистра 4 поступает в блок, 1, который запоминает его и начинает обрабатывать микрокоманду, не ожидая проверки ее ко{ ректностн,. Выполнение микрокоманды можно разелить на две фазы, В первой фазе в наале цикла выполняется прием кода в реистр микрокоманд, декодирование отдель-

рандов и выполнение над ними опредепенной о/герацни. Вторая фаза заключается в записи результатов выполнения микрокоманды. Эта фаза выполняется во второй половине цикла микрокоманды или может переноситься на следующий цикл.

Адрес записи блока 1 поступает в узел 3 записи результатов, который вырабатывает стробы приема в регистры и триггеры, (на чертеже не показаны) адресуемые кодом микрокоманды.

Параллельно с выполнением микрокоманды производится проверка ее кода, Для этого код из информационного регистра 4 поступает в генератор 6 контроп1 ных разрядов. Затем сформированные кон трольные разряды поступают в узел 7 сравнения,на другой вход которого поступают считанные из памяти контрольные разряды из регистра 5, Результатом поразрядного сравнения этих двух кодов является код синдромов, который запоминается в регистре 8, а также поступает в узел 11 обнаружения .

Наличие (Ошибки определяется по единичному состоянию хотя бы одного разряда кода синдромов.

Сигнал ошибки из узла 11 поступает в узел 3 для блокировки (отмены) уста- новки регистров и:элементов хранения результатов, а также в блок 1, Последний вырабатывает сигнал блокировки приема кода очередной микрокоманды из бло ка 2, подающийся в узел 12 приема данных,

В тех случаях, когда производится обмен информацией с памятью, выработка сигнала ошибки в узле 11 блокируется сигналом из блока 1. Код синдромов поступает на дешифратор 9, в котором, определяется тип ошибки - исправимая (единичная) или неисправимая (двойная) и для исправим X ошибок вырабатываются сигналы коррекции сбойных разрядов. Сигналы типа ошибки поступают в блок 1 микропрограммного правления и только неисправимые ошибки вызывают прерывание по машинному сбою. Сигналы коррекции сбойных разрядов поступают на узел 10, на другой вход которого поступает код из информационного регистра 4, Коррекция осуществляется путем инвертирования сбойного разряда, Исправленный код узла коррекции затем поступает вновь в информационный регистр 4,

R TTWVTTd K-J r r ritrTTtjrW .n rtl/TTV j- r-n-4«-. 1

svntjTaTOB и приема новой микрокоманды №3 памяти (на фиг, 2 показано штриховкой).

В информационном регистре ,4 остает ся исправленный код сбойной мнкрокомяи- ды, выполнение которой повторяется в следующем (третьем) цикле.

Таким образом, нормальная выработка микрокоманды происходит с потеряк и времени не превышающими время считывания памяти, а микрокоманды, в которых обнаруживаются ошибки, выполняются 1овторно с исправленными кодами.

Формула изобретений

Устройство для выработки микрокоманд,

содержащее блок микропрограммного управления, узел записи результате, блок памяти, информационный регистр, регистр контрольных разрядов, генератор контрольных разрядов, узел сравнения,

регистр синдромов, дешифратор и узел коррекции, причем выход информационного регистра соединен с первым входом блока микропрограммногоуправления, с первым входом узла коррекции и со входом

генератора контрольных разрядов, выход которого соединен с входом узла сравнения, второй вход которого соединен е выходом, регистра контрольных разрядов, а выход - Соединен со входом регистра синдромов, выход которого соединен со входом дешифратора, первый выход которого соединён со вторым входом блока микропрограммного управления,

а второй выход. соединен со вторым входом узла | коррекции, выход которого

соед1гнен с первым входом )ормационно- го регистра, первый выход блока микропрограммного управления соединен со входом блока памя,ти, второй выход сое- динен с первым входом узла записи реаультатоВу выход которого подключен к выходу устройства, отличающееся тем, что с целью повышения быстродействия, в него введены узел предварительного обнаружения ошибки иузел приема данных, причем первый вход у зла предварительного обнаружения ошибки соединен с выходом узла сравнения, второй вход соединен с третьим выходом блока микропрограммного управления, выход соединен со вторым: входом узла записи результате и третьим входом блока микропрограммного управления, четвертый выход котороТ ГЛ i rv -vrrTTTTi-itT 1 ГТГч,.х l-i-w -xriJ f

с выходом блока памяти, а выход соединен со вторы ц входом информационного регистра и входом регистра конт ропьных раэрадов.

Источн1йс{г информадии, пршштые во внимание приекспертизе:)

1 цик

f цикл

«г

J z/fwr/

Авторы

Даты

1978-07-15—Публикация

1976-07-23—Подача