Изобретение относится к вычислительной технике и может быть применено в процессорах малой и средней производительности с реализованным режимом диагностики.

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения возможности использования оборудования в диагностическом режиме работы процессора.

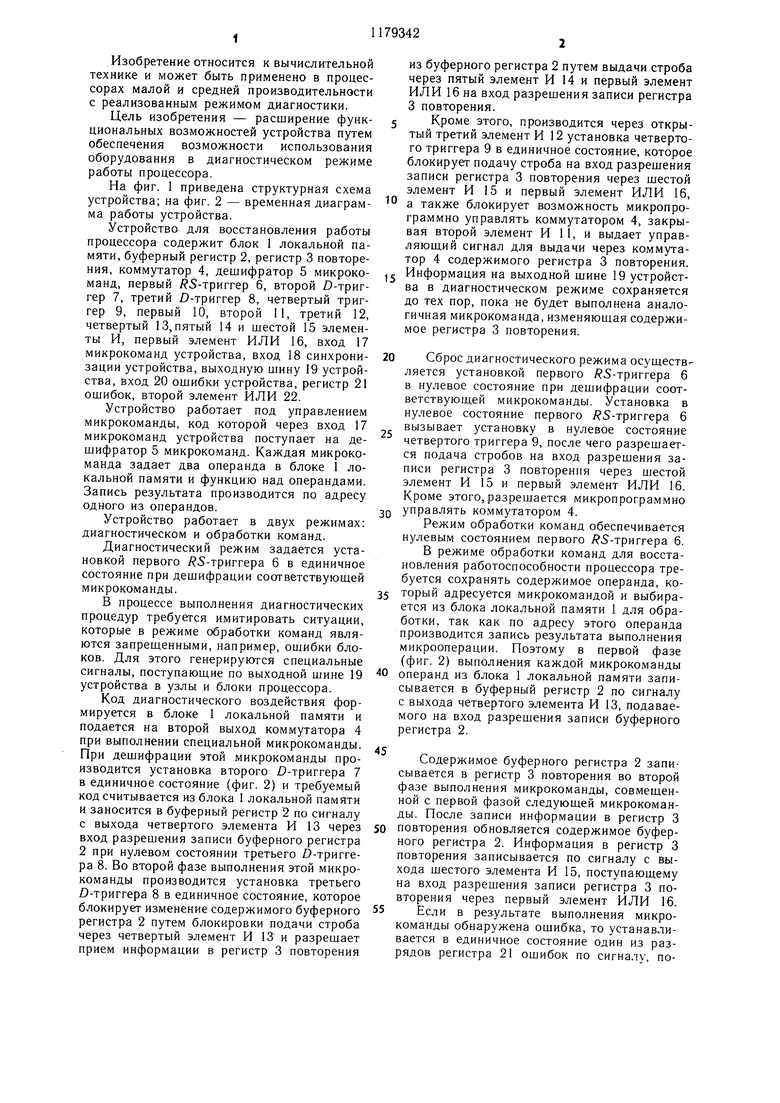

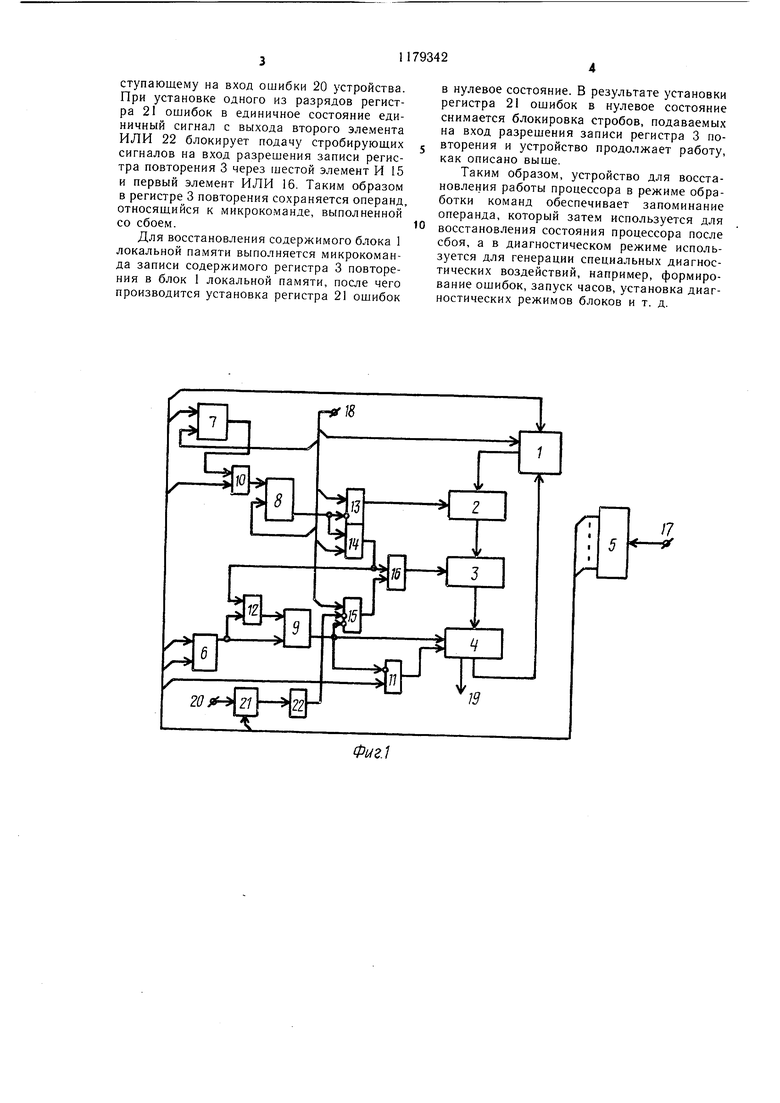

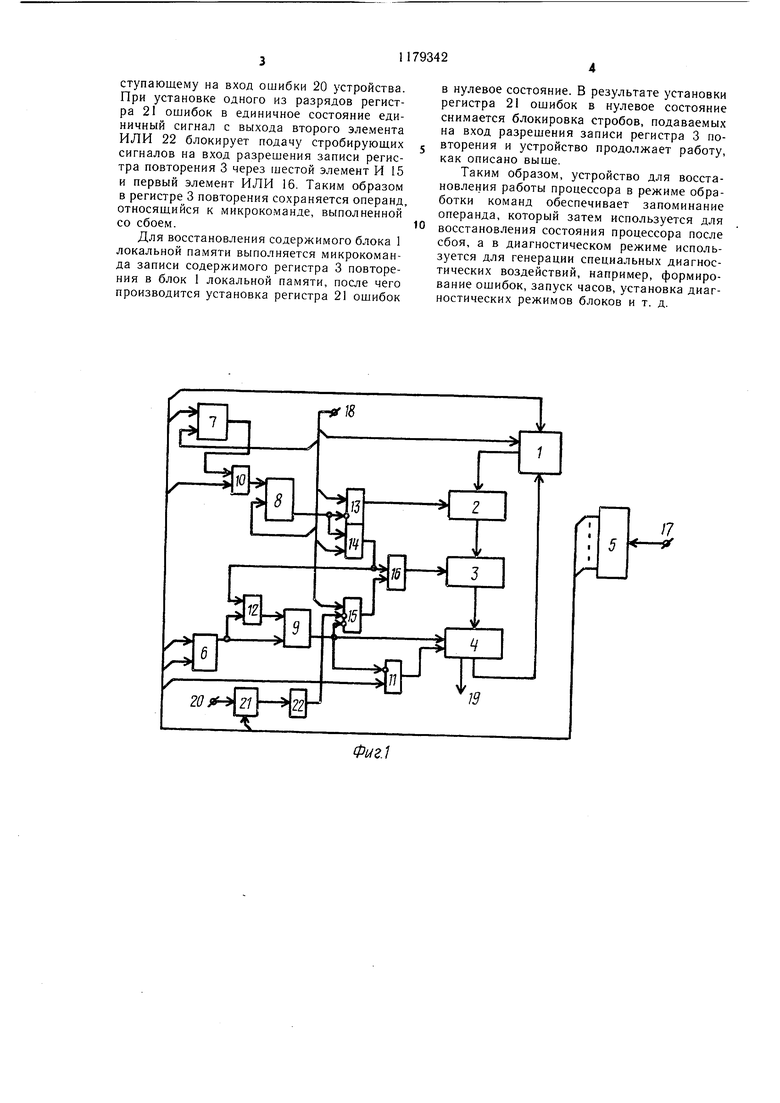

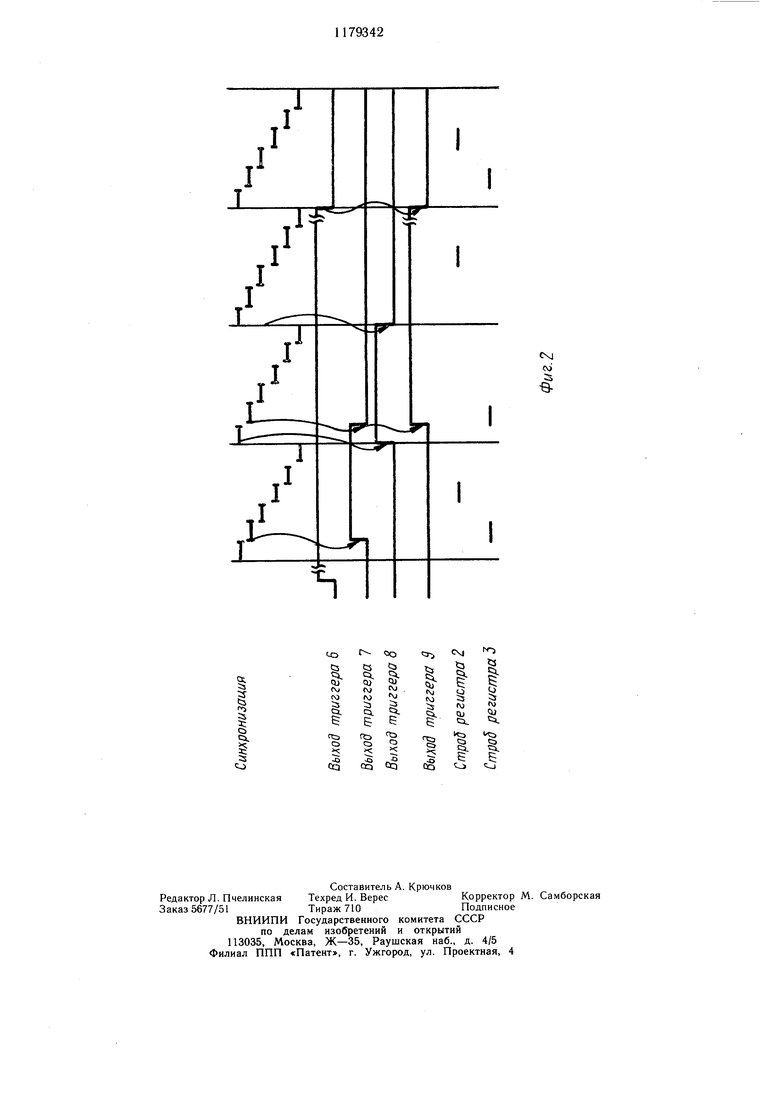

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временная диаграмма работы устройства.

Устройство для восстановления работы процессора содержит блок 1 локальной памяти, буферный регистр 2, регистр 3 повторения, коммутатор 4, дешифратор 5 микрокоманд, первый / 5-триггер 6, второй -триггер 7, третий / -триггер 8, четвертый триггер 9, первый 10, второй II, третий 12, четвертый 13, пятый 14 и шестой 15 элементы И, первый элемент ИЛИ 16, вход 17 микрокоманд устройства, вход 18 синхронизации устройства, выходную шину 19 устройства, вход 20 ошибки устройства, регистр 21 ошибок, второй элемент ИЛИ 22.

Устройство работает под управлением микрокоманды, код которой через вход 17 микрокоманд устройства поступает на дешифратор 5 микрокоманд. Каждая микрокоманда задает два операнда в блоке 1 локальной памяти и функцию над операндами. Запись результата производится по адресу одного из операндов.

Устройство работает в двух режимах: диагностическом и обработки команд.

Диагностический режим задается установкой первого У 5-триггера 6 в единичное состояние при дешифрации соответствующей микрокоманды.

В процессе выполнения диагностических процедур требуется имитировать ситуации, которые в режиме обработки команд являются запрещенными, например, ошибки блоков. Для этого генерируются специальные сигналы, поступаюшие по выходной шине 19 устройства в узлы и блоки процессора.

Код диагностического воздействия формируется в блоке 1 локальной памяти и подается на второй выход коммутатора 4 при выполнении специальной микрокоманды. При дешифрации этой микрокоманды производится установка второго / -триггера 7 в единичное состояние (фиг. 2) и требуемый код считывается из блока 1 локальной памяти и заносится в буферный регистр 2 по сигналу с выхода четвертого элемента И 13 через вход разрешения записи буферного регистра 2 при нулевом состоянии третьего /)-триггера 8. Во второй фазе выполнения этой микрокоманды производится установка третьего D-триггера 8 в единичное состояние, которое блокирует изменение содержимого буферного регистра 2 путем блокировки подачи строба через четвертый элемент И 13 и разрешает прием информации в регистр 3 повторения

из буферного регистра 2 путем выдачи строба через пятый элемент И 14 и первый элемент ИЛИ 16 на вход разрешения записи регистра 3 повторения.

5 Кроме этого, производится через открытый третий элемент И 12 установка четвертого триггера 9 в единичное состояние, которое блокирует подачу строба на вход разрешения записи регистра 3 повторения через шестой элемент И 15 и первый элемент ИЛИ 16,

0 а также блокирует возможность микропрограммно управлять коммутатором 4, закрывая второй элемент И 11, и выдает управляющий сигнал для выдачи через коммутатор 4 содержимого регистра 3 повторения.

г Информация на выходной шине 19 устройства в диагностическом режиме сохраняется до тех пор, пока не будет выполнена аналогичная микрокоманда, изменяющая содержимое регистра 3 повторения.

0 Сброс диагностического режима осуществляется установкой первого / 5-триггера 6 в нулевое состояние при дешифрации соответствующей микрокоманды. Установка в нулевое состояние первого 5-триггера 6 вызывает установку в нулевое состояние четвертого триггера 9, после чего разрешается подача стробов на вход разрешения записи регистра 3 повторения через шестой элемент И 15 и первый элемент ИЛИ 16. Кроме этого, разрешается микропрограммно

Q управлять коммутатором 4.

Режим обработки команд обеспечивается нулевым состоянием первого 5-триггера 6. В режиме обработки команд для восстановления работоспособности процессора требуется сохранять содержимое операнда, который адресуется микрокомандой и выбирается из блока локальной памяти 1 для обработки, так как по адресу этого операнда производится запись результата выполнения микрооперации. Поэтому в первой фазе (фиг. 2) выполнения каждой микрокоманды

операнд из блока 1 локальной памяти записывается в буферный регистр 2 по сигналу с выхода четвертого элемента И 13, подаваемого на вход разрешения записи буферного регистра 2.

Содержимое буферного регистра 2 записывается в регистр 3 повторения во второй фазе выполнения микрокоманды, совмещенной с первой фазой следующей микрокоманды. После записи информации в регистр 3

0 повторения обновляется содержимое буферного регистра 2. Информация в регистр 3 повторения записывается по сигналу с выхода шестого элемента И 15, поступающему на вход разрешения записи регистра 3 повторения через первый элемент ИЛИ 16.

5 Если в результате выполнения микрокоманды обнаружена ошибка, то устанавливается в единичное состояние один из разрядов регистра 21 ошибок по сигналу, поступающему на вход ошибки 20 устройства. При установке одного из разрядов регистра 21 ошибок в единичное состояние единичный сигнал с выхода второго элемента ИЛИ 22 блокирует подачу стробирующих сигналов на вход разрешения записи регистра повторения 3 через шестой элемент И 15 и первый элемент ИЛИ 16. Таким образом в регистре 3 повторения сохраняется операнд, относящийся к микрокоманде, выполненной со сбоем.

Для восстановления содержимого блока 1 локальной памяти выполняется микрокоманда записи содержимого регистра 3 повторения в блок 1 локальной памяти, после чего производится установка регистра 21 ошибок

в нулевое состояние. В результате установки регистра 21 ошибок в нулевое состояние снимается блокировка стробов, подаваемых на вход разрешения записи регистра 3 повторения и устройство продолжает работу, как описано выше.

Таким образом, устройство для восстановления работы процессора в режиме обработки команд обеспечивает запоминание операнда, который затем используется для восстановления состояния процессора после сбоя, а в диагностическом режиме используется для генерации специальных диагностических воздействий, например, формирование ошибок, запуск часов, установка диагностических режимов блоков и т. д.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для восстановления работы процессора | 1987 |

|

SU1476467A2 |

| Процессор | 1984 |

|

SU1246108A1 |

| Микропрограммный процессор с самодиагностикой | 1978 |

|

SU763902A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для восстановления работы процессора | 1977 |

|

SU696465A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1262516A1 |

УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ РАБОТЫ ПРОЦЕССОРА, содержащее блок локальной памяти, буферный регистр, регистр повторения, коммутатор, регистр ошибок, первый элемент ИЛИ и дешифратор микрокоманд, причем вход дешифратора микрокоманд соединен с входом микрокоманд устройства, соответствующие выходы дешифратора микрокоманд связаны с входами разрешения записи регистра ошибок и блока локальной памяти, выход, синхронизирующий вход и информационный вход которого соединены соответственно с информационным входом буферного регистра, входом синхронизации устройства и первым выходом коммутатора, информационный вход которого соединен с выходом регистра повторения, информационный вход которого связан с выходом буферного регистра, вход ошибки устройства соединен с информационным входом регистра ошибок, выход которого соединен с входом первого элемента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения возможности использования оборудования в диагностическом режиме работы процессора, в него введены второй элемент ИЛИ, четыре триггера и шесть элементов И, причем выходы соответствующих разрядов дешифратора микрокоманд соединены с первым входом первого элемента И, единичным и нулевым входами первого триггера, первым входом второго элемента И, )-входом второго триггера, С-вход и прямой выход которого связаны соответственно с входом синхронизации устройства и вторым входом второго элемента И, выход которого соединен с D-BXOдом третьего триггера, С-вход которого связан с входом синхронизации устройства, выход третьего триггера соединен с инверсным входом третьего элемента И и первым входом четвертого элемента И, второй вход которого соединен с входом синхронизации устройства, прямой вход и выход третьего элемента И Q соединены соответственно с входом синхроS низации устройства и входом разрешения записи буферного регистра, выход четвертого (Л элемента И соединен с первым входом второго элемента ИЛИ и первым входом пятого элемента И, второй вход и выход которого соединены соответственно с прямым выходом первого триггера и первым входом четвертого триггера, / -вход которого соединен с прямым выходом первого триггера, прямой выход четвертого триггера соединен с инверсным входом первого элемента И, первым управсо со ляющим входом коммутатора и первым инверсным входом шестого элемента И, второй ьо инверсный и третий прямой входы и выход которого соединены соответственно с выходом первого элемента ИЛИ, входом синхронизации устройства и вторым входом второго элемента ИЛИ, выход которого соединен с входом разрешения записи регистра повторения, выход первого элемента И соединен с вторым управляющим входом коммутатора, второй выход которого соединен с выходной шиной устройства.

«NJ

oJ

to

(v

ns

Ci

ci

CiСЭ

QJQj

JM

5e

rt(

оз

55

53

OQCQ

| Устройство для восстановления процессора после сбоя | 1979 |

|

SU857999A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для восстановления работы процессора | 1977 |

|

SU696465A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-01-09—Подача