(54) ОПЕРАЦИОННОЕ УСТРОЙСТВО ПРОЦЕССОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Процессор | 1977 |

|

SU691858A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Операционное устройство микропроцессорной вычислительной системы | 1982 |

|

SU1198532A1 |

| Устройство обработки информации с переменной длиной команд | 1990 |

|

SU1817099A1 |

| Арифметико-логическое устройство со встроенной диагностикой | 1984 |

|

SU1275426A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении процессоров .вычислительных машин.

Известно арифметико-логическое устройство, содержащее регистры, схему десятичного заполнителя, буфер перекоса, соединительный узел сумматора, схему сдвига вправо, сумматор, узел переноса, триггеры состояний переноса и десятичный корректор младших и старших знача,ш,их разрядов 1.

Наиболее близким по технической сущности к предлагаемому является процессор модели 50 системы 360 фирмы IBM, содержащий сумматор, регистры, блок регистров общего назначения, триггеры временного хранения, счетчики, схему однобайтовых логических операций, схему сдвига сумматора, группы входных и выходных вентилей, блок микроприказов, вход Y сумматора, вход XG сумматора и выход сумматора 2.

Недостаток известных устройств заключается в том, что они не позволяют реализовать (без выполнения сгандартных подпрограмм) присвоение первому операнду знака второго операнда или выделение модуля числа. Это ограничивает область применения устройств или снижает эффективность их применения, например, при управлении объектами в реальном масштабе времени.

Цель изобретения - повышение быстродействия устройства при выполнении операций присвоения знака и выделения модуля.

Поставленная цель достигается тем, что в операционное устройство процессора, содержащее арифметико-логи.ческий блок, блок регистров, селекторы первого и второго операндов, селектор результата и блок формирования микроприказов регистров, причем выход результата арифметико-логического блока соединен с информационным входом селектора результата, выход которого соединен с информационным входом блока регистров, управляющий вход которого соединен с выходом блока формирования микроприказов регистров, первый и второй информационные выходы блока регистров соединены соответственно с информационным входом селектора первого операнда и информационным входом селектора второго операнда, управляющие входы селекторов первого и второго операндов являются соответственно первым и вторым управляющими

входами устройства, выход селектора первого операнда и выход селектора второго операнда соединены соответственно с входами первого и второго операндов арифметикологического блока, вход подачи первого операнда и вход подачи второго операнда прямым кодом арифметико-логического блока являются соответственно третьим и четвертым управляющими входами устройства, эход подачи второго операнда обратным кодом и вход задания переноса в младший разряд арифметико-логического блока являются соответственно пятым и шестым-управляющими входами устройства, управляющий вход селектора результата является седьмым управляющим входом устройства, в блок формирования микроприказов регистров введены элемент сравнения, элемент НЕ, элемент И-ИЛИ, элемент И, элемент запрета, дещифратор,, группа элементов И, причем первый и второй входы элемента сравнения соединены соответственно с выходом селектора первого операнда и выходом селектора второго операнда, выход элемента сравнения соединен с первым входом элемента И-ИЛИ, второй вход которого соединен с выходом элемента НЕ, вход которого является входом строба устройства и соединен с третьим входом элемента ИИЛИ, четвертый вход которого соединен с его выходом, выход элемента И-ИЛИ соединен с первым входом элемента И, второй вход которого является входом признака команды присвоения знака устройства, выход элемента И соединен с первым входом элемента запрета, второй вход которого является входом такта записи устройства, выход элемента запрета соединен с первыми входами элементов И группы, вторые входы которых соединены с выходом дешифратора, вход которого является входом номера регистра устройства, выходы элементов И группы в совокупности являются выходом блока формирования микроприказов регистров.

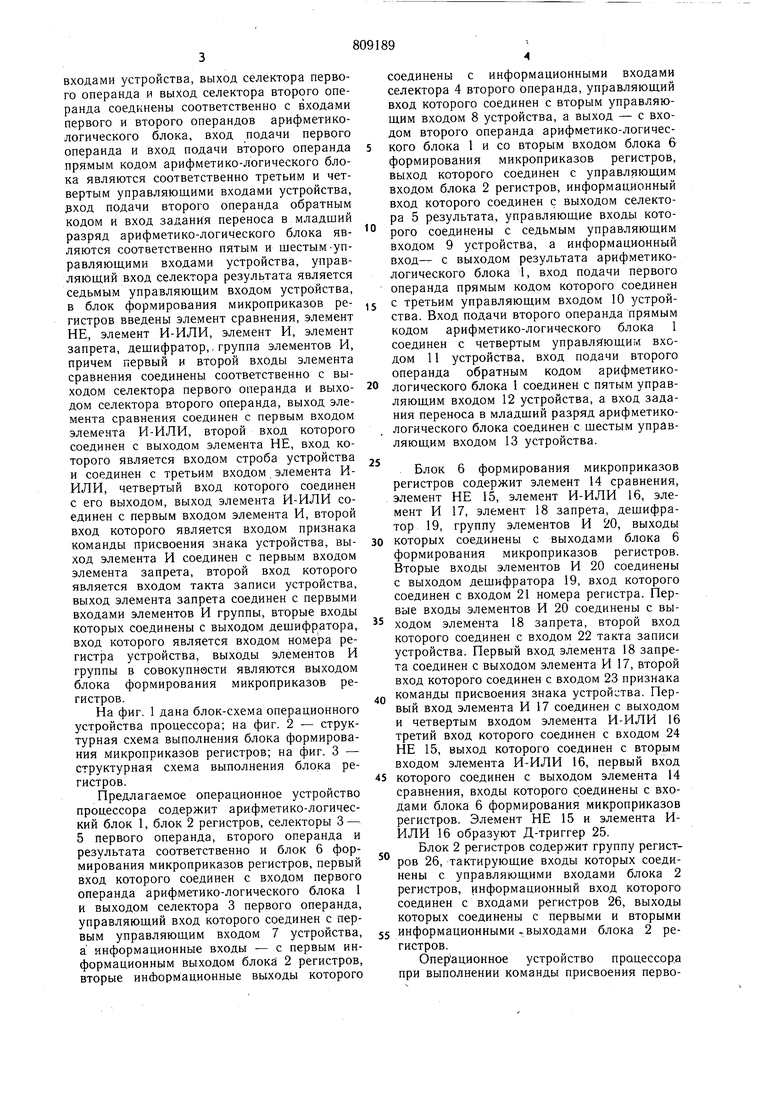

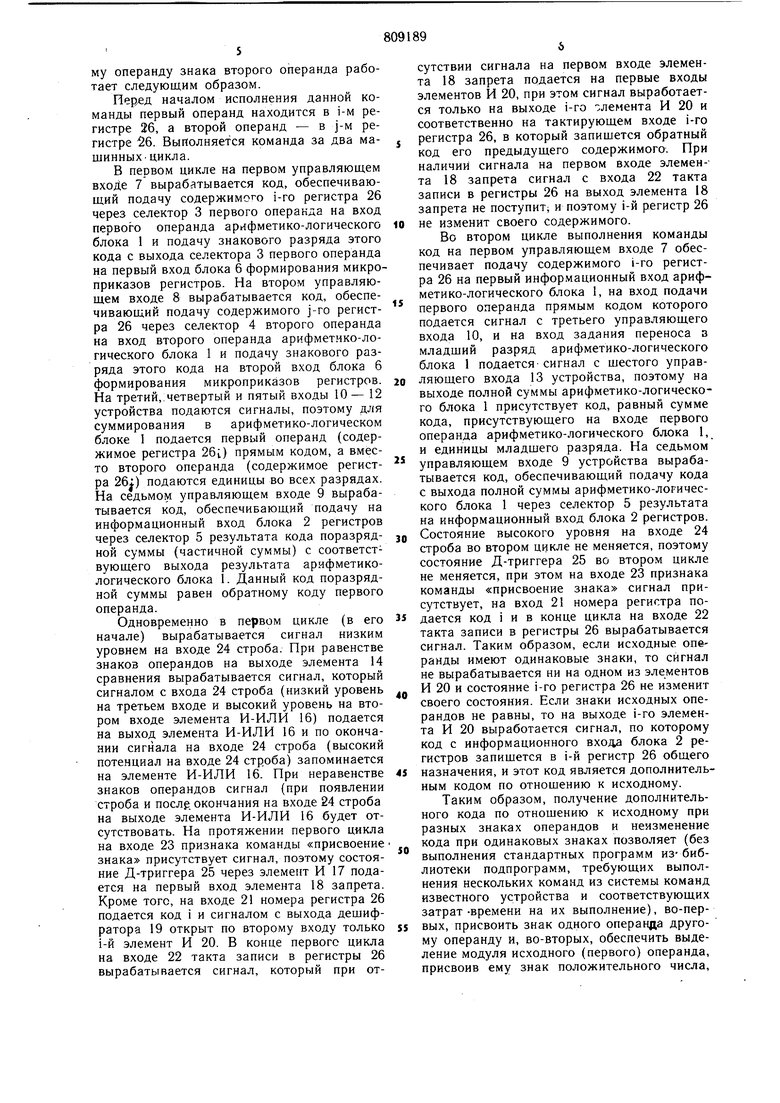

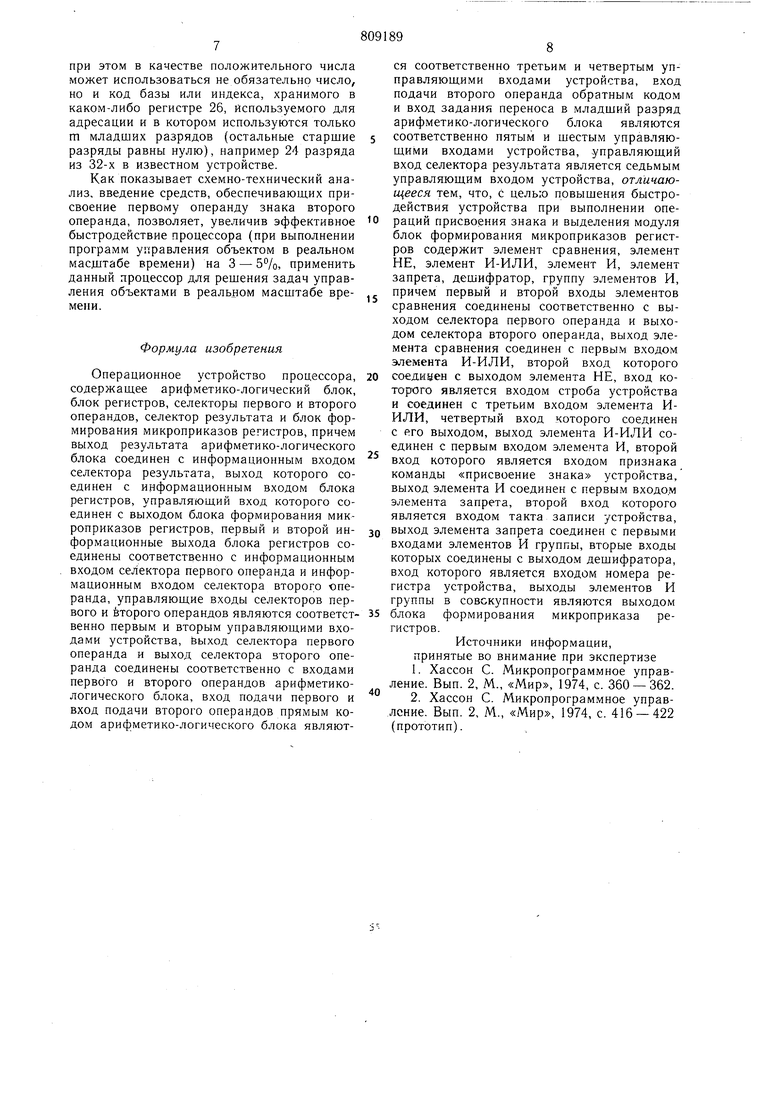

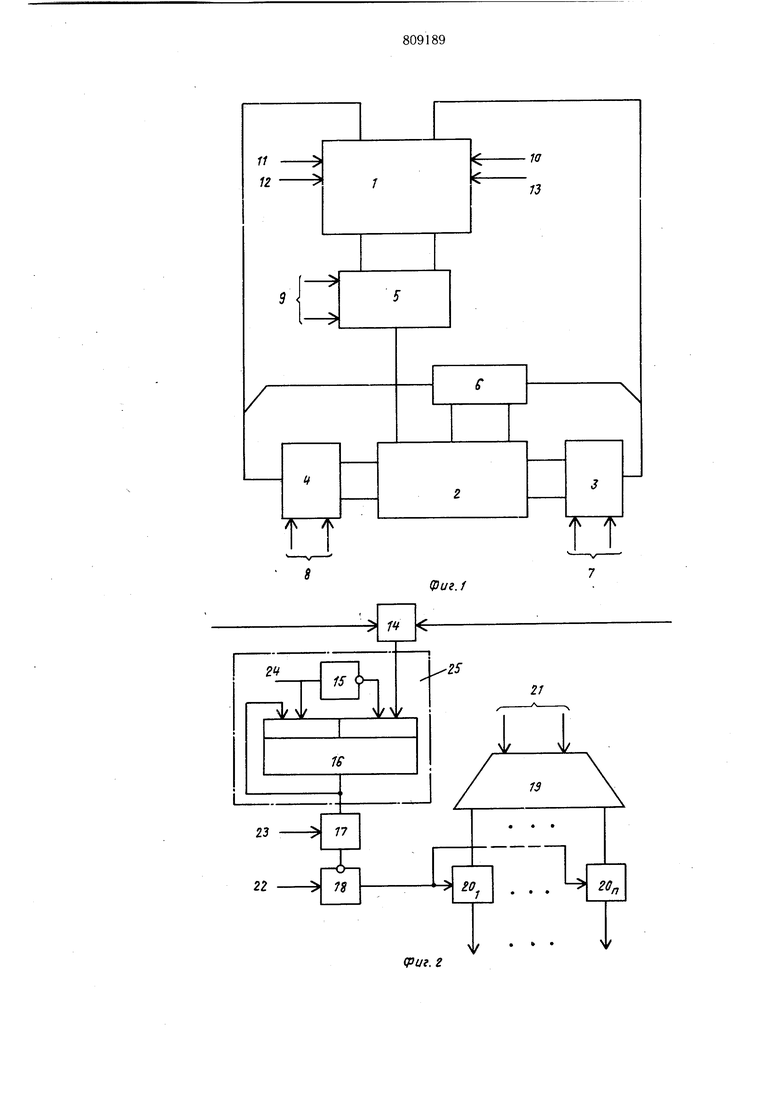

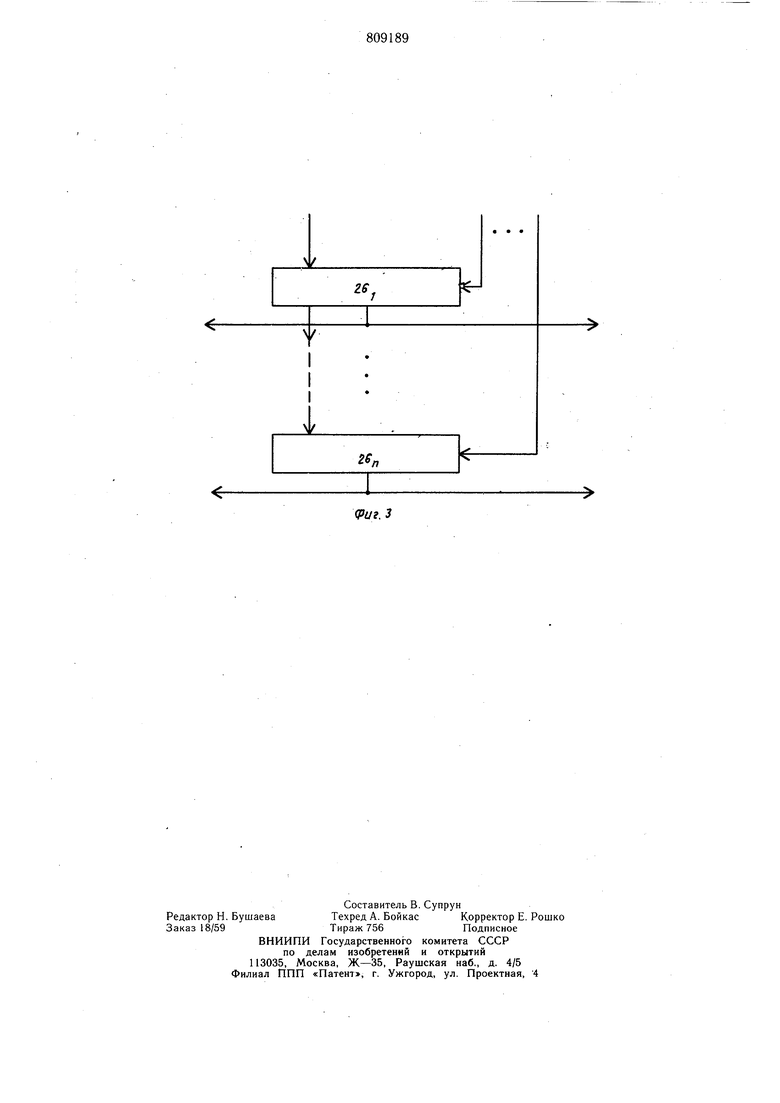

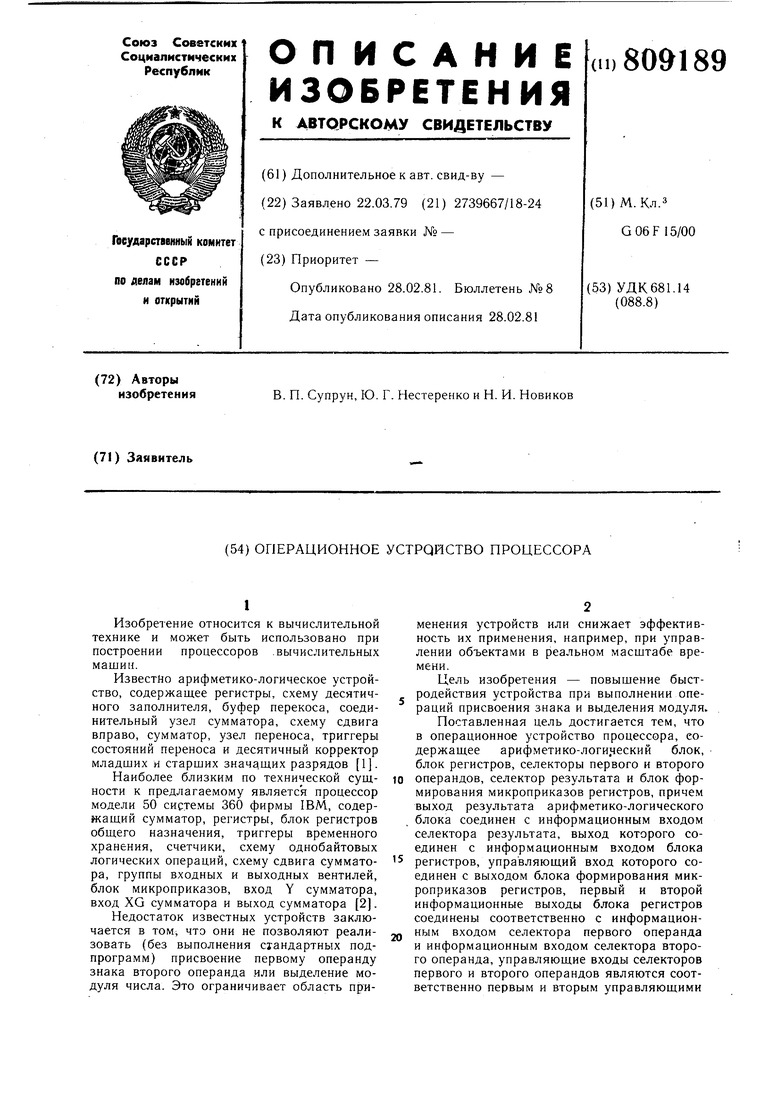

На фиг. 1 дана блок-схема операционного устройства процессора; на фиг. 2 - структурная схема выполнения блока формирования микроприказов регистров; на фиг. 3 - структурная схема выполнения блока регистров.

Предлагаемое операционное устройство процессора содержит арифметико-логический блок 1, блок 2 регистров, селекторы 3 - 5 первого операнда, второго операнда и результата соответственно и блок 6 формирования микроприказов регистров, первый вход которого соединен с входом первого операнда арифметико-логического блока 1 и выходом селектора 3 первого операнда, управляющий вход которого соединен с первым управляющим входом 7 устройства, а информационные входы - с первым информационным выходом блока 2 регистров, вторые информационные выходы которого

соединены с информационными входами селектора 4 второго операнда, управляющий вход которого соединен с вторым управляющим входом 8 устройства, а выход - с входом второго операнда арифметико-логического блока 1 и со вторым входом блока 6 формирования микроприказов регистров, выход которого соединен с управляющим входом блока 2 регистров, информационный вход которого соединен с выходом селектора 5 результата, управляющие входы которого соединены с седьмым управляющим входом 9 устройства, а информационный вход- с выходом результата арифметикологического блока 1, вход подачи первого операнда прямым кодом которого соединен

с третьим управляющим входом 10 устройства. Вход подачи второго операнда прямым кодом арифметико-логического блока 1 соединен с четвертым управляющим входом 11 устройства, вход подачи второго операнда обратным кодом арифметикологического блока 1 соединен с пятым управляющим входом 12 устройства, а вход задания переноса в младший разряд арифметикологического блока соединен с шестым управляющим входом 13 устройства.

Блок 6 формирования микроприказов регистров содержит элемент 14 сравнения, элемент НЕ 15, элемент И-ИЛИ 16, элемент И 17, элемент 18 запрета, дещифратор 19, группу элементов И 20, выходы

0 которых соединены с выходами блока 6 формирования микроприказов регистров. Вторые входы элементов И 20 соединены с выходом дешифратора 19, вход которого соединен с входом 21 номера регистра. Первые входы элементов И 20 соединены с вы ходом элемента 18 запрета, второй вход которого соединен с входом 22 такта записи устройства. Первый вход элемента 18 запрета соединен с выходом элемента И 17, второй вход которого соединен с входом 23 признака

Q команды присвоения знака устройства. Первый вход элемента И 17 соединен с выходом и четвертым входом элемента И-ИЛИ 16 третий вход которого соединен с входом 24 НЕ 15, выход которого соединен с вторым входом элемента И-ИЛИ 16, первый вход

5 которого соединен с выходом элемента 14 сравнения, входы которого соединены с входами блока 6 формирования микроприказов регистров. Элемент НЕ 15 и элемента ИИЛИ 16 образуют Д-триггер 25.

Блок 2 регистров содержит группу регистров 26, тактирующие входы которых соединены с управляющими входами блока 2 регистров, информационный вход которого соединен с входами регистров 26, выходы которых соединены с первыми и вторыми

5 информационными, выходами блока 2 регистров.

Операционное устройство процессора при выполнении команды присвоения первому операнду знака второго операнда работает следующим образом.

Перед началом исполнения данной команды первый операнд находится в i-м регистре 26, а второй операнд - в j-м регистре %. Выполняется команда за два машинных цикла.

В первом цикле на первом управляющем входе 7 вырабатывается код, обеспечивающий подачу содержимого i-ro регистра 26 через селектор 3 первого операнда на вход первого операнда арифметико-логического блока 1 и подачу знакового разряда этого кода с выхода селектора 3 первого операнда на первый вход блока 6 формирования микроприказов регистров. На втором управляющем входе 8 вырабатывается код, обеспечивающий подачу содержимого j-ro регистра 26 через селектор 4 второго операнда на вход второго операнда арифметико-логического блока 1 и подачу знакового разряда этого кода на второй вход блока 6 формирования микроприказов регистров. На третий,:четвертый и пятый входы 10- 12 устройства подаются сигналы, поэтому для суммирования в арифметико-логическом блоке 1 подается первый операнд (содержимое регистра 260 прямым кодом, а вместо второго операнда (содержимое регистра 26|) подаются единицы во всех разрядах. На седьмом управляющем входе 9 вырабатывается код, обеспечивающий подачу на информационный вход блока 2 регистров через селектор 5 результата кода поразрядной суммы (частичной суммы) с соответствующего выхода результата арифметикологического блока 1. Данный код поразрядной суммы равен обратному коду первого операнда.

Одновременно в первом цикле (в его начале) вырабатывается сигнал низким уровнем на входе 24 строба. При равенстве знаков операндов на выходе элемента 14 сравнения вырабатывается сигнал, который сигналом с входа 24 строба (низкий уровень на третьем входе и высокий уровень на втором входе элемента И-ИЛИ 16) подается на выход элемента И-ИЛИ 16 и по окончании сигнала на входе 24 строба (высокий потенциал на входе 24 строба) запоминается на элементе И-ИЛИ 16. При неравенстве знаков операндов сигнал (при появлении строба и послр. окончания на входе 24 строба на выходе элемента И-ИЛИ 16 будет отсутствовать. На протяжении первого цикла на входе 23 признака команды «присвоение знака присутствует сигнал, поэтому состояние Д-триггера 25 через элемент И 17 подается на первый вход элемента 18 запрета. Кроме того, на входе 2 номера регистра 26 подается код i и сигналом с выхода дешифратора 19 открыт по второму входу только i-й элемент И 20. В конце первого цикла на входе 22 такта записи в регистры 26 вырабатывается сигнал, который при OTсутствии сигнала на первом входе элемента 18 запрета подается на первые входы элементов И 20, при этом сигнал выработается только на выходе i-ro элемента И 20 и соответственно на тактирующем входе i-ro J регистра 26, в который запищется обратный код его предыдущего содержимого. При наличии сигнала на первом входе элемен-та 18 запрета сигнал с входа 22 такта записи в регистры 26 на выход элемента 18 запрета не поступит и поэтому i-й регистр 26

0 не изменит своего содержимого.

Во втором цикле выполнения команды код на первом управляющем входе 7 обеспечивает подачу содержимого i-ro регистра 26 на первый информационный вход арифметико-логического блока 1, на вход подачи

S первого операнда прямым кодом которого подается сигнал с третьего управляющего входа 10, и на вход задания переноса з младший разряд арифметико-логического блока 1 подается-сигнал с шестого управляющего входа 13 устройства, поэтому на выходе полной суммы арифметико-логического блока 1 присутствует код, равный сумме кода, присутствующего на входе первого операнда арифметико-логического блока 1, и единицы младшего разряда. На седьмом

управляющем входе 9 устройства вырабатывается код, обеспечивающий подачу кода с выхода полной суммы арифметико-логического блока 1 через селектор 5 результата на информационный вход блока 2 регистров.

0 Состояние высокого уровня на входе 24 строба во втором цикле не меняется, поэтому состояние Д-триггера 25 во втором цикле не меняется, при этом на входе 23 признака команды «присвоение знака сигнал присутствует, на вход 2 номера регистра подается код i и в конце цикла на входе 22 такта записи в регистры 26 вырабатывается сигнал. Таким образом, если исходные операнды имеют одинаковые знаки, то сигнал не вырабатывается ни на одном из элементов И 20 и состояние i-ro регистра 26 не изменит своего состояния. Если знаки исходных операндов не равны, то на выходе i-ro элемента И 20 выработается сигнал, по которому код с информационного входа блока 2 регистров запищется в i-й регистр 26 общего

5 назначения, и этот код является дополнительным кодом по отношению к исходному.

Таким образом, получение дополнительного кода по отношению к исходному при разных знаках операндов и неизменение кода при одинаковых знаках позволяет (без

0 выполнения стандартных программ из-библиотеки подпрограмм, требующих выполнения нескольких команд из системы команд известного устройства и соответствующих затрат-времени на их выполнение), во-первых, присвоить знак одного операнда другому операнду и, во-вторых, обеспечить выделение модуля исходного (первого) операнда, присвоив ему знак положительного числа. при этом в качестве положительного числа может использоваться не обязательно число, но и код базы или индекса, хранимого в каком-либо регистре 26, Используемого для адресации и в котором используются только m младших разрядов (остальные старшие разряды равны нулю), например 24 разряда из 32-х в известном устройстве. Как показывает схемно-технический анализ, введение средств, обеспечивающих присвоение первому операнду знака второго операнда, позволяет, увеличив эффективное быстродействие процессора (при выполнении программ управления объектом в реальном времени) на 3 - 5%, применить данный процессор для решения задач управления объектами в реальном масштабе времени. Формула изобретения Операционное устройство процессора, содержащее арифметико-логический блок, блок регистров, селекторы первого и второго операндов, селектор результата и блок формирования микроприказов регистров, причем выход результата арифметико-логического блока соединен с информационным входом селектора результата, выход которого соединен с информационным входом блока регистров, управляющий вход которого соединен с выходом блока формирования микроприказов регистров, первый и второй информационные выхода блока регистров соединены соответственно с информационным входом селектора первого операнда и информационным входом селектора второго операнда, управляющие входы селекторов первого и второго операндов являются соответственно первым и вторым управляющими входами устройства, ёыход селектора первого операнда и выход селектора второго операнда соединены соответственно с входами первого и второго операндов арифметикологического блока, вход подачи первого и вход подачи второго операндов прямым кодом арифметико-логического блока являют9ся соответственно третьим и четвертым упправляющими входами устройства, вход подачи второго операнда обратным кодом и вход задания переноса в младший разряд арифметико-логического блока являются соответственно пятым и шестым управляющими входами устройства, управляющий вход селектора результата является седьмым управляющим входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства при выполнении операций присвоения знака и выделения модуля блок формирования микроприказов регистров содержит элемент сравнения, элемент НЕ, элемент И-ИЛИ, элемент И, элемент запрета, дешифратор, группу элементов И, причем первый и второй входы элементов сравнения соединены соответственно с выходом селектора первого операнда и выходом селектора второго операнда, выход элемента сравнения соединен с первым входом элемента И-ИЛИ, второй вход которого соедиаен с выходом элемента НЕ, вход которого является входом строба устройства и соединен с третьим входом элемента ИИЛИ, четвертый вход которого соединен с его выходом, выход элемента И-ИЛИ соединен с первым входом элемента И, второй вход которого является входом признака команды «присвоение знака устройства, выход элемента И соединен с первым входом элемента запрета, второй вход которого является входом такта записи устройства, выход элемента запрета соединен с первыми входами элементов И группы, вторые входы которых соединены с выходом дешифратора, вход которого является входом номера регистра устройства, выходы элементов И группы в совокупности являются выходом блока формирования микроприказа регистров. Источники информации, принятые во внимание при экспертизе 1. Хассон С. Микропрограммное управление. Вып. 2, М., «Мир, 1974, с. 360 - 362. 2. Хассон С. Микропрограммное управление. Вып. 2, М., «Мир, 1974, с. 416 -422 (прототип).

П 12

10

13

Фиг./

2

15

пз/

f

rs2S

21

11

23

д;

22

12

. .

/

Авторы

Даты

1981-02-28—Публикация

1979-03-22—Подача