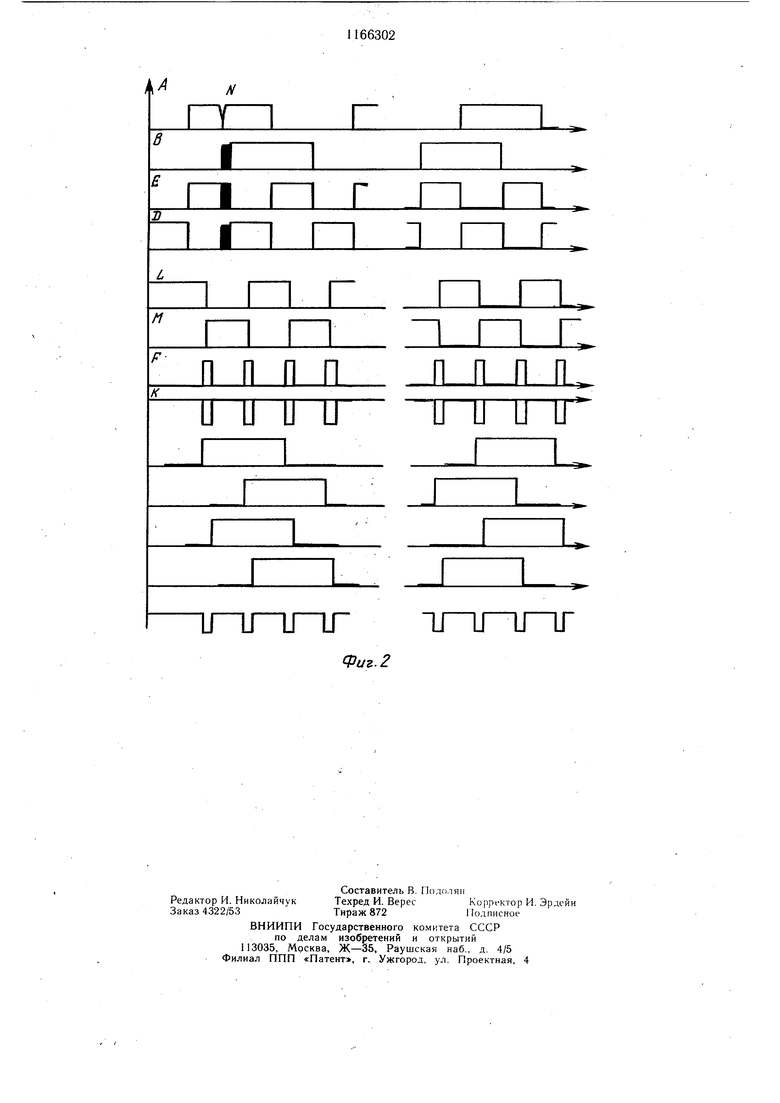

Изснбретение относится к автоматике и вычкс,;1ите;1ьной технике и предназначено для преобразования линейных или угловых перемещений в число импульсов, пропорциональное величине перемещения с учетом его направления. Целью изобретения является повышение помехоустойчивости устройства для дискретной обработки аналоговой информации. На фиг. 1 представлена блок-схема устройства для дискретной обработки аналоговой информации перемещения в код; на фиг. 2 - временные диаграммы работы устройства. Устройство содержит формирователи 1 и 2 логических уровней, блок 3 памяти текущего состояния, блок 4 памяти предыдущего состояния, дешифратор 5, блок 6 формирования синхроимпульсов, элемент ИСКЛЮЧАЮЩЕЕ .ИЛИ 7, инвертор 8, элементы И - liE 9 и 10, формирователь 11 импульсов, триггер, 12 и инвертор 13. Устройство работает следующим образом. При перемещени кодовой шкалы на выходах формирователей 1 и 2 возникают две последовательности импульсов, сдвинутые одна относительно другой на четверть периода, причем частота следования импульсов прямо пропорциональна скорости перемещения шкалы. При движении шкалы в одном направлении на выходе формирователей возникают состояния 00, 10, 11, 01, при смене направления движения 00,01,11,10. Анализируя одновременно текущее и предыдущее состояния, можно определить направление перемещения шкалы. Для запоминания состояния предназначены блоки 3 и 4 памяти. Анализ состояний осуществляется с помощью дешифратора 5, который выдает импульсы на суммирующий ( + ) или вычитающий (-) входы реверсивного счетчика (не показан) при соответствующих перемещениях кодовой шкалы. Таким образом, состояние реверсивного счетчика пропорционально величине перемещения шкалы относительно точки отсчета. Блок 6 служит для формирования синхроимпульсов, которые вырабатываются при каждой смене состояний на выходах формирователей 1 и 2, причем для повышения помехоустойчивости синхроимпульсы формируются только после окончания формирования на выходах формирователей логического уровня. Принцип действия схемы формирования импульсов занесения поясняется с помощью временной .диаграммы (фит. 2), где слева показана диаграмма состояний при работе преобразователя в режиме сложения, а справа - в режиме вычитания. На входы блока 6 формирования синхроимпульсов подаются обе последовательности сигналов с выходов формирователей 1 и 2, которые суммируются элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 7. На выходе элемента 7 логический уровень изменяется при любом изменении состояния на выходах формирователей 1 и 2 (диаграмма Е, фиг. 2). При этом вблоках 3 и 4 памяти должны фиксироваться только те изменения состояния, которые остаются стабильными в течение некоторого промежутка времени t«3- Всякое изменение состояния длительностью (f4 воспринимается как помеха и не вызывает формирование синхроимпульса. Для этой цели в схеме используется формирователь 1 1 импульсов, который соединяется с выходами двух элементов-И- НЕ 9 и 10 с открытыми коллекторами. Длительность интервала twj задается формирователем 11. Висходном состоянии на оба входа одного из элементов И-НЕ поступают уровни логической «1, другого -уровни логического «О. В случае изменения состояний на выходах формирователей 1 и 2 логические уровни на входах D и С элементов И-НЕ 9 и 10 изменяются на противоположные, т. е. оба элемента И-НЕ 9 и 10 имеют на выходе высокий логический уровень. Если изменение состояния остается устойчивым в течение времени tos, то на выходе формирователя 11 импульсов появ-ляется передний фронт синхроимпульса. В противном случае (,j) один из элементов И-НЕ переходит в состояние с низким логическим уровнем на выходе до того, как срабатывает формирователь 11 импульсов. Передний фронт синхроимпульса поступает на синхровход триггера 12 и изменяет его состояния на выходах на противоположные. При этом уровень логической «1 подается на оба входа элемента И-НЕ 10, на выходе которого устанавливается сигнал логического «О. Формирователь 11 вырабатывает задний фронт синхроимпульса. Таким образом, длительность импульса занесения определяется суммарным временем задержки срабатывания элементов 12, 10 и 11 и временем формирования импульсов формирователем 11 (диаграмма Е, фиг. 2). Занесение в блок 3 памяти текущего состояния осуществляется по переднему фронту синхроимпульса,.вырабатываемого формирователем 11, запись в блок 4 памяти предыдущего состояния происходит но заднему фронту этого же импульса, который с помощью инвертора 13 преобразуется в передний фронт инверсного импульса (диаграмма К).

А

N

б

1

Е F

ГП 1

JL

гп г

тг

п п п п

FUnTLT

Г

Г

и

п п

U U U U

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь синусоидальных сигналов перемещения в код | 1984 |

|

SU1234968A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ВИБРАЦИЙ | 1986 |

|

SU1378548A1 |

| Микропроцессор | 1982 |

|

SU1045231A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1987 |

|

SU1439612A1 |

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

| Устройство для измерения ритма сердца | 1985 |

|

SU1284512A1 |

| СИГНАТУРНЫЙ АНАЛИЗАТОР | 1991 |

|

RU2017209C1 |

УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ АНАЛОГОВОЙ ИНФОРМАЦИИ, содержащее два формирователя логических уровней, выходы которых подключены к информационным входам первого блока памяти, первый и второй выходы которого подключены соответственно к первым и вторым входам второго блока памяти и дешифратора, выходы второго блока памяти подключены к третьему и четвертому входам дешифратора, отличающееся тем, что, с целью повышения помехоустойчивости устройства, в него введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два инвертора, два элемента И-НЕ, формирователь импульсов и триггер, выходы формирователей логических уровней подключены к входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к входу первого инвертора и первому входу первого элемента И-НЕ, выход первого инвертора подключен к первому входу второго элемента И-НЕ выход которого объединен с выходом первого элемента И-НЕ и подключен к входу формирователя импульсов, выход которого подключен к синхровходам триггера, первого блока памяти и через второй инвертор (g к синхровходу второго блока памяти, пря(Л мой выход триггера подключен к второму входу второго элемента И - НЕ, инверсный выход триггера подключен к его информационному входу и второму входу первого элемента И-НЕ. 05. 05 00 О ГС

Риг.г

| Преобразователь перемещения в код | 1977 |

|

SU649006A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для дискретной обработки аналоговой информации | 1975 |

|

SU591899A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-07-07—Публикация

1984-01-09—Подача