Изобретение относится к электросвязи и может использоваться в многоканальных, синхронных системах связи.

Известно устройство для синхронизации многоканальных систем связи, содержащее п усилителей-ограничителей, блок выделения знакоперемен сигнала, к тактовому входу которого и к соответствующему входу запоминающего блока подключен выход задающего генератора, причем между выходами и входами основных разрядов запоминающего блока включен арифметический блок, а между выходами и входами дополнительных разрядов - блок управления 1.

Однако в известном устройстве наличие в каждом канале индивидуальных блоков выделения знакоперемен и в особенности многоразрядных каскадов сравнения ходов на выходе устройства приводит к значительному росту объема оборудования с увеличением числа обслуживаемых каналов, и как следствие к понижению надежности устройства.

Цель изобретения - упрощение устройства.

Цель достигается тем, что в устройство для синхронизации многоканальных систем связи, содержащее п усилителей-ограничителей, блок выделения знакоперемен сигнала, к тактовому входу которого и к соответствующему входу запоминающего блока подключен выход задающего генератора, причем между выходами и входами основных разрядов запоминающего блока включен арифметический блок, а между выходами и входами дополнительных разрядов - блок управления, введены входной и выходной коммутаторы, управляемые распределителем, и последовательно соединенные арифметический сумматор и дополнительный запоминающий блок, при этом выход блока выделения знакоперемен сигнала подключен к дополнительному входу блока управления и к соответствующему входу дополнительного запоминающего блока, выходы которого подключены к дополнительным входам арифметического блока, а выходы основных разрядов запоминающего блока подключены к соответствующим входам дополнительного запоминающего блока и к соответствующим входам арифметического сумматора, к другим входам которого подключены выходы дополнительных разрядов запоминающего блока, а выходы арифметического сумматора подключены к соответствующим входам блока управления, кроме того, выход задающего генератора подключен к счетному входу распределителя, а выходы п усилителей-ограничителей через входной коммутатор подключены к информационному входу блока выделения знакоперемен.

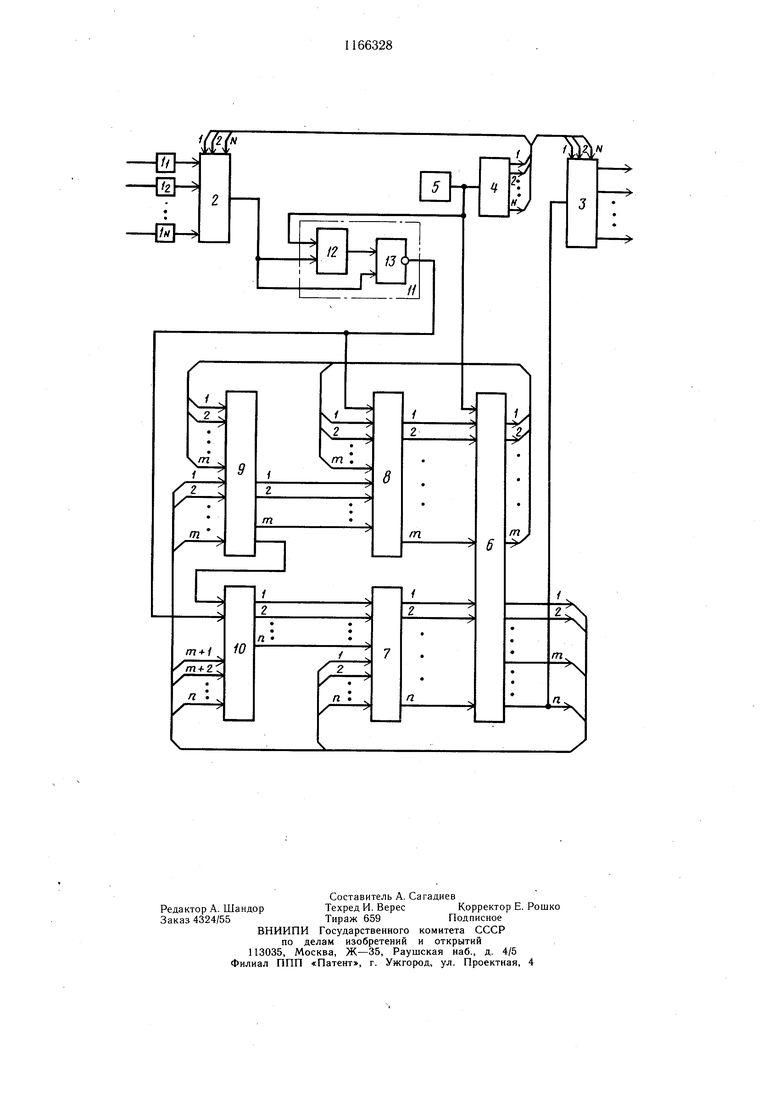

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство для синхронизации многоканальных систем связи содержит п усилителей ограничителей 1 (Ij, 1 ,...,1д ), входной коммутатор 2, выходной коммутатор 3, распределитель 4, задающий генератор 5, запоминающий блок 6, арифметический блок 7, блок 8 управления, арифметический сумматор 9, дополнительный запоминающий блок 10, блок 11 выделения знакоперемен сигнала, состоящий из сдвигающего регистра 12 и сумматора 13 по модулю два.

5 Устройство работает следующим образом.

Усиленный и ограниченный сигнал каждого канала поступает на вход входного коммутатора 2. Тактовые импульсы задающего генератора 5, имеющего частоту ТЕ;, поступают на вход распределителя 4, имеющего столько адресов, сколько каналов обслуживается системой синхронизации. Поэтому каждый, из каналов опрашивается с частотой FO . где N - число каналов.

5 С выхода входного коммутатора 2 отсчеты линейного сигнала подаются на вход сдвигающего регистра 12 блока 11, сдвиг информации в котором производится синхронно с работой входного коммутатора 2. Поэтому на входе и выходе сдвигающего регистра 12 выделяется пара смежных отсчетов входного сигнала каждого из каналов связи. Полярность каждой пары отсчетов сравнивается сумматорсгм 13 по модулю два, который определяет знакоперес мену в линейном сигнале при несовпадении полярности смежной пары отсчетов.

Сигнал знакоперемены с выхода сумматора 13 по модулю два подается на управляющий вход блока 8 управления и запоминающего блока 10.

При отсутствии знакоперемены устройство работает следующим образом.

При этом на входе запоминающего блока 10 удерживается потенциал, соответствующий числу « + 1, которое добавляется к числу на выходах основных разрядов запоминающего блока 6.

Так как сдвиг информации в запоминающем блоке 6 происходит с частотой F, , число ячеек памяти которого равно числу каналов, то добавление «4-1 к числу,

0 имеющемуся в запоминающем, блоке 6, происходит с частотой FO , что соответствует циклу работы входного 2 и выходного 3 коммутаторов.

При числе основных разрядов, равном п,

на выходах запоминающего блока 6 образуется последовательность чисел 0,1,2,..., , 0,1,..., 2,... . Любое из чисел этой последовательности повторяется с тактовой

частотой l заданного значения 4 частоту задающего генератора 5

МОЖНО определить как

.N-f

Т4

Для вывода тактовой частоты к потребителям сигналы с выхода старшего из основных разрядов запоминающего блока б подаются на групповой вход выходного коммутатора 3, работающего синхронно с входным. Тактовая частота, выводимая из многоканальной системы синхронизации, имеет форму меандра, поскольку старщий из основных разрядов в состояниях О, 1, 2,... принимает значение двоичного нуля, а в состояниях + 1; ...2 - состояние двоичной единицы.

Выходы дополнительных m разрядов запоминающего блока 6 через блок 8 управления подключается к входам записи этих же разрядов. Это позволяет организовать режим хранения ранее записанной информации в дополнительных разрядах запоминающего блока 6.

В арифметическом сумматоре 9 постоянно происходит суммирование чисел первого слагаемого, образованного m дополнительными разрядами запоминающего блока 6 и второго слагаемого, образованного младщими m разрядами из числа основных. При этом число п-m определяет коррекционный эффект системы синхронизации.

При поступлении знакоперемены с выхода арифметического сумматора 9 младшая часть суммы (т-разрядное число) через блок 8 записывается в дополнительные разряды запоминающего блока 6 и далее хранится до следующей знакоперемены. Из старших (п-т) разрядов суммы и сигнала переноса, которые подаются на адресные входы запоминающего блока 10, определяется число, соответствующее сигналу коррекции фазы тактовой частоты. Для корректирования фазы тактовой частоты

0 на арифметический бл.ок 7 подаются как сигналы с выхода основных разрядов запоминающего блока 6 (текущая фаза), так и сигнал подстройки, принимающий значения -2, -1,0+1+2, в зависимости от

5 расхождения фаз.

Таким образом, подстройка фазы тактовой частоты происходит только в моменты появления знакоперемен во входном сигнале. При этом в отсутствие знакоперемен основные разряды запоминающего блока 6

0 и арифметический блок 7 образуют делитель частоты с коэффициентом деления , а в дополнительных разрядах хранятся результаты промежуточных вычислений, определяющих инерционные свойства

5 системы синхронизации.

Применение предложенного устройства позволяет значительно уменьшить объем оборудования и повысить его надежность по сравнению с известными устройствами. Экономический эффект на 1 комплекте

0 16-канальной системы синхронизации составит ориентировочно 1400-2000 руб.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканальной дискретной автоподстройки частоты синхронизации | 1976 |

|

SU571922A2 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи | 1984 |

|

SU1234992A1 |

| Устройство групповой тактовой синхронизации | 1982 |

|

SU1022325A2 |

| Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи | 1986 |

|

SU1354434A1 |

| Динамическое запоминающее устройство | 1982 |

|

SU1065886A1 |

| Устройство для формирования сигнала с многократной относительной фазовой модуляцией | 1984 |

|

SU1241518A1 |

| Устройство для формирования частотно-манипулированного сигнала | 1980 |

|

SU919147A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ МНОГОКАНАЛЬНЫХ СИСТЕМ СВЯЗИ, содержащее п усилителейограничителей, блок выделения знакоперемен сигнала, к тактовому входу которого и к соответствующему входу запоминающего блока подключен выход задающего генератора, причем между выходами и входами основных разрядов запоминающего блока включен арифметический блок, а между выходами и входами дополнительных разрядов - блок управления, отличающееся тем, что, с Целью упрощения устройства путем исключения датчика аппаратного времени и каскадов обработки сигнала, в него введены входной и выходной коммутаторы, управляемые распределителем, и последовательно соединенные арифметический сумматор и дополнительный запоминающий блок, при этом выход блока выделения знакоперемен сигнала подключен к дополнительному входу блока управления и к соответствующему входу дополнительного запоминающего блока, выходы которого подключены к дополнительным входам арифметического блока, а выходы основных разрядов запоминающего блока подключены к соответствующим входам дополнительного запоминающего блока и к соответствующим входам арифметического сумматора, к другим входам которого подключены выходы дополнительных разрядов запоминающего блока, а выходы арифмеS тического сумматора подключены к соответствующим входам блока управления, кроме того, выход задающего генератора подключен к счетному входу распределителя, а выходы п усилителей-ограничителей через входной коммутатор подключены к информационному входу блока выделения знакоперемен. О5 О5 СО IN5 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 431640, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-07-07—Публикация

1976-06-01—Подача