со

9д

113

Изобретение относится к автомати ке и вычислительной технике и может быть использовано в вычислительных устройствах при проектировании микропрограммных устройств с времяраспре- деленными функциями, а также в средствах службы единого времени или системах подсчета ресурса работы уст ройств.

Целью изобретения является расширение функциональных возможностей за счет обеспечения выдачи управляющих команд в различных кодах.

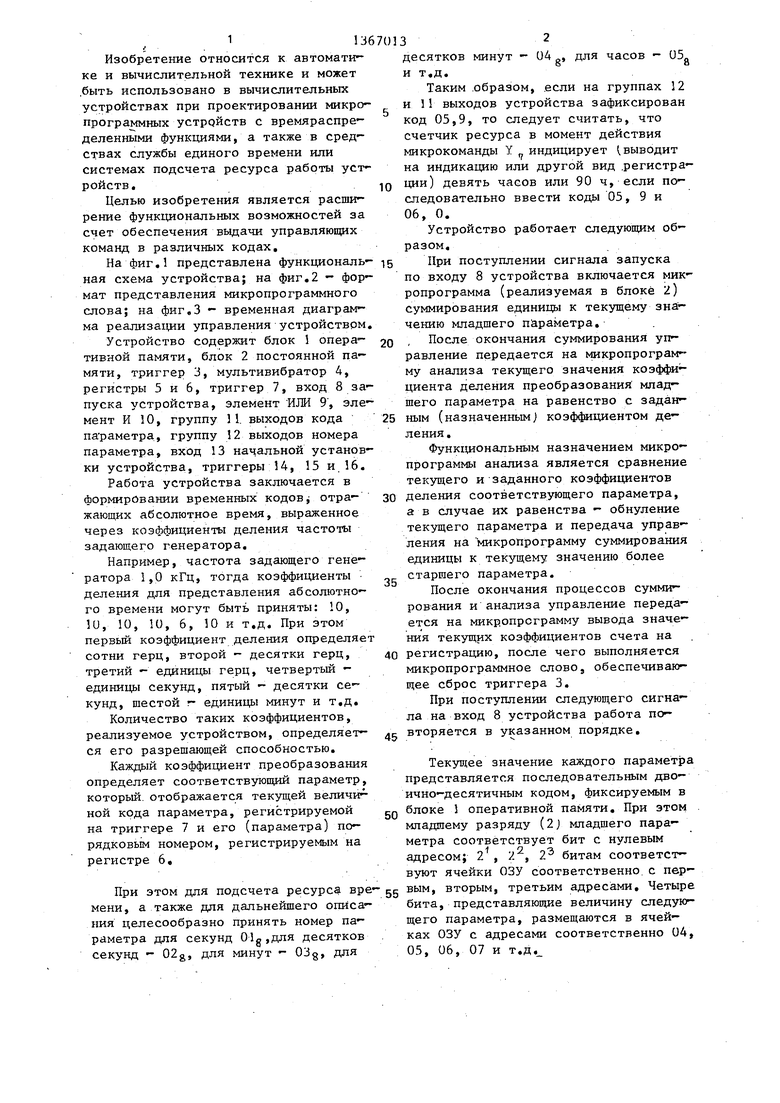

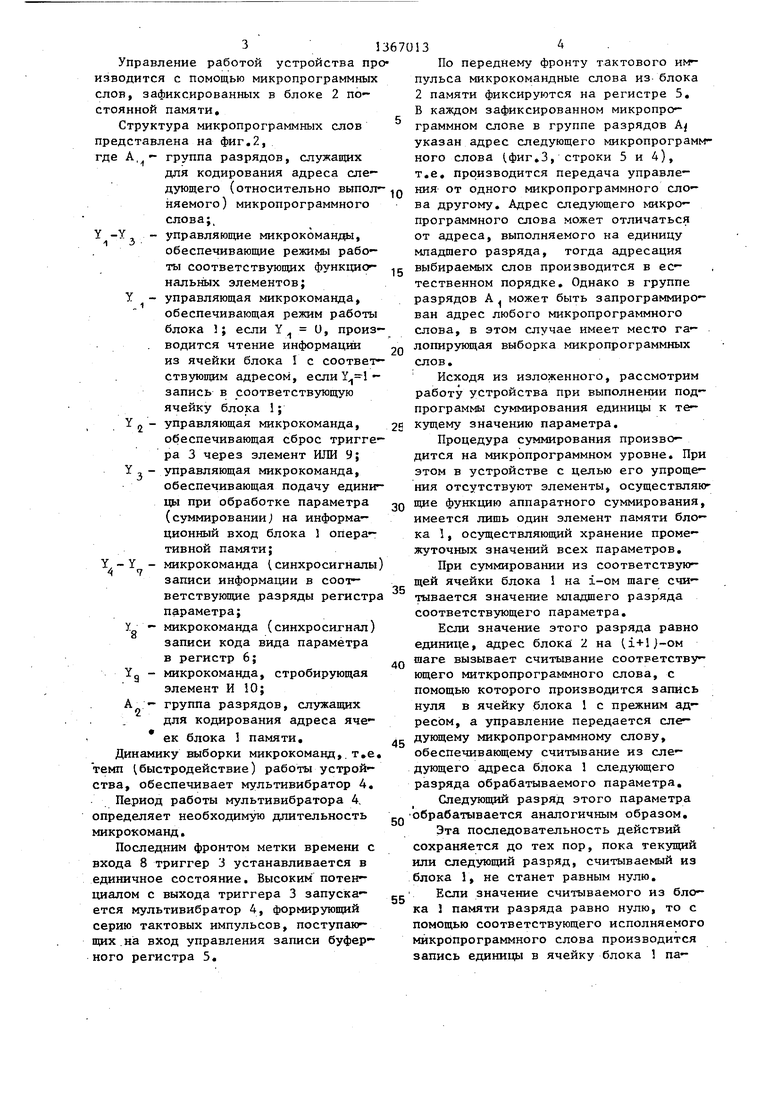

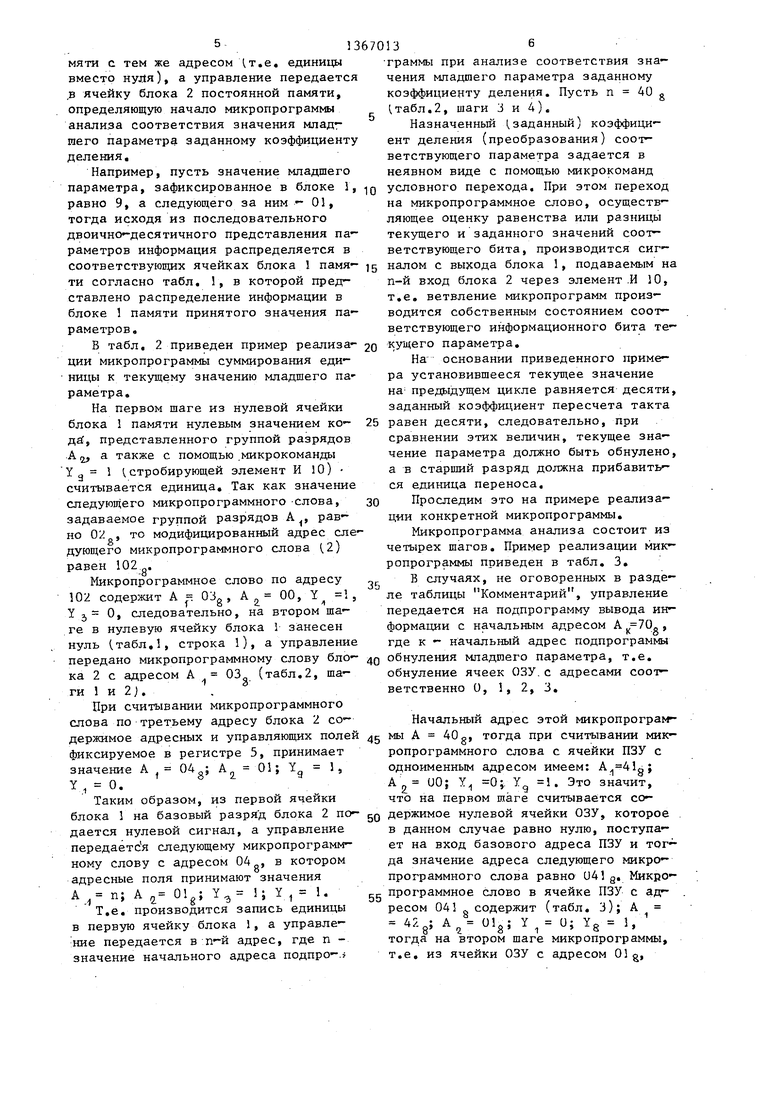

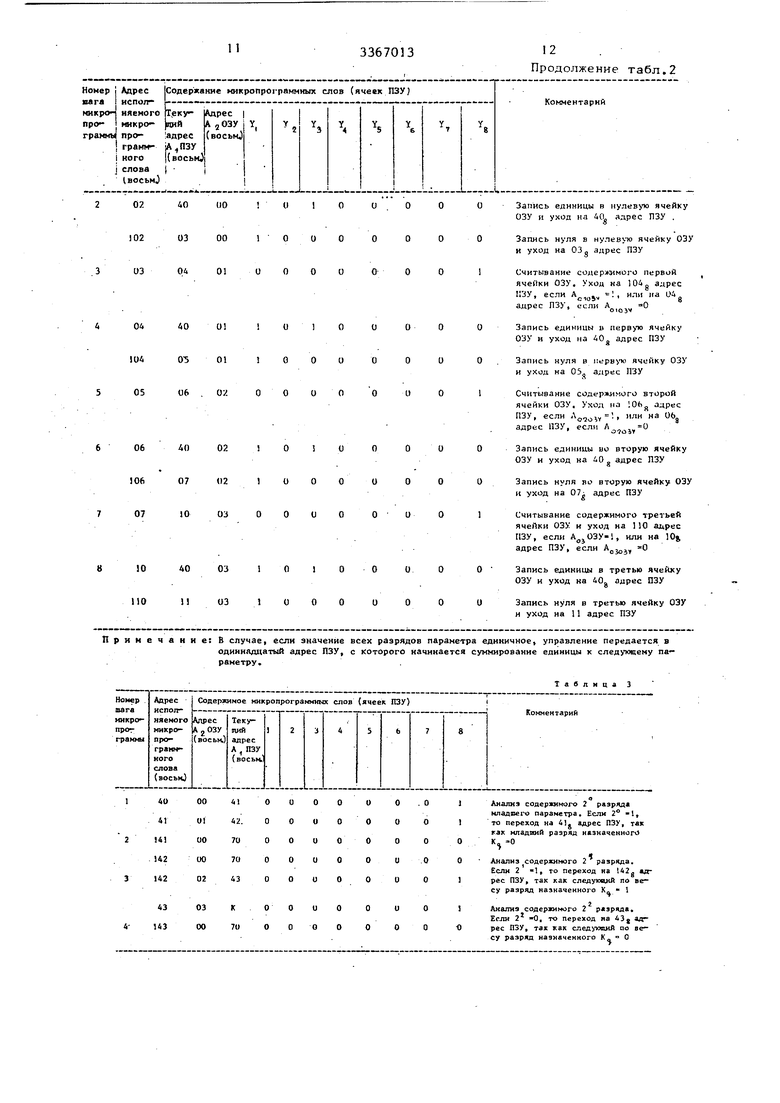

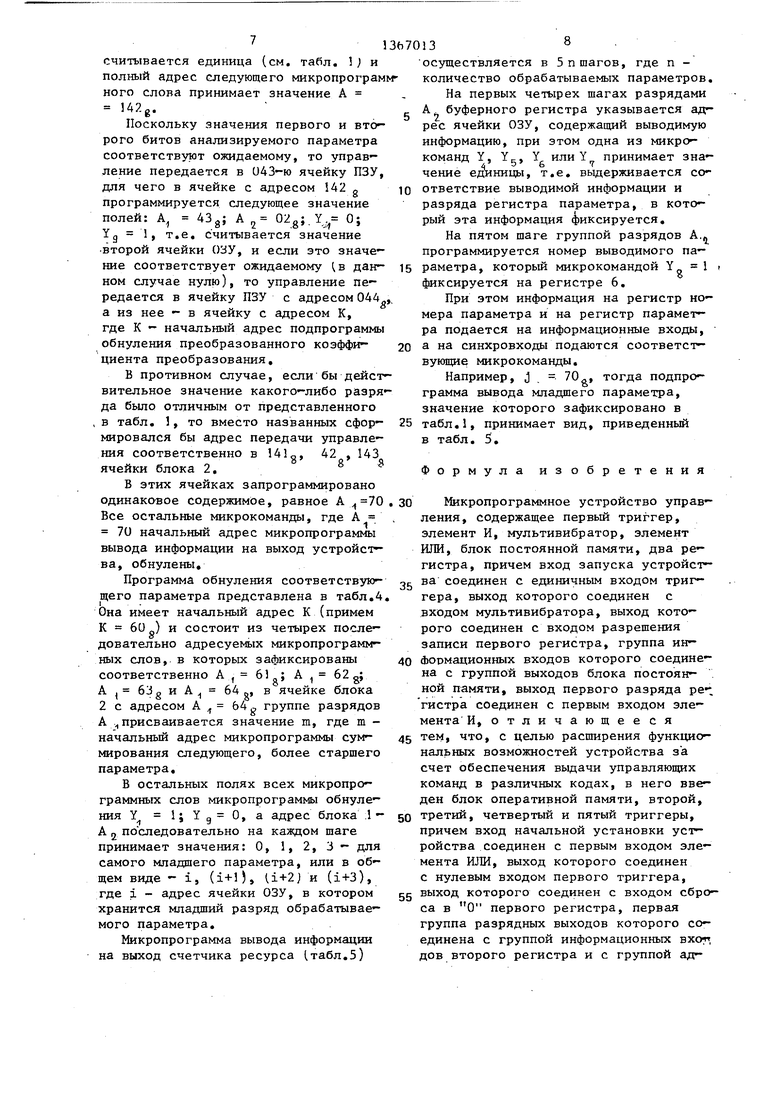

На фиг,1 представлена функциональ- ная схема устройства; на фиг,2 - формат представления микропрограммного слова; на фиг,3 - временная диаграмма реализации управления устройством

Устройство содержит блок J опера- тивной памяти, блок 2 постоянной памяти, триггер 3, мультивибратор 4, регистры 5 и 6, триггер 7, вход 8 запуска устройства, элемент ИЛИ 9, элемент И 10, группу 11. выходов кода параметра, группу 12 выходов номера параметра, вход 13 начальной установки устройства, триггеры 14, 15 и 16,

Работа устройства заключается в формировании временных кодовj отра- жающих абсолютное время, выраженное через коэффициенты деления частоты задающего генератора,

Например, частота задающего генератора 1,0 кГц, тогда коэффициенты деления для представления абсолютного времени могут быть приняты: 0, 1U, 10, 10, 6, 10 и т,д. При этом первый коэффициент делеьшя определяет сотни герц, второй - десятки герц, третий - единицы герц, четвертый - единицы секунд, пятый - десятки секунд, шестой г- единицы минут и т,д,

Количество таких коэффициентов, реализуемое устройством, определяет- ся его разрешающей способностью.

Каждый коэффициент преобразования определяет соответствующий параметр, который. Отображается текущей величиной кода параметра, регистрируемой на триггере 7 и его (параметра) порядковым номером, регистрируемым на регистре 6,

При этом для подсчета ресурсу вре- мени, а также для дальнейшего описания целесообразно принять номер параметра для секунд 01д,для десятков секунд - 02g, для минут - 03g, для

32

десятков минут - 04 .., для часов - 05

оо

и т,д.

Таким .образом, если на группах 12 и 11 выходов устройства зафиксирован код 05,9, то следует считать, что счетчик ресурса в момент действия микрокоманды Y индицирует выводит на индикацию или другой вид .регистрации) девять часов или 90 ч, если последовательно ввести коды 05, 9 и 06, О,

Устройство работает следующим образом.

При поступлении сигнала запуска по входу 8 устройства включается микропрограмма (реализуемая в блоке 2) суммирования единицы к текущему значению младшего параметра.

После окончания суммирования управление передается на микропрограмму анализа текущего значения коэффициента деления преобразования младшего параметра на равенство с заданным (назначенным) коэффициентом деления ,

Функ1щональным назначением микропрограммы анализа является сравнение текущего и заданного коэффициентов деления соответствующего параметра, а в случае их равенства - обнуление текущего параметра и передача управления на микропрограмму суммирования единицы к текущему значению более старшего параметра.

После окончания процессов суммирования и анализа управление передается на микропрограмму вывода значения текущих коэффициентов счета на регистрацию, после чего выполняется микропрограммное слово, обеспечивающее сброс триггера 3,

При поступлении следующего сигнала на вход 8 устройства работа повторяется в указанном порядке.

Текущее значение каждого параметра представляется последовательным двоично-десятичным кодом, фиксируемым в блоке 1 оперативной памяти. При этом младшему разряду (2 j младшего параметра соответствует бит с нулевым адресом; 2,2,2 битам соответствуют ячейки ОЗУ соответственно, с первым, вторым, третьим адресами. Четыре бита, представляющие величину следуюг- щего параметра, размещаются в ячейках ОЗУ с адресами соответственно 04, 05, 06, 07 и т,д,

Управление работой устройства призводится с помощью микропрограммных слов, зафиксированных в блоке 2 постоянной памяти.

Структура микропрограммных слов представлена на фиг.2, где А,- группа разрядов, служащих

для кодирования адреса следующего (относительно выполняемого) микропрограммного слова;, Y -Y - управляющие микрокоманды,

обеспечивающие режимы работы соответствующих функцисг- нальных элементов; Y - управляющая микрокоманда,

обеспечивающая режим работы блока ; если Y U, производится чтение информации из ячейки блока I с соответствующим адресом, ecлиY -l- запись в соответствующую ячейку блока 1;

Yj- управляющая микрокоманда, обеспечивающая сброс триггера 3 через элемент ИЛИ 9; Y - управляющая микрокоманда,

обеспечивающая подачу единицы при обработке параметра (суммировании; на информационный вход блока 1 оперативной памяти;

Y -Y - микрокоманда iсинхросигналы записи информации в соответствующие разряды регистр параметра;

У - микрокоманда (синхросигнал) записи кода вида параметра в регистр 6; Yg - микрокоманда, стробирующая

элемент И 10; А. - группа разрядов, служащих

для кодирования адреса ячеек блока 1 памяти. Динамику выборки микрокоманд,.т,е темп быстродействие) работы устройства, обеспечивает мультивибратор 4,

Период работы мультивибратора 4, определяет необходимую длительность микрокоманд,

Последним фронтом метки времени с входа 8 триггер 3 устанавливается в единичное состояние. Высоким потенциалом с выхода триггера 3 запуска- ется мультивибратор 4, формирующий серию тактовых импульсов, поступающих. Hia вход управления записи буферного регистра 5,

0

g

,,

S

Q

-

0

5

0

По переднему фронту тактового импульса микрокомандные слова из- блока 2 памяти фиксируются на регистре 5, В каждом зафиксированном микропрограммном слоне в группе разрядов А указан адрес следующего микропрограммного слова (,фиг,3, строки 5 и 4), т.е, производится передача управления от одного микропрограммного слова другому. Адрес следующего микропрограммного слова может отличаться от адреса, выполняемого на единицу младшего разряда, тогда адресация выбираемых слов производится в естественном порядке. Однако в группе разрядов А может быть запрограммирован адрес любого микропрограммного слова, в этом случае имеет место галопирующая выборка микропрограммных слов,

Исходя из изложенного, рассмотрим работу устройства при выполнении подпрограммы суммирования единицы к текущему значению параметра.

Процедура суммирования производится на микропрограммном уровне. При этом в устройстве с целью его упрощения отсутствуют элементы, осуществляю щие функцию аппаратного суммирования, имеется лишь один элемент памяти блока 1 , осуществляющий хранение промежуточных значений всех параметров.

При суммировании из соответствующей ячейки блока на i-ом шаге считывается значение младшего разряда соответствующего параметра.

Если значение этого разряда равно единице, адрес блока 2 на (.1+1}-ом шаге вызывает считывание соответствующего миткропрограммного слова, с помощью которого производится запись нуля в ячейку блока 1 с прежним адресом, а управление передается следующему микропрограммному слову, обеспечивающему считывание из следующего адреса блока 1 следующего разряда обрабатываемого параметра.

Следующий разряд этого параметра обрабатывается аналогичным образом.

Эта последовательность действий сохраняется до тех пор, пока текущий или следующий разряд, считываемый из блока 1, не станет равным нулю,

Если значение считываемого из блока J памяти разряда равно нулю, то с помощью соответствующего исполняемого микропрограммного слова производится запись единицы в ячейку блока 1 памяти с тем же адресом Л т.е. единицы вместо нуйя), а управление передается в ячейку блока 2 постоянной памяти, определяющую начало микропрограммы анализа соответствия значения младг шего параметра заданному коэффициенту деления.

Например, пусть значение младшего

граммы при анализе соответствия значения младшего параметра заданному коэффициенту деления. Пусть п 40 g (.табл.2, шаги 3 и 4).

Назначенный I,заданный) коэффициент деления (преобразования) соответствующего параметра задается в неявном виде с помощью микрокоманд

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный микропрограммный счетчик | 1985 |

|

SU1280598A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для ввода информации | 1986 |

|

SU1352479A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1305681A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1287155A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для приема заказов | 1985 |

|

SU1316020A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

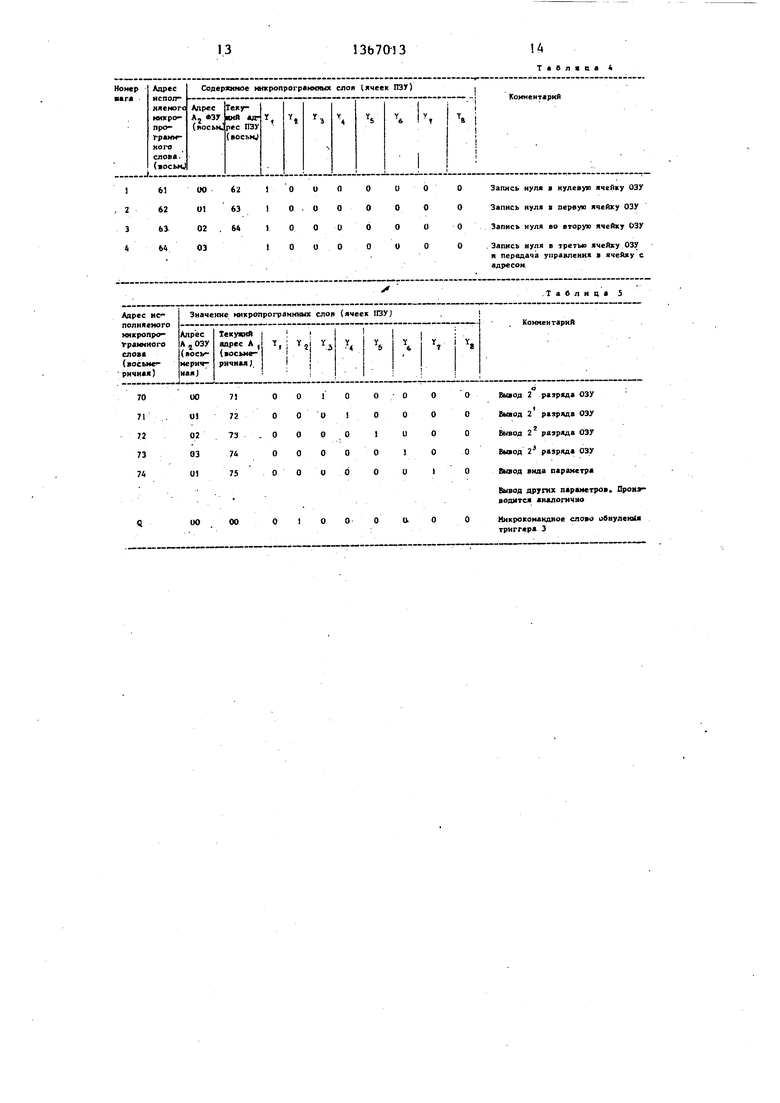

параметра, зафиксированное в блоке 1, Q условного перехода. При этом переход равно 9, а следующего за ним- 01, на микропрограммное слово, осуществ- тогда исходя из последовательного ляющее оценку равенства или разницы двоично-десятичного представления па- текущего и заданного значений соот- раметров информация распределяется в ветствующего бита, производится сиг- соответствующих ячейках блока 1 памя- g налом с выхода блока 1, подаваемым на ти согласно табл. 1, в которой пред- п-й вход блока 2 через элемент .И 10, ставлено распределение информации в блоке 1 памяти принятого значения параметров.

т.е. ветвление микропрограмм производится собственным состоянием соответствующего информационного бита теВ табл. 2 приведен пример реализа- 2о кутдего параметра.

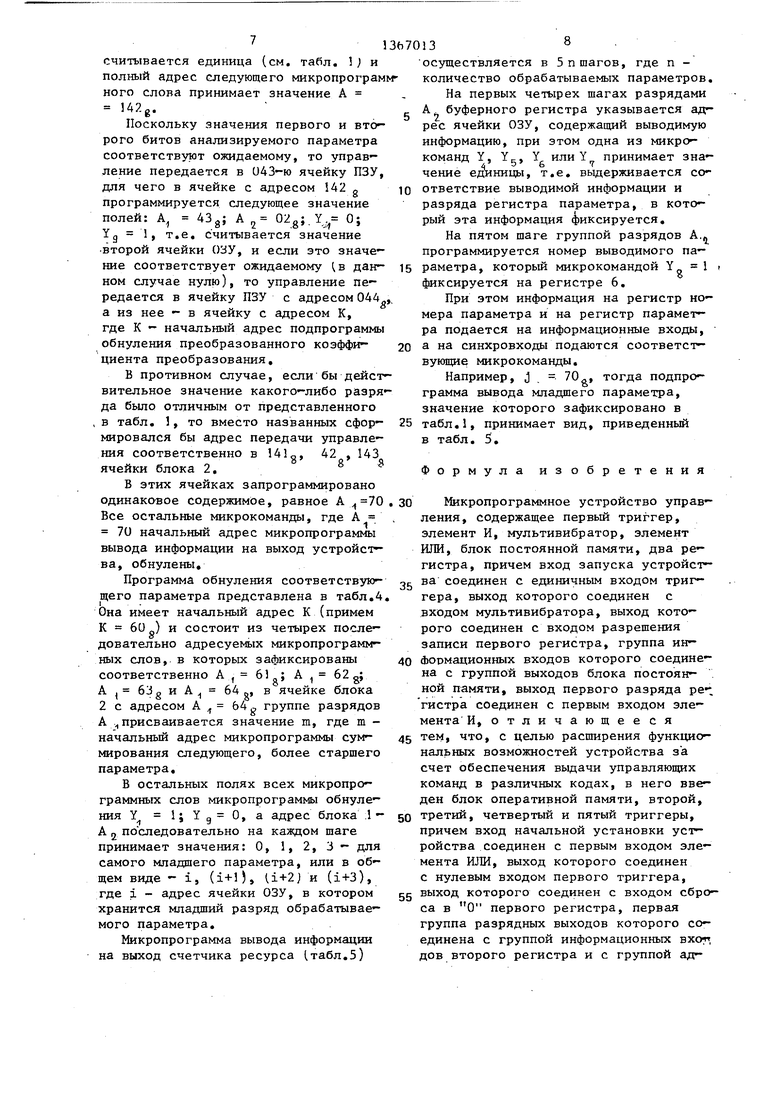

ции микропрограммы суммирования еди- ницы к текущему значению младшего па раметра.

На первом шаге из нулевой ячейки

блока 1 памяти нулевым значением ко- 25 равен десяти, следовательно, при

дй, представленного группой разрядов А 2;, а также с помощью .микрокоманды Yg 1 стробирующей элемент И Ш) считывается единица. Так как значение следующего микропрограммного -слова, задаваемое группой разрядов А, равно 02 , то модифицированный адрес следующего микропрограммного слова (2 равен 102 .

Микропрограммное слово по адресу 102 содержит А 03g , А 00, Y 1, Y 5 О, следовательно, на втором шаге в нулевую ячейку блока 1 занесен нуль (табл.1, строка 1), а управление

передано микропрограммному слову бло- 40 обнуления младшего параметра, т.е. ка 2 с адресом А 03 (табл.2, ша- обнуление ячеек ОЗУ.с адресами соот- ги 1 и 2). ,ветственно О, 1, 2, 3.

При считывании микропрограммного

слова по третьему адресу блока 2 со- Начальный адрес этой микропрогра1 г- держимое адресных и управляющих полей 45 А. 40g, тогда при считывании мик- фиксируемое в регистре 5, принимает ропрограммного слова с ячейки ПЗУ с

значение А

одноименным адресом имеем: А,(;

Y 0. А 00; Y 0;. Yg 1. Это значит.

Таким образом, из первой ячейки что на первом шаге считывается со- блока 1 на базовый разряд блока 2 по- gQ держимое нулевой ячейки ОЗУ, которое

дается нулевой сигнал, а управление передается следующему микропрограммному слову с адресом 04„, в котором адресные поля принимают значения А п; А Olg; Y 1; Y 1.

Т.е. производится запись единицы в первую ячейку блока 1, а управле- ние передается в п-й адрес, где п - значение начального адреса подпро-.j

в данном случае равно нулю, поступает на вход базового адреса ПЗУ и тогда значение адреса следующего микропрограммного слова равно U41д. Микро- gg программное слово в ячейке ПЗУ с адресом 041 g содержит (табл. З); А

«-gJ А. Y, и; Yg 1, тогда на втором шаге микропрограммы, т.е. из ячейки ОЗУ с адресом 01g.

условного перехода. При этом переход на микропрограммное слово, осуществ- ляющее оценку равенства или разницы текущего и заданного значений соот- ветствующего бита, производится сиг- налом с выхода блока 1, подаваемым на п-й вход блока 2 через элемент .И 10,

т.е. ветвление микропрограмм производится собственным состоянием соответствующего информационного бита теНа основании приведенного примера установившееся текущее значение на предыдущем цикле равняется десяти, заданный коэффициент пересчета такта

0

5

сравнении этих величин, текущее значение параметра должно быть обнулено, а в старший разряд должна прибавиться единица переноса.

Проследим это на примере реализации конкретной микропрограммы.

Микропрограмма анализа состоит из четырех шагов. Пример реализации микропрограммы приведен в табл. 3.

В случаях, не оговоренных в разделе таблицы Комментарий, управление передается на подпрограмму вывода информации с начальным адресом А .70,. , где к - начальный адрес подпрограммы

одноименным адресом имеем: А,(;

А 00; Y 0;. Yg 1. Это значит

в данном случае равно нулю, поступает на вход базового адреса ПЗУ и тогда значение адреса следующего микропрограммного слова равно U41д. Микро- gg программное слово в ячейке ПЗУ с адресом 041 g содержит (табл. З); А

«-gJ А. Y, и; Yg 1, тогда на втором шаге микропрограммы, т.е. из ячейки ОЗУ с адресом 01g.

считывается единица (см. табл. 1; и полный адрес следующего MHKponporpaMNr ного слова принимает значение А

142

i

Поскольку значения первого и вто- рого битов анализируемого параметра соответствуют ожидаемому, то управление передается в ОДЗ-ю ячейку ПЗУ для чего в ячейке с адресом 142 g программируется следующее значение полей: А 43g; А 2 02g;,Y 0; Yg 1, Т.е. считывается значение второй ячейки ОЗУ, и если это значение соответствует ожидаемому в данном случае нулю), то управление передается в ячейку ПЗУ с адресом 044 а из нее - в ячейку с адресом К, где К - начальный адрес подпрограммы обнуления преобразованного коэффициента преобразования,

В противном случае, если бы действительное значение какого-либо разряда было отличным от представленного , в табл. 1, то вместо названных сформировался бы адрес передачи управления соответственно в 141„, 42 ,143 ячейки блока 2.88

В этих ячейках запрограммировано одинаковое содержимое, равное А 70 Все остальные микрокоманды, где А 70 начальный адрес микропрограммы вывода информации на выход устройства, обнулены.

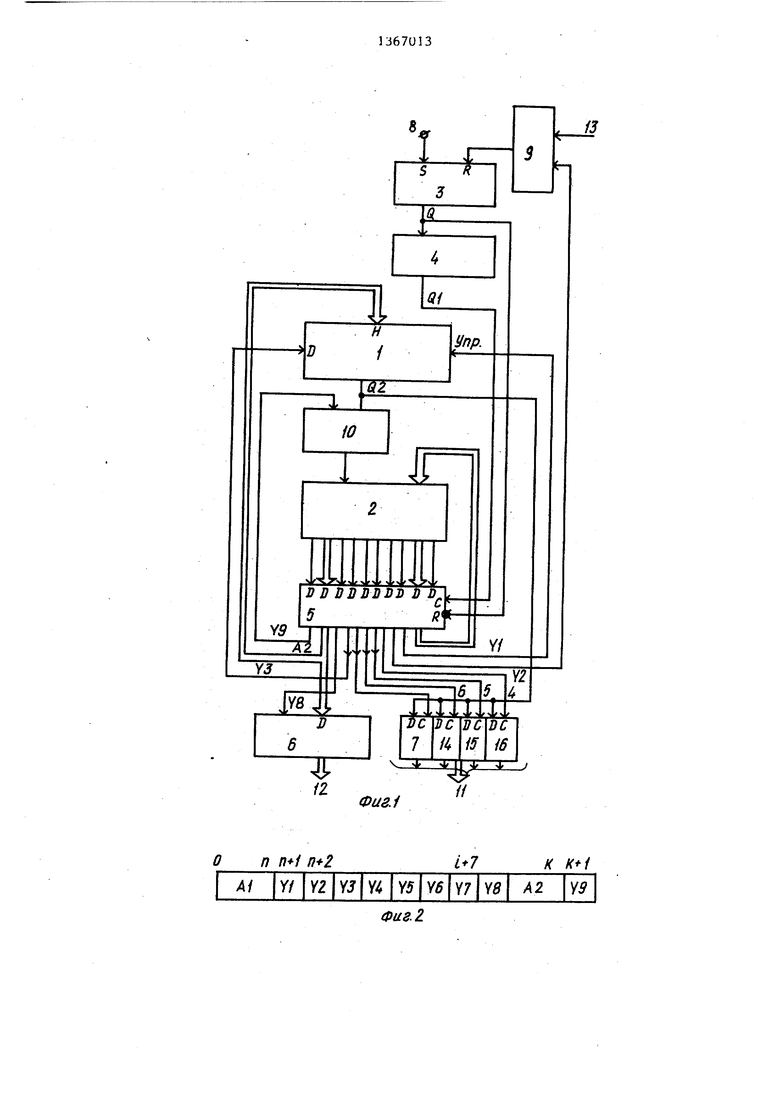

Программа обнуления соответствующего параметра представлена в табл,4 Она имеет начальный адрес К (примем К 60 ) и состоит из четырех последовательно адресуемых микропрограммных слов, в которых зафиксированы соответственно А , 61„; А

АГ

А, 63g и А 64

8 1 - 62 g; в ячейке блока

2 с адресом А 64 „ группе разрядов А присваивается значение т, где m - начальный адрес микропрограммы суммирования следующего, более старшего параметра,

В остальных полях всех микропрограммных слов микропрограммы обнуления Y , а адрес блока ;1 - А 2 по следовательно на каждом шаге принимает значения: О, 1, 2, 3 - для самого младшего параметра, или в общем виде - i, (i+l), (i+2) к (i+З), где i - адрес ячейки ОЗУ, в котором хранится младший разряд обрабатываемого параметра.

Микропрограмма вывода информации на выход счетчика ресурса (табл,5)

r

осуществляется в 5пшагов, где п - количество обрабатываемых параметров. На первых четырех шагах разрядами А буферного регистра указывается адрес ячейки ОЗУ, содержащий выводимую информацию, при этом одна из микроYC, Y, илиY„ принимает знакоманд Y, J. g,

Y или Y

i о 6 7

чение единицы, т.е. выдерживается со

10 ответствие выводимой информации и разряда регистра параметра, в который эта информация фиксируется.

На пятом шаге группой разрядов А. программируется номер выводимого па-

15 раметра, который микрокомандой Y 1 фиксируется на регистре 6.

При этом информация на регистр номера параметра и на регистр параметра подается на информационные входы,

20 э на синхровходы подаются соответствующие микрокоманды.

Например, J 70д, тогда подпрограмма вывода младшего параметра, значение которого зафиксировано в

25 табл,1, принимает вид, приведенный в табл. 5,

Формула изобретения

Микропрограммное устройство управления, содержащее первый триггер, элемент И, мультивибратор, элемент ИЛИ, блок постоянной памяти, два регистра, причем вход запуска устройст-

ва соединен с единичным входом триггера, выход которого соединен с входом мультивибратора, выход которого соединен с входом разрешения записи первого регистра, группа ин-

Формационных входов которого соединена с группой выходов блока постоян- . ной памяти, выход первого разряда ре, гистра соединен с первым входом элемента И, отличающееся

тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения выдачи управляющих команд в различных кодах, в него введен блок оперативной памяти, второй,

третий, четвертый и пятый триггеры, причем вход начальной установки устройства соединен с первым входом элемента ШШ, выход которого соединен с нулевым входом первого триггера,

выход которого соединен с входом сброса в О первого регистра, первая группа разрядных выходов которого соединена с группой информационных вхог дов второго регистра и с группой ад-

ресных входов блока оперативной па-- мяти, информационный вход которого соединен с вторым разрядным выходом первого регистра, третий разрядный выход которого соединен с входом разрешения записи второго регистра,груп па разрядных выходов которого является группой выходов номера параметра устройства, вторая группа разрядных выходов первого регистра соединена с входами с первого по п-3)-й группы адресных входов блока постоянной памяти, четвертый разрядный выход первого регистра соединен с вторым входом элемента ИЛИ, пятый разрядный выход первого регистра соединен с

0001(К)О и О ОО

010200О О О ОО

входом разрешения записи блока оперативной памяти, тестой, седьмой, восьмой и. девятый разрядные выходы первого регистра соединены с синхро- входами соответственно второго, третьего, четвертого и пятого триггеров, информационные входы которых соединены с выходом блока оперативной памяти и с вторым входом элемента И, выход которого соединен с п-м входом группы адресных входов блока постоянной памяти, выходы второго, третьего, четвертого и пятого .триггеров являются соответственно первым, вторым, третьим и четвертым выходами группы выходов кода параметра устройства.

а 1

Таблица 2

Вход в микропрограмму суммирования

Считывание содержимого нулевой ячейки ОЗУ, Уход на 102 адрес, если содержимое ОЗУ равно 1, или - на 02gадрес, если содер- жимое ОЗУ равно О

10203001000

030401о о о о

0440О 101оооо

10405011000ооо

0640021010О00

10607021000

071003О О и О

10

4003

1010

ПО

И03100

Примечание В случае, если значение одиннадцатый адрес ПЗУ, ранетру.

14U0041О и О О 41 01 42.GOOD

2 4 00700000

142

00700000

14202430000

4303КО О О О

14300700000

. о

оо

оо

оо

00

ОО

00

о - Запись еднницы в нулевую ячейку ОЗУ н уход на 40. адрес ПЗУ .

О

0Запись нуля в нулевую ячейку ОЗУ и уход на 03д адрес ПЗУ

в

1Считывание содержимого первой ячейки ОЗУ. Уход на 104 адрес , если A,yj 1, или па 04 адрес ПЗУ, если А 0

О Запись единицы в первую ячейку ОЗУ н уход на 40 адрес ПЗУ

0. Запись нуля в ячейку ОЗУ

и уход на 05, адрес ПЗУ

1Считывание содержимого второй ячейки ОЗУ, Уход на ЮЬ адрес ПЗУ, если Лд, ; , или на 06 адрес ПЗУ, если Л.0

О Запись единицы во вторую ячейку ОЗУ н уход на 40 адрес ПЗУ

0Запись нуля во вторую ячейку ОЗУ к уход на 07 адрес ПЗУ

1Считывание содержимого третьей ячейки ОЗУ и уход на 110 адрес ПЗУ, если A j03y-, илн на 10 адрес ПЗУ, если , 0

О Запись единицы в третью ячейку ОЗУ и уход на 40 адрес ПЗУ

О Запись нуля в третью ячейку ОЗУ и уход на 11 адрес ПЗУ

всех разрядов параметра единичное, управление передается в с которого иачинается сутчирование еднницы к следующему па-

Тавлнца 3

. О

О

О

о

о

1 1 о о 1

1

о

Аналнэ содержимого 2 разряда младшего параметра. Если 2 , то переход на 4. адрес ПЗУ, так гак младвшй разряд назначенного

S-0

Анализ содер.жимого 2 разряда. Если 2 1, то переход на адрес ПЗУ, так как следу)сщ1Й по весу разряд назначенного К. 1

Анализ содержимого 2 р«эряда« Если 2 О, то переход па u3j адрес ПЗУ, так как cneAjTOHiwfl по весу разряд наэмаченного К- ° С

uo

00

Т бл«па k

-Таблица 3

Вы«од 2 раэрхда ОЗУ Вшод 2 разряда ОЗУ Вывод 2 разряда ОЗУ Вьоод 2 разряда ОЗУ Вывод вида параметра

Вывод других параметров. Производится аналогично

ИнхрокоианднОе слово иВнулени триггера 3

12

п п-1-2

6

I

13

Фие.1

11

К

Фи8.2

Ш.ина 8 Устройстоа

(метна бремениГ

) . I tv.i.

Выход LмультиВи5ра-тора 4

Выход ПЗУ 2

АО

Выход бу(рерного регистра 5

Редактор Н.Ивыдкая Техред А.Кравчук

Заказ 6840/48 Тираж 704Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 133035, Москва, Ж-35, Раушская наб,, д. 4/5

Фиг.З

Корректор О.Кравцова

| Авторское свидетельство СССР № 1159435, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-15—Публикация

1985-08-08—Подача