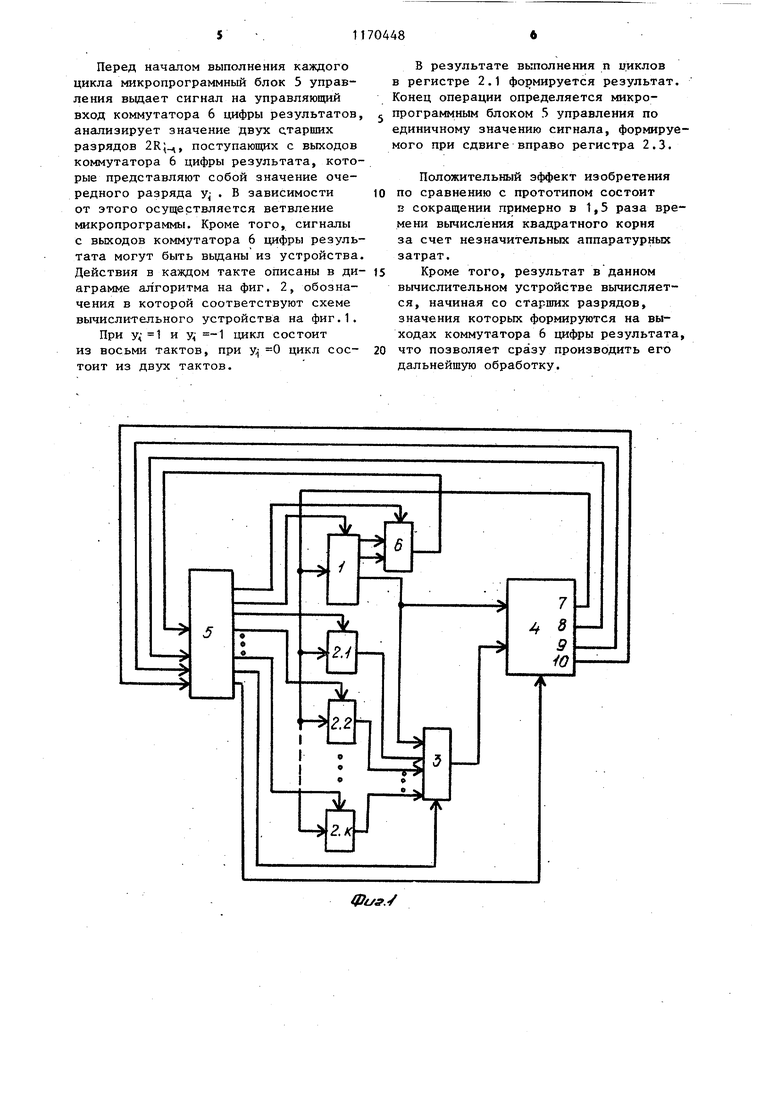

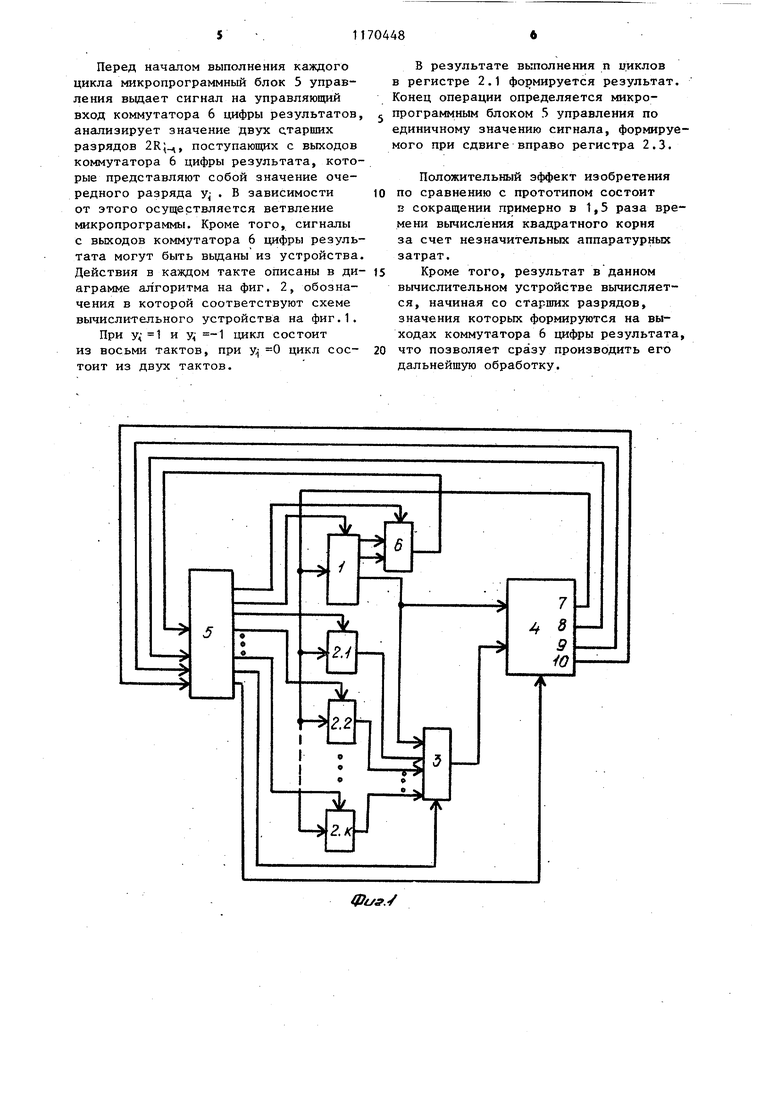

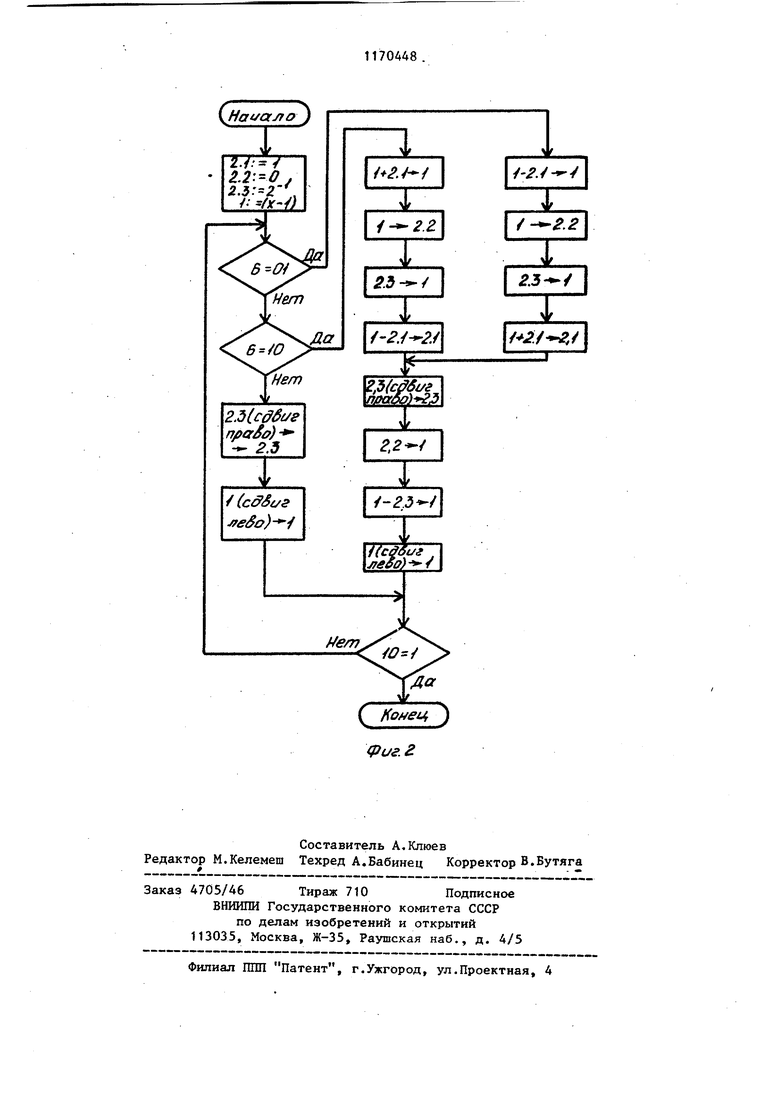

Изобретение относится к вычисли тельной технике и может быть использовано в электронных цифровых вычислительных машинах и микропроцессорах. Известно арифметическое устройство, содержащее операционные блоки, каждый из которых предназначен для выполнения определенной операции (например, умножения, сложения вычитания, деления, извлечения кор ня) . Устройство позволяет достичь высокой производительности при реа лизации вычислительных процессов 1 Однако данное устройство содержит большой объем аппаратуры. Известно арифметическое устройс во, содержащее блок управления, сумматор, регистры С2 . Однако известное устройство имеет ограниченныефункциональные возможности, так как введение новой операции требует изменения его структуры. Наиболее близким по технической сущности к изобретению является вычислительное устройство, содержащее арифметико-логический блок, регистра-аккумулятор, регистры-операнды, коммутатор и блок микропрограммного управления, причем к первой группе входов арифметико-логиче кого блока подключены выходы регист ра-акуумулятора, а к второй - выходы коммутатора, к информационным входам которого подключены выходы регистров-операндов и регистра -аккумулятора, информационные выходы арифметико-логического блока подклю чены к информационным входам регистра-аккумулятора и регистровоперандов, выходы сдвига влево и вправо, а также выход переноса ариф метико-логического блока подключены к входам логических условий микропрограммного блока управления, выхо ды операционных полей микропрограмного блока управления подключены к управляющим входам регистров-операндов, регистра аккумулятора, арифметико-логического блока и комм татора зЗ. Арифметические операции в этом устройстве реализуются путем последовательного выполнения микрооперац сдвига и суммирования (вычитания) в сответствии с микропрограммами. 8. 2 записанными в микропрограммном блоке управления. Недостатком указанного устройства является низкое быстродействие при вычислении квадратного корня. Цель изобретения - увеличение |быстродействия вычислительного устройства при выполнении операции извлечения квадратного корня. Поставленная цель достигается тем, что вычислительное устройство, содержащее регистр-аккумулятор, групцу k регистров-операндов, микропрограммный блок управления, арифметикологический блок и коммутатор, причем выход коммутатора подключен к первому информационному входу ариметикр-логического блока, выход результата которого соединен с информационными входами регистров-операндов группы, выходы которых подключены к соответствующим информационным входам коммутатора, (k+1)-й информационньй вход которого соединен с вторым информационным входом арифметико-логического блока и с выходом регистра-аккумулятора, входом под:.:люченного к выходу результата арифметико-логического блока, выходы сдвига влево, сдвига вправо и переноса которого соединены соответственно с входами с первого по третий логических условий микропрограмного блока управления, вькоды операционных полей которого с первого по (и+3)-й соединены соответственно с управляющими входами регистровоперандов группы, регистра-аккумулятора, коммутатора и арифметико-логи- ческого блока, содержит коммутатор цифры результата, причем выходы двух старших разрядов регистра-аккумулятора соединены с информационным входом коммутатора цифры результата, выход которого соединен с четвертым входом логических условий микропрограммного блока управления, (и+4)-й выход операционных полей которого соединен с управляющим входом коммутатора цифры. На фиг. 1 представлена схема вычислительного устройства; на фиг.2 диаграмма алгоритма вычисления квадратного корня. Вычислительное устройство содержит регистр-аккумулятор 1, группу 2 регистров-операндов, коммутатор 3, арифметико-логический блок 4, микропрограммный блок 5 управления, коммутатор 6 цифры результата, выходы 7 - 10 результата, сдвига влево, вправо и три переноса блока 4. Коммутатор 6 цифры результата состоит из элементов И, первые вход которых подключены к выходам регист ра-аккумулятора 1, а вторые входы к выходу микропрограммного блока 5 управления. Вычислительное устройство работает следующим образом. Арифметические операции в вычислительном устройстве осуществляются I путемпоследовательного выполнения микроопераций сдвига и суммирования (вычитания) в соответствии с микропрограммами, записанными в микропрограммном блоке 5 управления. Ветвление программ осуществляется в зависимости от значений сигналов, поступающих в определенный момент времени с выходов переноса, сдвига влево или вправо арифметико-логического блока 4. Кроме того, ветвление программ может производиться по сигналам, поступающим на входы микропрограммного блока управления 5 с выхода коммутатора 6 цифры результата. Выполнение операций сдвига, сложения, вычитания, умножения, деления и пересылки не отличается от выполнения данных операций в устройствепрототипе. Сдвиг влево или вправо в регистре-аккумуляторе 1 или в регистрахоперандах 2.1-2.k может быть осуществлен за один такт. При этом операнд вьщается из нужного регистра через коммутатор 3 на арифметикологический блок 4, где сдвигается влево или вправо, а с выхода результата арифметико-логического блока записывается в тот же регистр. Сложение (вычитание) содерзшмого двух регистров также осуществляется за один такт. При этом в качестве регистра одного операнда всегда исполь зуется регистр-аккумулятор 1. Второй операнд может находиться в любом регистре-операнде 2.1-2.k. Результат суммирования (вычитания) может быть записан только в те регистры, в которых находились операнды. Пересыпка из регистра в регистр производится за один такт. При этом информация из регистра 2.1-2.3 передается в ариф метико-логический блок 4, с выходов которого записывается в нужньй регистр.. При выполнении операции извлечения квадратного корня () вычислительное устройство работает в соответствии со следукицим алгоритмом:, 2Ro(x-1); Для ,п вьтолнить п.п. 3-5; -1 при 2R;. -2 у О при -2- « . Т 1 при 2R,- 2) ,-Y., у,.-у,- 2-- ; .. Yi Yj., - -2-Vy, - слово, содержащее только i где старших разрядов результата; у - очередная цифра результата; Ri - очередной остаток. Микропрограмма выполнения операции извлечения квадратного корня реализуется по диаграмме алгоритма фиг.2. Для вычисления необходимы, наприер, регистры 2.1, 2.2 и 2.3 для ранения - Yo,R,2. В исходном сосоянии величина 2Ro(x-1) хранится регистре-аккумуляторе 1, в регисте 2 . 1 записана 1, регистр 2.2 обулен, а в регистре 2.3 записана еличина 2 .. Соответствие значений старших азрядов 2R,-., (знакового г и старего разряда дробной части z, ) очередного разряда результата у риведено в таблице. Операция извлечения квадратного орня выполняется за п циклов. Цикл остоит из нескольких тактов, в кажом из которых выполняется только дна микрооперация.

Перед началом выполнения каждого цикла микропрограммный блок 5 управления вьщает сигнал на управляющий вход коммутатора 6 цифры результатов, анализирует значение двух старших разрядов , поступающих с выходов коммутатора 6 цифры результата, которые представляют собой значение очередного разряда yj . В зависимости от этого осуществляется ветвление микропрограммы. Кроме того, сигналы с выходов коммутатора 6 цифры результата могут быть вьщаны из устройства. Действия в каждом такте описаны в диаграмме алгоритма на фиг. 2, обозначения в которой соответствуют схеме вычислительного устройства на фиг.1.

При у 1 и у; -1 цикл состоит из восьми тактов, при у 0 цикл состоит из двух тактов.

В результате выполнения п циклов в регистре 2.1 формируется результат. Конец операции определяется микро, программным блоком 5 управления по единичному значению сигнала, формируемого при сдвиге вправо регистра 2.3.

Положительный эффект изобретения 10 по сравнению с прототипом состоит

в сокращении примерно в 1,5 раза времени вычисления квадратного корня за счет незначительных аппаратурных затрат.

15 Кроме того, результат в данном вычислительном устройстве вычисляется, начиная со старших разрядов, значения которых формируются на выходах коммутатора 6 цифры результата 20 что позволяет сразу производить его дальнейшую обработку.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Процессор | 1974 |

|

SU526902A1 |

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее регистр-аккумулятор, группу из k регистров-операндов, микропрограммный блок управления, арифметико-логический блок и коммутатор, причем выход коммутатора подключен к первому информационному входу арифметико-логического блока, выход результата которого соединен с информационными входами регистра операндов группы, выходы которых подключены к соответствующим информационным входам коммутатора, (k+1)-й информационньш вход которого соединен с вторым информационным входом арифметикологического блока и с выходом pierHCTра-аккумулятора, входом подключенного к выходу результата арифметикологического блока, выходы сдвига влево, сдвига вправо и переноса которого соединены соответственно с входами с первого по третий логических условий микропрограммного блока управления, выходы операционных полей которого с первого по ()-и соеди- нены соответственно с управлякицими входами регистров-операндов группы, i регистра-аккумулятора, коммутатора и арифметико-логического блока, отличающееся тем, что, с целью увеличения быстродействия вычислительного устройства при выполнении операции извлечения квадратного корня, оно содержит коммутатор цифры результата, причем выходы двух старпих разрядов регистра аккумулятора соединены с информационным входом коммутатора цифры результата, выход которого соединен с четветрым входом 4: 4; логических условий микропрограммного блока управления, (k+4)-й Ьыход операционных полей которого соединен 00 с управляющим входом коммутатора цифры результата.

Фа.-/

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Самофалов К.Г | |||

| и др | |||

| Электронные цифровые вычислительные машины | |||

| Киев, Вища школа, 1976, с.357 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| -Цифровые вычислительные машины и системы | |||

| М., Энергия, 1973, с | |||

| Обогреваемый отработавшими газами карбюратор для двигателей внутреннего горения | 1921 |

|

SU321A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микропроцессорные комплекты повышенного быстродействия | |||

| М., Радио и связь, 1981, с | |||

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

| Льномолотилка веялка | 1923 |

|

SU498A1 |

Авторы

Даты

1985-07-30—Публикация

1983-05-20—Подача