и вторым входом элемента И i-ro разряда, третий вход которого соединен с выходом элемента НЕ i-ro разряда, выход элемента И i-ro разряда соеди йен с входом первого элемента НЕ корректирующего узла (i-l)-ro разряда и с входом второго элемента НЕ корректирующего узла (i-l)-ro разря

1083182

да, а также с первым входом второго элемента ШШ i-ro разряда, второй вход которого соединен с выходом суммы одноразрядного сумматора того же разряда, а выход соединен с i-M разрядом выхода суммы сумматора кодов и иррациональным основанием.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов Фибоначчи | 1987 |

|

SU1532915A1 |

| Накапливающий сумматор избыточного кода | 1988 |

|

SU1603370A1 |

| Сумматор избыточного кода | 1987 |

|

SU1476460A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1983 |

|

SU1170449A1 |

| Сумматор кодов Фибоначчи | 1987 |

|

SU1411735A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

СУММАТОР КОДОВ С ИРРАДИОНАЛЬНЬМ ОСНОВАНИЕМ, содержащий в каждом разряде одноразрядньщ сумматор и корректирующий узел, который содержит два элемента И и три элемента ИЛИ, причем первый и второй входы первого элемента И корректирующего узла i-ro разряда (i 1,2,...,п) соединены с соответствующими разрядами входов первого и второго слагаемых сумматора кодов с иррациональным основанием, а его выход соединен с первым входом первого элемента ИЛИ корректирующего узла, выход которого соединен с первым входом одноразрядного сумматора того же разряда, первый вход второго, элемента И корректирующего узла соединен с выходом переноса одноразрядного сумматора (i-l)-ro разряда, первый вход второго элемента ИЛИ корректирующего узла соединен с пер-, вым входом первого элемента И корректирующего узла, а его выход подклю чан к второму входу одноразрядного сумматора того же разряда, первый вход третьего элемента ИЛИ корректирующего узла соединён с первым входом второго элемента И корректирующего узла, а его выход подключен к третьему входу одноразрядного сумматора того же разряда, отличающийся тем, что, с целью расширения области применения за счет суммирования кодов с произвольной разрядностью, в корректирующий узел введены третий элемент И, первый и второй элементы НЕ, а каждый разряд содержит дополнительно элемент НЕ, элемент И и элемент ИЛИ, первый вход третьего элемента И корI (Л ректирующего узла соединен с выходом первого элемента НЕ корректирующего узла, второй вход третьего элемента И корректирующего узла соединен с выходом второго элемента НЕ того же узла, выход третьего элемента И корректирующего узла подключен к второму входу первого элемента ИЛИ того же узла, третий вход первого элемента И корректирующего узла соединен с первым входом второго элемента И корректирующего узла, второй вход второго элемента И корректирующего узла соединен с вторым входом первого элемента И корректирующего узла и с вторым входом третьего элемента ИЛИ того же узла, выход второго элемента ИЛИ корректирующего узла .соединен с вторым входом второго элемента ИЛИ того же узла, выход перено.са одноразрядного сумматора i-ro разряда соединен с третьим входом третьего элемента И корректирующего узла (-2)-го разряда, с входом элемента НЕ (i-2)-ro разряда, первым входом элемента И (i-l)-ro разряда.

Изобретение относится к вычислительной технике и может быть исполь зовано в арифметических установках ЭВМ, осуществлякицих параллельное суммирование чисел, представленных кодах с иррациональными основаниями Известен параллельный сумматор кодов Фибоначчи, содержащий два регистра, блок нормализации, блок элементов И, блок контроля, блок определения окончания суммирования и шину управления ij . Недостатками данного сумматора являкугся сложность конструкции и низкое быстродействие. Известен также комбинационный сумматор кодов с иррациональным основанием, .содержащий в каждом разря де одноразрядный сумматор и коррект рзт)щий узел, который включает два элемента И и три элемента ИЛИ, причем первый и второй входы первого элемента И корректирующего узла i-r разряда (i 1,2,...,п) соединены с соответствующими разрядами первой и второй входных шин сумматора кодов с иррациональным основанием, а его выход - с первым входом первого элемента ИЛИ корректирующего узла, выход которого подключен к первому входу одноразрядного сумматора того же разряда, первый вход второго эле мента И корректирующего узла соедин с выходом переноса одноразрядного сумматора (i-ro)-го разряда, первый вход второго элемента ИЛИ корректирующего узла соединен ц первым входом первого -элемента И корректирующего узла, а его выход подключен к второму входу одноразрядного сумматора того же -разряда, первый вход третьего, элемента ИЛИ корректирукице го узла соединен с первым входом второго элемента И корректирующего узла, а его выход подключен к третьему входу одноразрядного сумматора того же разряда 21. Недостатком известного сумматора является ограниченность области его применения за счет невозможности суммирования кодов с произвольной разрядностьюJ так как разрядность суммируемых им кодов ограничена восемью разрядами. Цель изобретения - расширение области применения сумматора кодов с ирра1Д{ональным основанием за счет суммирования кодов с произвольной разрядностью. л, . . . Указанная цель достигается тем. что в сумматоре кодов с иррациональным основанием, содержащем в каждом разряде одноразрядный сумматор и корректирующий узел, который содержит два элемента И и три элемента ШШ, причем первый и второй входы первого элемента И корректирующего узла i-ro разряда (i 1,2,...,п) соединены с соответствующими разрядами входов первого и второго слагаемых сумматора кодов с ирращ{ональ ным основанием, а его выход соединен с первым входом первого элемента ШШ корректирующего узла, выход которого соединен с первым входом одноразрядного сумматора того же разряда первый вход второго элемента И корректирующего узла соединен с выходом переноса одноразрядного сумматора i-1) разряда, первый вход второго элемента ИЛИ корректирующего узла соединен с первым входом первого элемента И корректирующего узла, а его выход подключен к второму входу одноразрядного сумматора того же разряда, первый вход третьего элемента 1ШИ корректирующего узла соединен с первым входом второго элемента И корректирующего узла, а его выход подключен к третье му входу одноразрядного сумматора того же разрядд, з корректирующий узел введены третий элемент И, первый и второй элементы НЕ, а каждый разряд содержит дополнительно элемент НЕ, элемент И и элемент ИЛИ, первый вход третьего элемента И корректирующего узла соединен с выходом первого элемента НЕ корректирующего узла, второй вход третьего элемента И корректирующего узла соединен с вьпсодом второго элемента НЕ того же узла, выход третьего элемента И логического. корре:ктирующего узла подключен к второму входу первого элемента ИЛИ того же узла, третий вход первого элемента И корректирующего узла соединен с первым входом второго элемента И корректирующего узла, второй вход второго элемента И корректирующего узла соединён с вторым входом первого элемента И корректирующего узла и с вторым входом третьего элемента ИЛИ того же узла, выход второго элемента ИЛИ корректирующего узла соединен с вторым входом второго элемента ШШ того же узла, выход переноса одноразрядного сумматора i-ro разряда соединен с третьим входом третьего Э1Лёмента И корректирующего узла (i-2)-ro разряда, с входом элемента ЙЕ (i-2)го разряда, первым входом элемента И (i-l)-rp разряда и вторым входом

элемента И i-ro разрядка, третий вход которого соединен с выходом

элемента НЕ i-ro разряда, выход элемента И i-ro разряда соединен с входом первого элемента НЕ корректирующего узла (i-l)-ro разряда и с входом второго элемента НЕ корректирующего узла (i-l)-rO разряда, а также с первым входом второго элемента ИЛИ i-ro разряда, второй вход которого соединен с выходом суммы одноразрядного сумматора, того же разряда, а выход соединен с i-M разрядом выхода суммы сумматора кодов с иррациональным основанием.

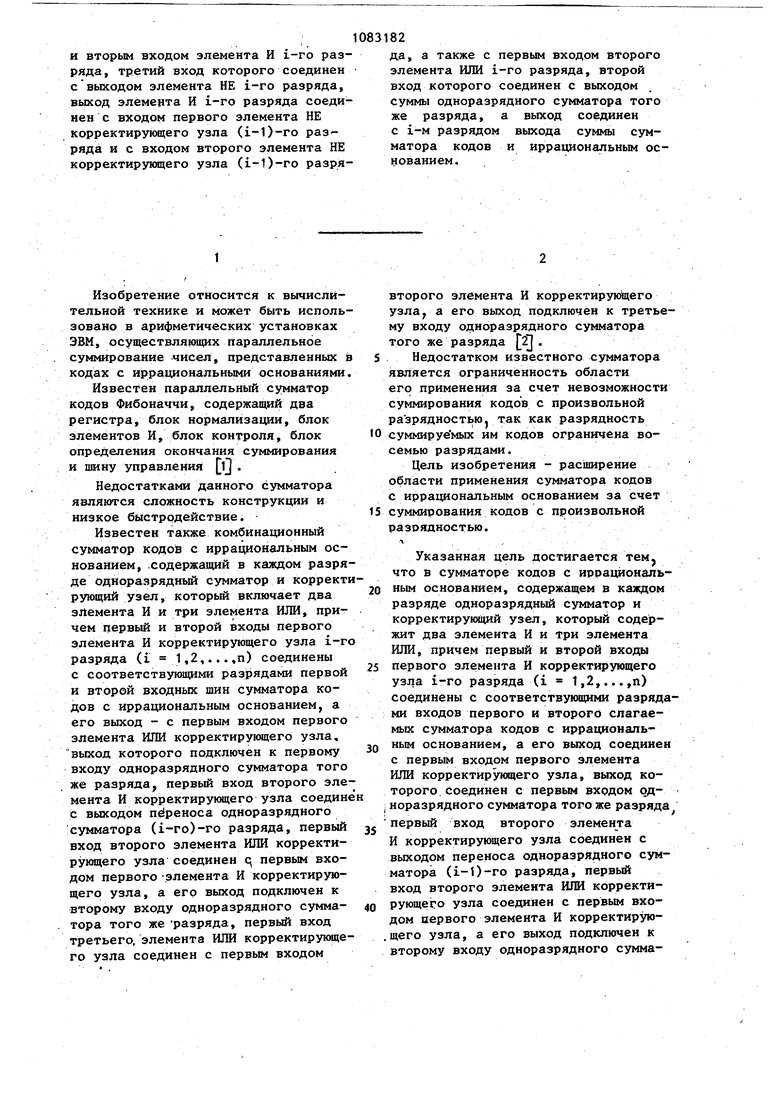

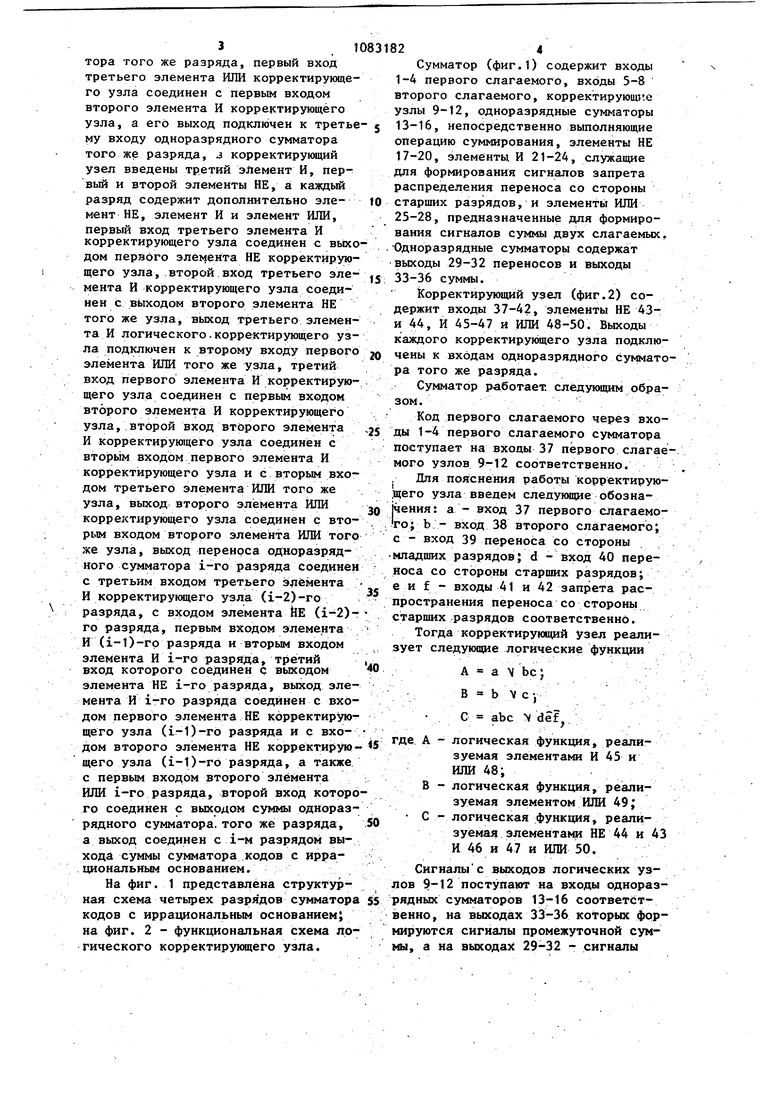

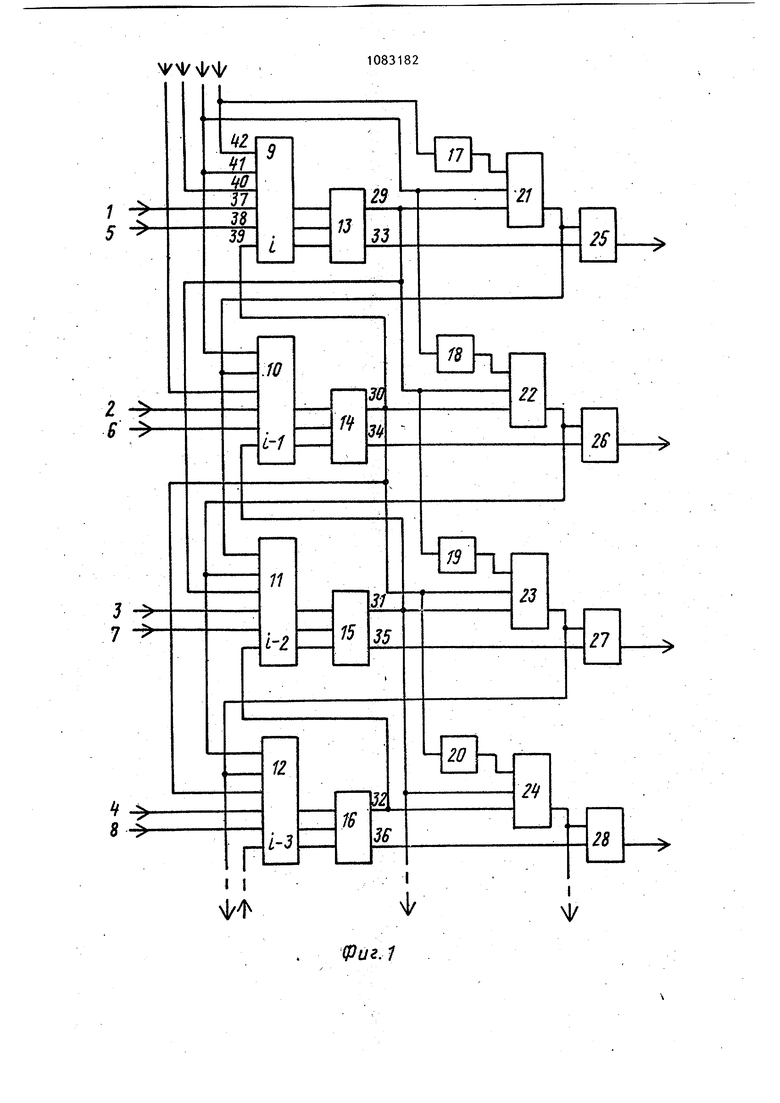

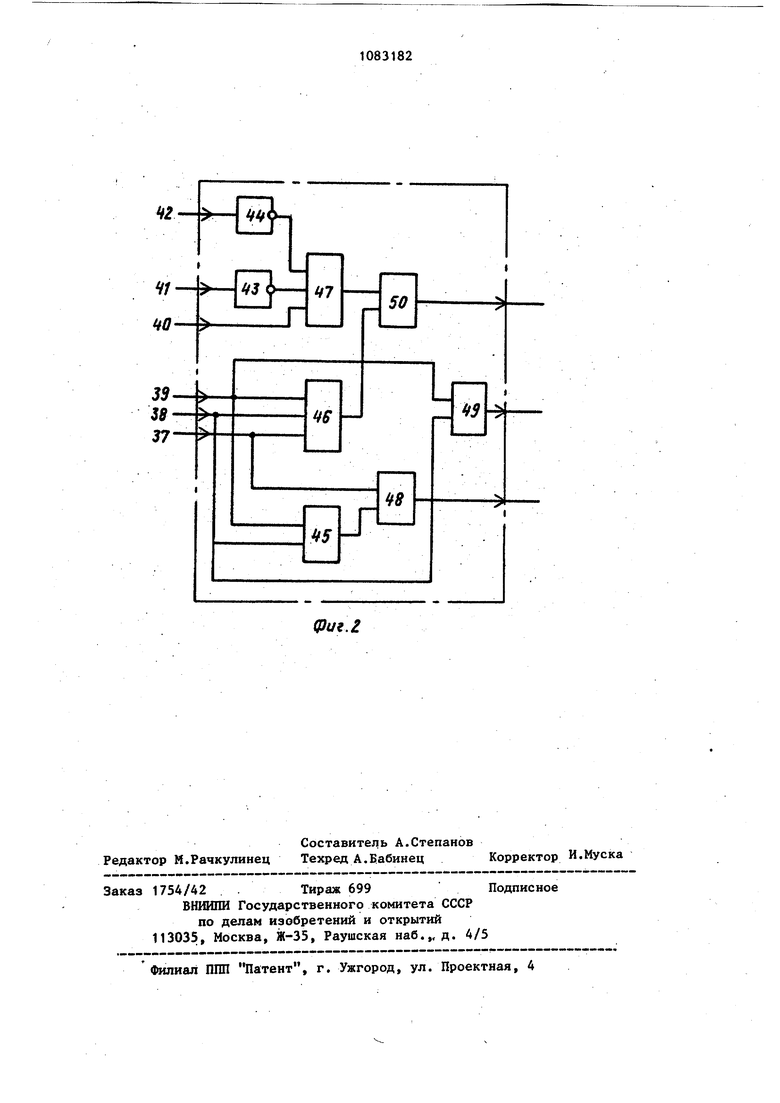

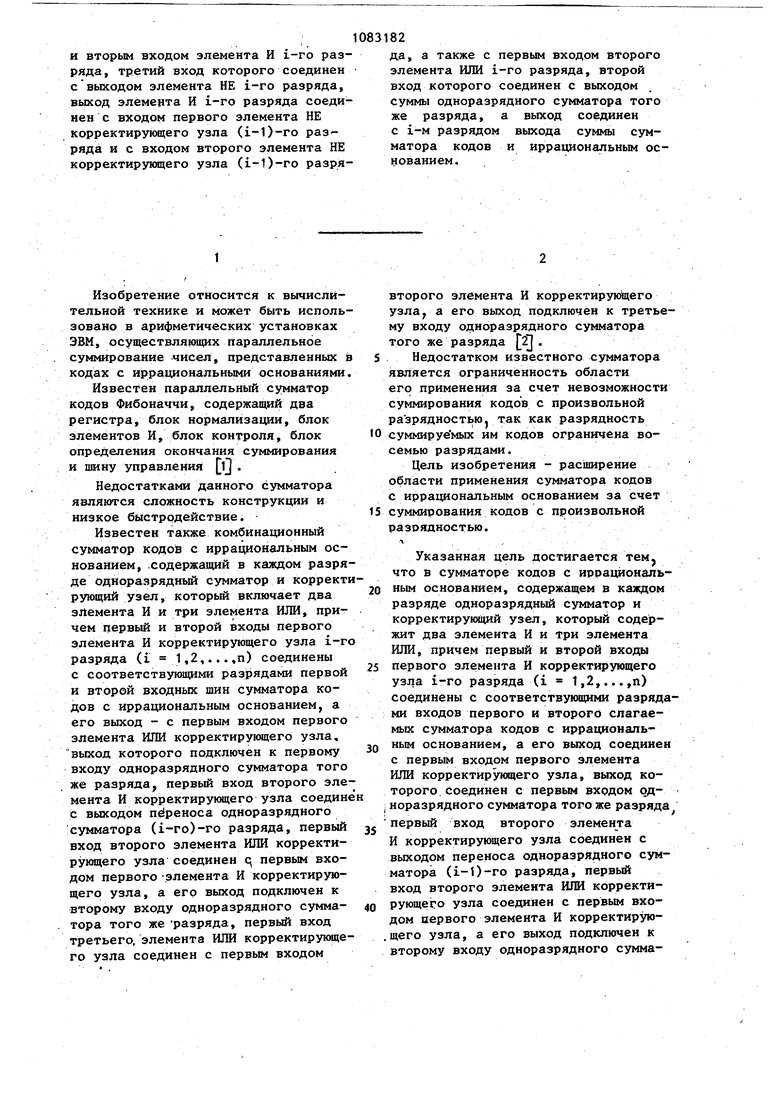

На фиг. 1 представлена структурная схема четьфех разрядов сумматора кодов с иррациональным основанием; на фиг. 2 - функциональная схема логического корректирукядего узла.

Сумматор (фиг.1) содержит входы 1-4 первого слагаемого, входы 5-8 второго слагаемого, корректирующг.с узлы 9-12, одноразрядные сумматоры 13-16, непосредственно выполняющие операцию суммирования, элементы НЕ 17-20, элементы И 21-24, служащие для формирования сигналов запрета распределения переноса со стороны старщих разрядов, и элементы ИЛИ 25-28, предназначенные для формирования сигналов суммы двух слагаемых. Одноразрядные сумматоры содержат выходы 29-32 переносов и выходы 33-36 суммы.

Корректирующий узел (фиг.2) содержит входы 37-42, элементы НЕ 43и 44, И 45-47 и ИЛИ 48-50. Выходы каждого корректирующего узла подключены к входам одноразрядного сумматора того же разряда.

Сумматор работает следукицим образом. . . , .

Код первого слагаемого через входы 1-4 первого слагаемого сумматора поступает на входы 37 первого влагаемого узлов 9-12 соответственно.

Для пояснения работы корректирующего узла введем следукмдие обозна|чения: а - вход 37 первого слагаемото; b - вход 38 второго слагаемого; с - вход 39 переноса со стороны -младших разрядов; d - вход 40 переноса со стороны старших разрядов; ей f - входы 41 и 42 запрета распространения переноса со стороны старших разрядов соответственнб.

Тогда корректирующий узел реализует следующие логические функции

А а be; В Ь V су С аЬс def,

где А - логическая функщ1я, реализуемая элементами И 45 и ИЛИ 48;

В - логическая функция, реализуемая элементом ШШ 49 J С - логическая функция, реализуемая элементами НЕ 44 и 43 И 46 и 47 и ИЛИ 50.

Сигналыс выходов логических узЛов 9-12 поступают на входы одноразрядных сумматоров 13-16 соответственно, на выходах 33-36 которых формируются сигналы промежуточной суммы, а на выходах 29-32 - сигналы

промежуточных переносов Дри возникновении сигналов переноса в двух соседних разрядах и отсутствии переноса в старшем соседнем к ним разряде на выходе элементов И 21-24 соответствуишщх разрядов появляются сигналы запретов переноса, которые запрещают поступление переноса на, вход одноразрядных сумматоров соответствующих младших разрядов.

Сигналы запретов с выходов элементов И 21-24 и сигналы с выходов 33-36 сумматоров 13-16 поступают н$. 0ХОДЫ элементов ШШ 25-28, на выходах которьи формируется окончаFejibmi результат суммирования.

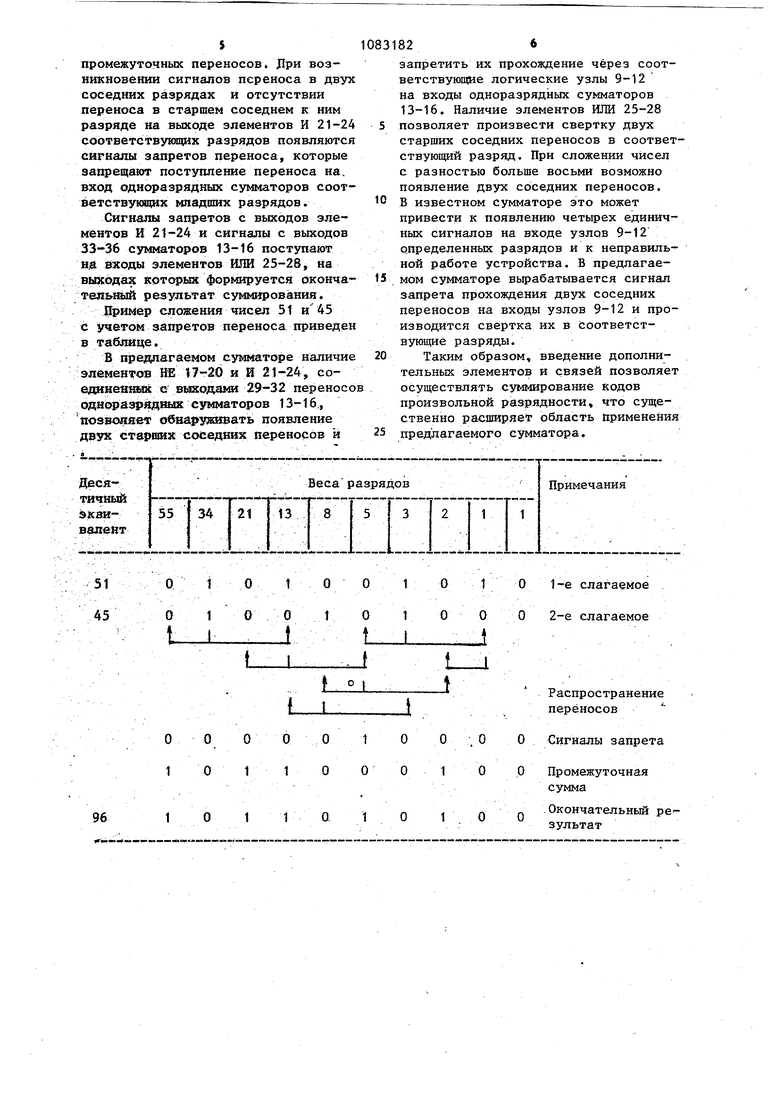

Ярямер сложения чисел 51 и 45 с учетом запретов переноса приведен

в таблице,

В предпагаемом сумматоре наличие элементов Ш 17-20 ни 21-24, соедаЕнешв с выходами 29-32 переносо одаоразря:д шх сумматоров 13-16., лозводяет обнаруживать появление двух старших соседних переносов и о о о 1 о о , о 0О 1О 1 1 о о о 10 1 О

запретить их прохождение через соответствующие логические узлы 9-12 на входы одноразрядных сумматоров 13-16. Наличие элементов ИЛИ 25-28 позволяет произвести свертку двух старших соседних переносов в соответствующий разряд. При сложении чисел с разностью больше восьми возможно появление двух соседних переносов.

в известном сумматоре это может

привести к появлению четырех единичных сигналов на входе узлов 9-12 определенных разрядов и к неправильной работе устройства. В предлагаемом сумматоре вырабатывается сигнал запрета прохождения двух соседних переносов на входы узлов 9-12 и производится свертка их в соответствующие разряды.

Таким образом, введение дополнительных элементов и связей позволяет осуществлять суммирование кодов произвольной разрядности, что существенно расширяет область применения

предлагаемого сумматора. о Сигналы запрета О Промежуточная сумма .Окончательный результат

Фиг, 1

Ь

3

ff7

e

LP

«5

риг.

50

Lrn

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Параллельный сумматор кодов фибоначчи | 1978 |

|

SU840891A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Комбинационный сумматор | 1975 |

|

SU570896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-30—Публикация

1982-12-31—Подача