первые и вторые управляющие входы преобразователей прямого кода в обратный и знака промежуточной суммы соединены соответственно с выходами третьего элемента НЕ и второго элемента 2И-ИЛИ-НЕ, выход которого соединен также с входом третьего элемента НЕ, выходы преобразователя знака промежуточной суммы и преобразователя прямого кода в обратный соединены соответственно с входами первого слагаемого комбинационного сумматора, входы второго

слагаемого которого соединены с информационными входами накапливающего сумматора, за исключением входа старшего разряда комбинационного сумматора, который соединен с входом нулевого потенциала накапливающего сумматора, выход преобразователя знака промежуточной примы соединен с выходом знака промежуточной суммы накапливающего сумматор выход переноса комбинационного сумматора соединен с входом переноса комбинационного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Функциональный преобразователь кода угла | 1978 |

|

SU716042A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Накапливающий перемножитель | 1981 |

|

SU987618A1 |

| Арифметическое устройство | 2016 |

|

RU2632411C1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

НАКАПЛИВАЮЩИЙ СУММАТОР, содержащий комбинационный сумматор, преобразователь прямого кода в обратный, преобразователь знакового разряда, выход которого является выходом знакового разряда накапливающего сумматора, первый злемент НЕ, первый элемент 2И-Ш1И-НЕ, блок памяти, инфор мационные входь разрядов которого соединены соответственно с выходами разрядов комбинационного сумматора, прямые выходы разрядов с первого по N-Й блока памяти (N - разрядность операндов) соединены соответственно с первой группой информш;йонных входов преобразователя прямого кода в обратный, инверсные выходы р азрядов с первого по N-и блока памяти соединены с второй группой информационных входов преобразователя прямого кода в обратный, выходы которого являются информационными выходами накапливающего сумматора тактовый вход которого соединен с входом синхронизации блока памяти, вход знакового разряда накапливающего сумматора соединен с входом первого элемента НЕ и с первым входом первой группы входов первого элемента 2И-ИЛИ-НЕ, первый вход второй группы входов первого элемента 2И-ИЛИ-НЕ, первый вход группы входов которого соединен с выходом первого элемента НЕ, отличающийс я тем, что, с целью сокращения количества оборудования и повышения точности, в него введены дополнительный разряд блока памяти, второй и третий элементы НЕ, второй элемент 2И-ИЛИ-НЕ и преобразователь знака промежуточной суммы, причем первый и .второй информационные входы преобразователя знакового разряда соединены соответственно с вторыми входами первой и второй групп входов первого элемента 2И-ИЛИ-НЕ и с прямым и инверсным выходами дополнительного ю разряда блока памяти, информационный (Л вход которого соединен с входом знакового разряда накапливающего сумматора, первый вход первой группы входов второго элемента 2И-ИЛИ-НЕ соединен с выходом первого элемента 2И-ИЛИ-НЕ, второй вход первой группы входов второго элемента 2И-ИЛИ-НЕ соединен с входом второго элемента НЕ и с входом режима преобразования 4 накапливающего сумматора, выход СО второго элемента НЕ соединен с пер,- to вым входом второй группы входов второго элемента 2И-ИЛИ-НЕ, второй вход второй группы входов которого соединен с первым управляющим входом преобразователя знакового разряда с первым информационным входом преобразователя знака промежуточной суммы и с прямым выходом ()ro разряда блока памяти, инверсный выход которого соединен с вторым управляющим входом преобразователя знакового разряда и с вторым информационяым входом преобразователя знака промежуточной суммы, причем

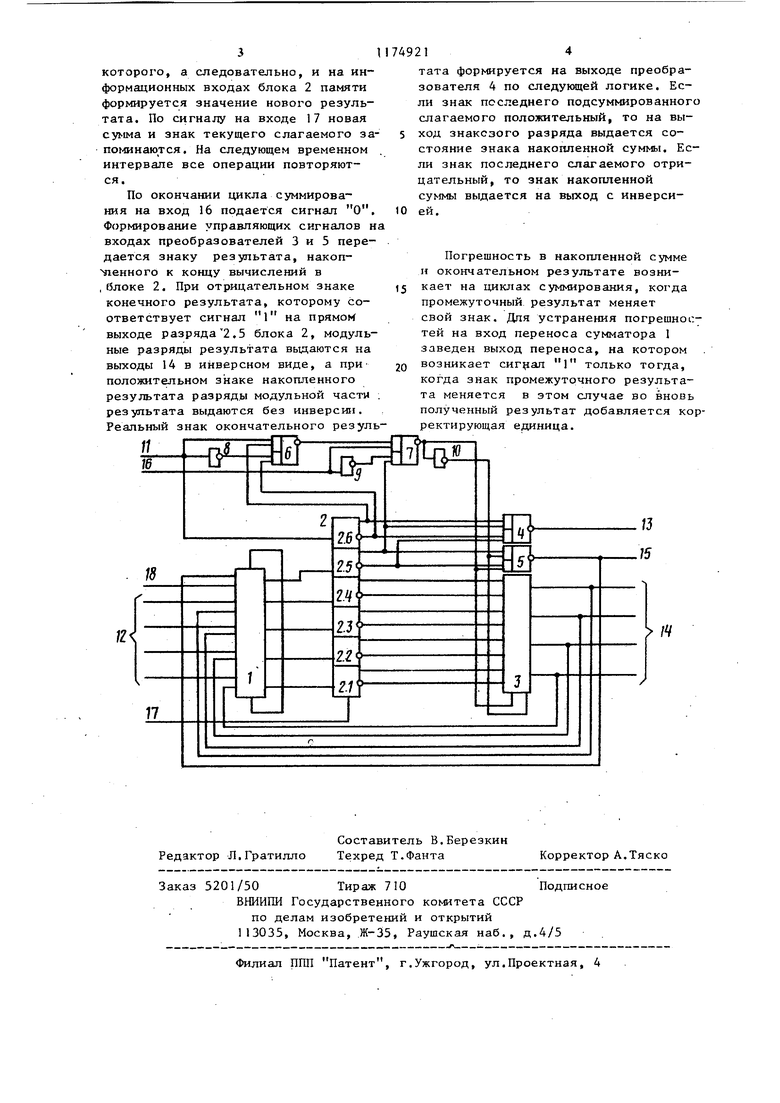

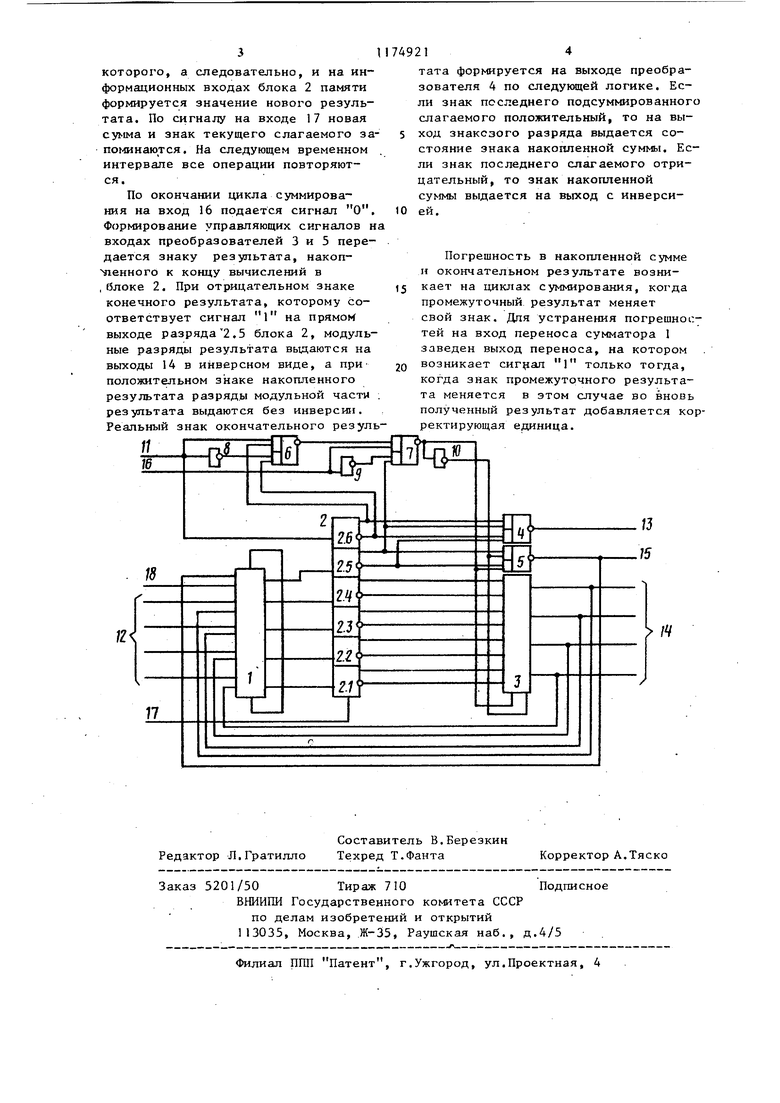

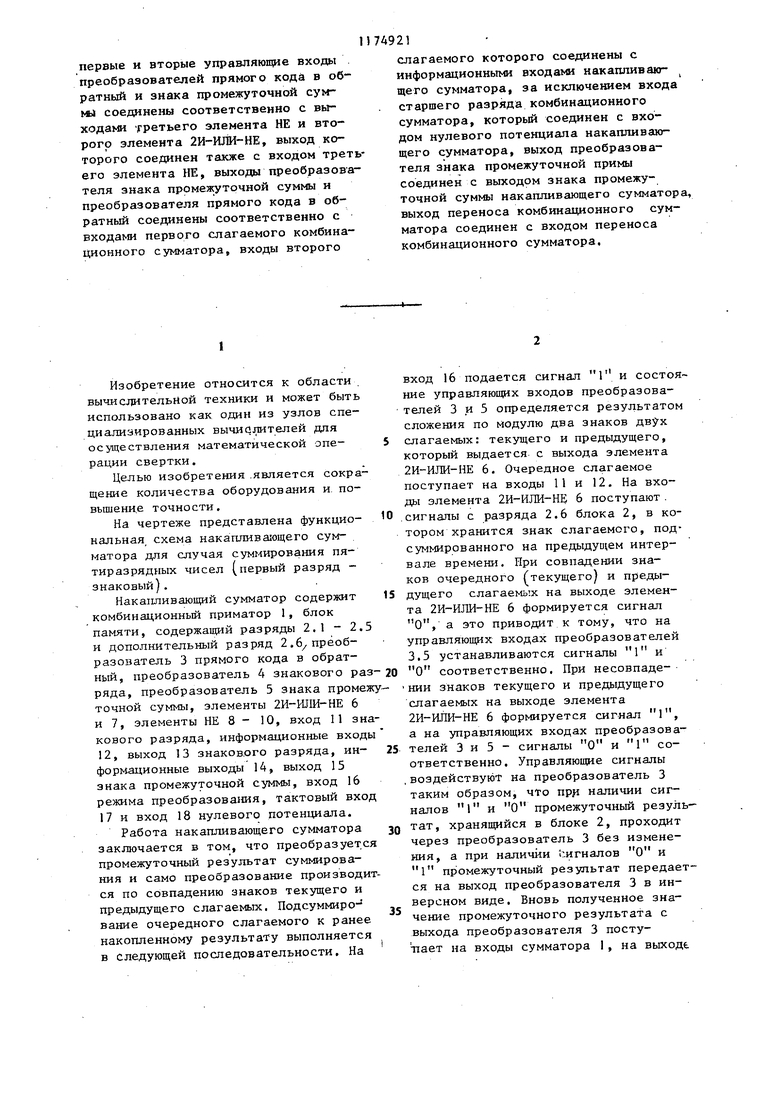

Изобретение относится к области вычислительной техники и может быть использовано как один из узлов специализированных вычислителей для осуществления математической oneрации свертки. Целью изобретения .является сокра щение количества оборудования и повышение точности. На чертеже представлена функциональная, схема накапливающего сумматора для случая суммирования пятиразрядных чисел (первый разряд знаковый). Накапливающий сумматор содержит комбинационный приматор 1, блок памяти, содержащий разряды 2.1 - 2. и дополнительный разряд 2.6 преобразователь 3 прямого кода в обратный, преобразователь 4 знакового ра ряда, преобразователь 5 знака проме точной суммы, элементы 2И-Ш1И-НЕ 6 и 7, элементы НЕ 8 - 10, вход 11 зн кового разряда, информационные вход 12, выход 13 знакового разряда, информационные выходы 14, выход 15 знака промежуточной суммы, вход 16 режима преобразова1шя, тактовый вхо 17 и вход 18 нулевого потенциала. Работа накапливающего сумматора заключается в том, что преобразуетс промежуточный результат суммирования и само преобразование производи ся по совпадению знаков текущего и предыдущего слагаемых. Подсуммирование очередного слагаемого к ранее накопленному результату выполняется в следующей последовательности. На вход 16 подается сигнал и состоя ние управляющих входов преобразователей 3 и 5 определяется результатом сложения по модулю два знаков двух слагаемых: текущего и предыдущего, который выдается с выхода элемента 2И-ИЛИ-НЕ 6. Очередное слагаемое поступает на входы 11 и 12. На входы элемента 2И-ИЛИ-НЕ 6 поступают. сигналы с разряда 2.6 блока 2, в котором хранится знак слагаемого, подсуммированного на предыдущем интервале времени. При совпадении знаков очередного (текущего) и предыдущего слагаемых на выходе элемента 2И-ИЛИ-НЕ 6 формируется сигнал О, а это приводит к тому, что на управляющих входах преобразователей 3.5 устанавливаются сигналы 1 и О соответственно. При несовпадеНИИ знаков текущего и предыдущего слагаемых на выходе элемента 2И-ИЛИ-НЕ 6 формируется сигнал 1, а на управляющих входах преобразователей 3 и 5 - сигналы О и 1 соответственно. Управляющие сигналы воздействуют на преобразователь 3 таким образом, что при наличии сигналов 1 и О промежуточный результат, хранящийся в блоке 2, проходит через преобразователь 3 без изменения, а при наличии ;:игналов О и 1 промежуточный результат передается на выход преобразователя 3 в инверсном виде. Вновь полученное значение промежуточного результата с выхода преобразователя 3 поступает на входы сумматора 1 , на выходе 3 которого, a следовательно, и на информационных входах блока 2 памяти формируется значение нового результата. По сигналу на входе 17 новая сумма и знак текущего слагаемого за по1-1инаются. На следующем временном интервале все операции повторяются. По окончании цикла суммирования на вход 16 подается сигнал О Формирование управляющих сигналов н входах преобразователей 3 и 5 передается знаку резупьтата, накопленного к концу вычислений в .блоке 2. При отрицательном знаке конечного результата, которому соответствует сигнал 1 на прямом выходе разряда2.5 блока 2, модуль ные разряды результата вьщаются на выходы 14 в инверсном виде, а приположительном знаке накопленного результата разряд.ы модульной части резупьтата выдаются без инверсии. Реальный знак окончательного резул 14 тата фор ируется на выходе преобразователя 4 по следующей логике. Если знак последнего подсуммированного слагаемого положительный, то на выход знаксзого разряда выдается состояние знака накопленной суммы. Если знак последнего слагаемого отрицательный, то знак накопленной суммы выдается на выход с инверсией. Погрешность в накопленной сумме н окончательном результате возникает на циклах суммирования, когда промежуточный результат меняет свой знак. Для устранения погрешностей на вход переноса сумматора 1 заведен выход переноса, на котором возникает 1 только тогда, когда знак промежуточного результата меняется в этом случае во вновь полученный результат добавляется корректирующая единица.

| Патент США № 3633105, кл | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Заключительный отчет | |||

| № гос | |||

| регистрации 75067249, 1977. | |||

Авторы

Даты

1985-08-23—Публикация

1984-02-03—Подача