элементов ИЛИ и первого и третьего буферных регистров, дыход четвертого элемента И соединен с входом регистра микрокоманд, выход пятого элеменг та И соединен с входами всех буферных регистров и регистра результата

выходы первой и третьей схем сравнения соединены с входами соответственно первого буферного регистра и дешифратора, выход первого элемента ИЛИ соединен с входом второго буферного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Мультимикропрограммное устройство управления | 1982 |

|

SU1042017A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

УСТРОЙСТВО для КОНТРОЛЯ ПРОГРАММ и МИКРОПРОГРАММ, содержащее триггер пуска, генератор импульсов, триггер управления, счетчик адреса, память, регистр микрокоманд, три буферных регистра, регистр результата, регистры начального и конечного адресов, первые блоки элементов ИЛИ и И, шесть элементов Hj два элемента ИЛИ, отличающ е е с я тем, что, с целью уменьшения времени контроля, в него введены три схемы сравнения, дешифратор, модификатор условий, формирователь импульса, вторые блоки элементов ИЛИ и И, причем первый вход устройства соединен с входами регистров начального и конечного адресов и через первый блок элементов ИЛИ с входом счетчика адреса, выход которого через соединенные последовательно память и регистр микрокоманд соединен с входами модификатора условий, первой схемы сравнения, второго блока элементов ИЛИ и первого элемента ИЛИ, второй вход устройства соединен с входами регистров «.;.7;ЗТ: начального и конечного адресов, второго элемента ИЛИ и через триггер пуска - с входом генератора импульсов, выходы которого соединены с входами первых пяти элементов И и счетчика адреса, выход которого соединен с входами первого и второго буферных регистров, второй и третьей схем сравнения и через первый блок элементов И - с входом второго блока элементов ИЛИ, выход которого соединен с входом тре.тьего буферного регистра, выходы всех буферных регистров через регистр результата соединены с входом дешифратора, выходы которого черезпервый и второй (Л элементы И -соединены с выходами устройства, выход регистра начально го адреса соединен с входапи первой и третьей схем сравнения и через второй блок элементов И - с входом первого блока элементов ИЛИ, выход регистра конечного адреса соединен с входом первой схемы сравнения и Од через вторую схему сравнения - с входами дешифратора и формирователя им00 Од 4 пульса, выход которого соединен с входами триггера управления, второго блока элементов И, шестого элемента И и через второй элемент ИЛИ с входом счетчика адреса, выходы триггера управления соединены с входами третьего и четвертого элемен тов И, входом первого блока элементов И, пятого элемента И и через шестой элемент И - с входом триггера пуска, выход третьего элемента И соединен с входоМвторого буферного регистра и через модификатор условий - с входами второго блока

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке систем контроля программного обеспечения

Целью изобретения является уменьшение времени контроля.

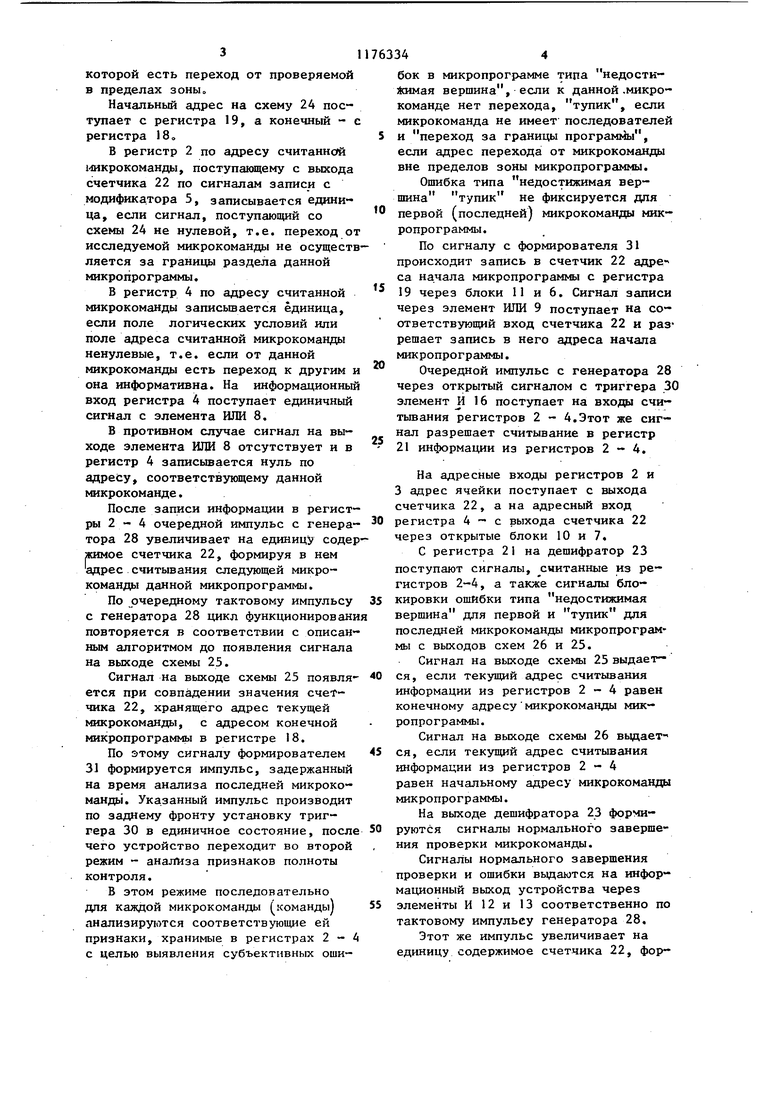

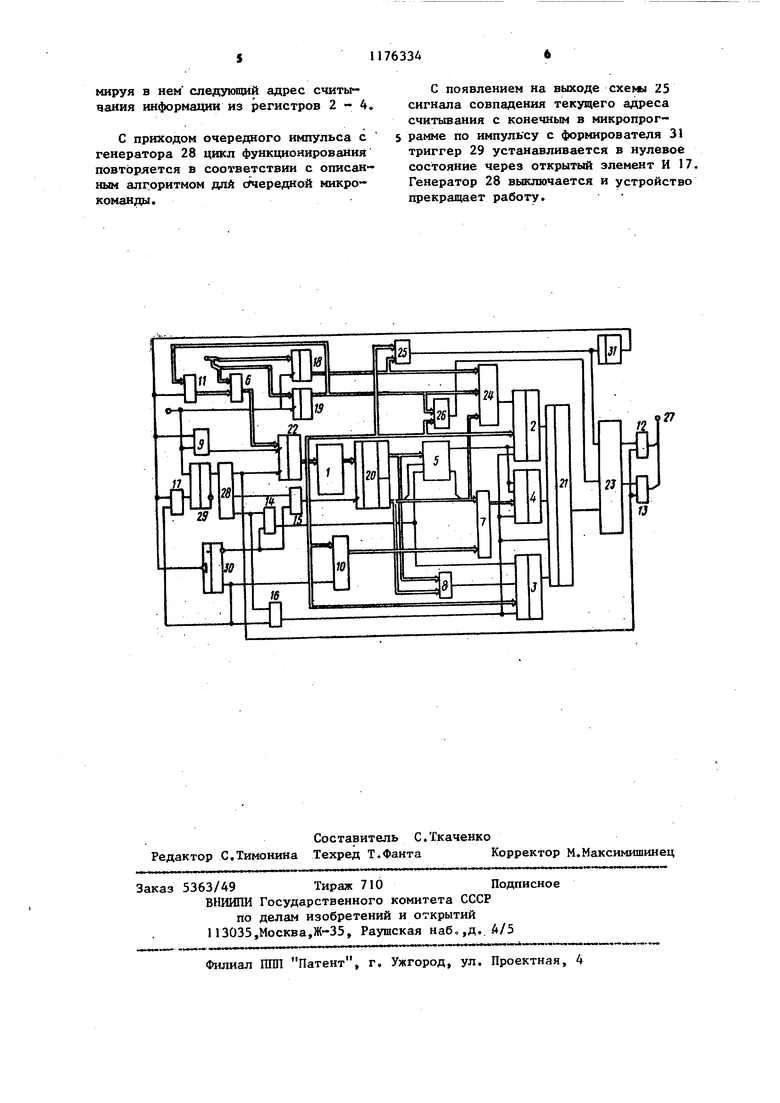

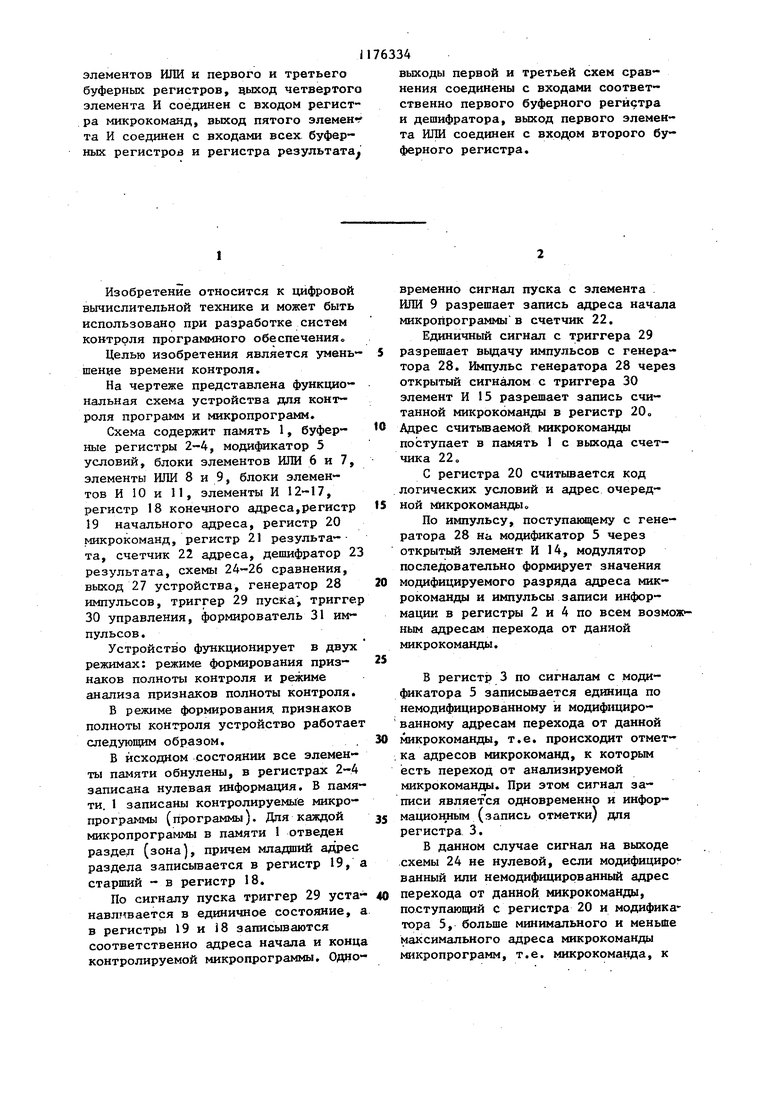

На чертеже представлена функциональная схема устройства для контроля программ и микропрограмм.

Схема содержит память 1, буферные регистры 2-4, модификатор 5 условий, блоки элементов ИЛИ 6 и 7, элементы ИЛИ 8 и 9, блоки элементов И 10 и 11, элементы И 12-17, регистр 18 конечного адреса,регистр 19 начального адреса, регистр 20 микрокоманд, регистр 21 результа- та, счетчик 22 адреса, дешифратор 23 результата, схемы 24-26 сравнения, выход 27 устройства, генератор 28 импульсов, триггер 29 пуска, триггер 30 управления, формирователь 31 импульсов.

Устройство функционирует в двух режимах: режиме формирования признаков полноты контроля и режиме анализа признаков полноты контроля,

В режиме формирования, признаков полноты контроля устройство работает следующим образом,.

В исходном состоянии все элементы памяти обнулены, в регистрах 2-4 записана нулевая информация, В памяти. 1 записаны контролируемые микропрограммы (программы). Дпя каждой микропрограммы в памяти 1 отведен раздел (зона), причем младший адрес раздела записывается в регистр 19, а старший - в регистр 18,

По сигналу пуска триггер 29 устанавливается в единичное состояние, а в регистры 19 и 18 записываются соответственно адреса начала и конца контролируемой микропрограммы. Одновременно сигнал пуска с элемента ; ИЛИ 9 разрешает запись адреса начала микропрограммыв счетчик 22,

Единичный сигнал с триггера 29 разрешает выдачу импульсов с генератора 28, Импульс генератора 28 через открытый сигнапом с триггера 30 элемент И 15 разрешает запись считанной микрокоманды в регистр 20о Адрес считьшаемой микрокоманды поступает в память 1 с выхода счетчика 22

С регистра 20 считывается код логических условий и адрес очередной микрокоманды

По импульсу, поступающему с генератора 28 на модификатор 5 через открытый элемент И 14, модулятор последовательно формирует значения модифицируемого разряда адреса микрокоманды и импульсы записи информации в регистры 2 и 4 по всем возмоным адресам перехода от данной микрокоманды,

В регистр 3 по сигналам с модификатора 5 записывается единица по немодифицированмому и модифицированному адресам перехода от данной микрокоманды, т,е, происходит отметка адресов микрокоманд, к которым есть переход от анализируемой микрокоманды. При этом сигнал записи является одновременно и информационтгм (запись отметки) для регистра 3,

В данном случае сигнал на выходе схемы 24 не нулевой, если модифициро ванный или немодифициррваниый адрес перехода от данной микрокоманды, поступающий с регистра 20 и модификатора 5, больше минимального и меньше максимального адреса микрокоманды микропрограмм, т,е, микрокоманда, к которой есть переход от проверяемой в пределах зоны Начальный адрес на схему 24 поступает с регистра 19, а конечный регистра 18, В регистр 2 по адресу считанной микрокоманды, поступающему с выхода счетчика 22 по сигналам записи с модификатора 5, записывается единица, если сигнал, поступающий со схемы 24 не нулевой, т.е. переход о исследуемой микрокоманды не осущест ляется за границы раздела данной микропрограммы. В регистр 4 по адресу считанной микрокоманды записьшается единица, если поле логических условий или поле адреса считанной микрокоманды ненулевые, т.е. если от данной микрокоманды есть переход к другим она информативна. На информационны вход регистра 4 поступает единичный сигнал с элемента ИЛИ 8. В противном случае сигнал на выходе элемента ИДИ 8 отсутствует и в регистр 4 записывается нуль по адресу, соответствующему данной микрокоманде. После записи информации в регист ры 2 - 4 очередной импульс с генера тора 28 увеличивает на единицу соде жимое счетчика 22, формируя в нем адрес считывания следующей микрокоманда данной микропрограммы. По очередному тактовому импульсу с генератора 28 цикл функционирован повторяется в соответствии с описан ным алгоритмом до появления сигнала на выходе схемы 25. Сигнал на выходе схемы 25 появля ется при совпадении значения счетчика 22, хранящего адрес текущей микрокоманды, с адресом конечной микропрограммы в регистре 18. По этому сигналу формирователем 3J формируется импульс, задержанный на время анализа последней микроко- мандь. Указанный импульс производит по заднему фронту установку триггера 30 в едршичное состояние, посл чего устройство переходит во второй режим - анализа признаков полноты контроля. В этом режиме последовательно для каждой микрокоманды (команды) анализируются соответствующие ей признаки, хранимые в регистрах 2- с целью выявления субъективных оши- бок в микропрограмме типа недости имая вершина, если к данной .микрокоманде нет перехода, тупик, если микрокоманда не имеет последователей и переход за границы программы, если адрес перехода от микрокоманды вне пределов зоны микропрограммы. Ошибка типа недостижимая вершина тупик не фиксируется для первой (последней) микрокоманды микропрограммы. По сигналу с формирователя 31 происходит запись в счетчик 22 адреса начала микропрограммы с регистра 19 через блоки 11 и 6. Сигнал записи через элемент ИЛИ 9 поступает на соответствующий вход счетчика 22 и разрешает запись в него адреса начала микропрограммы. Очередной импульс с генератора 28 через открытый сигналом с триггера 30 элемент ji 16 поступает на входы считывания регистров 2 - 4.Этот же сигнал разрешает считывание в регистр 21 информации из регистров 2-4. На адресные входы регистров 2 и 3 адрес ячейки поступает с выхода счетчика 22, а на адресный вход регистра 4 - с выхода счетчика 22 через открытые блоки 10 и 7. С регистра 21 на дешифратор 23 поступают сигналы, считанные из регистров 2-4, а также сигналы бло- кировки ошибки типа недостижимая вершина для первой и тупик для последней микрокоманды микропрограммы с выходов схем 26 и 25. Сигнал на выходе схемы 25 выдает ся, если текущий адрес считывания информации из регистров 2-4 равен конечному адресумикрокоманды микропрограммы. Сигнал на выходе схемы 26 выдает ся, если текущий адрес считывания информации из регистров 2-4 равен начальному адресу микрокоманды микропрограммы. На выходе дешифратора 23 формируются сигналы нормального завершения проверки микрокоманды. Сигналы нормального завершения проверки и ошибки выдаются на информационный выход устройства через элементы И 12 и 13 соответственно по тактовому импульсу генератора 28. Этот же импульс увеличивает на единицу содержимое счетчика 22, формируя в нем следующий адрес считывания информации из регистров 2 4.

С приходом очередного импульса с генератора 28 цикл функционирования повторяется в соответствии с описанным алгоритмом дли с чередной микрокоманды..

С появлением на выходе схемы 25 сигнала совпадения текущего адреса считывания с конечным в микропрограмме по импульсу с формирователя 31 триггер 29 устанавливается в нулевое состояние через открытый элемент И 17. Генератор 28 выключается и устройство прекращает работу.

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-30—Публикация

1983-07-11—Подача