Изобретение относится к вычислительной технике.

Целью изобретения является повьшение точности диагностирования цифровых систем.

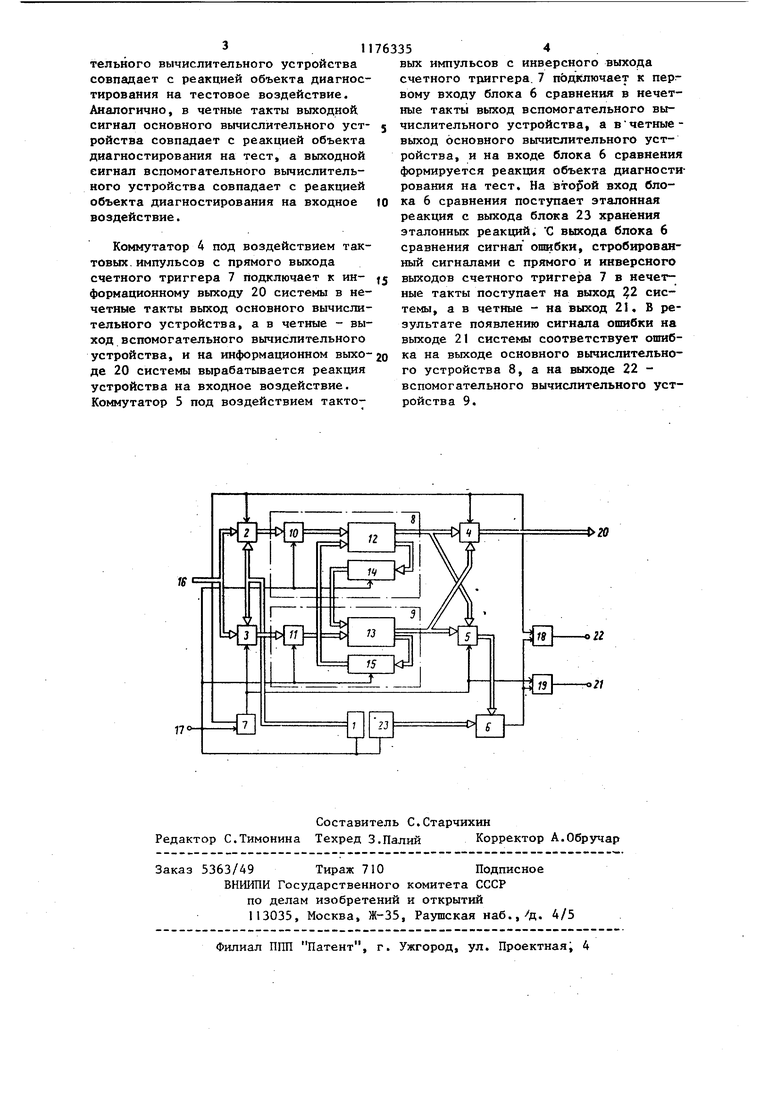

На чертеже представлена структура предлагаемойсистемы.

Система содержит генератор 1 тестовых воздействий, коммутаторы 2-5, блок 6 сравнения, счетный триггер 7, основное и вспомогательное вычислительные устройства 8 и 9 соответственно, каждое из которых состоит из блоков буферной памяти 10 и И соответственно, арифметико-логического блока 12 и 13 соответственно, запоминающего блока 14 и 15 соответственно Кроме того, она содержит информационный вход 16, синхровход 17, первый и второй элементы И 18 и 19, информационный выход 20, выходы 21 и 22 сигнала ошибки основного и вспомогательного вычислительных устройств соответственно, блок 23 хранения эталонных реакций.

Система работает следующим образом.

Счетный триггер вырабатьюает управляющий импульс, на своих прямом и инверсном выходах, передний (задний) фронт которого совпадает с нечетным (четным) и четным (нечетным) тактовым импульсом соответственно.

Тактовые импульсы поступают с синхровхода 17 системы и обеспечивают синхронность блоков буферной памяти 10 и 11 и запоминающих блоков 14 и 15 основного и вспомогательногб вычислительных устройств 8 и 9, а также генератора 1 тестовых воздейстВИЙ и блока 23 хранения эталонных реакций.

При наличии на управляющем входе каждого из коммутаторов управляюще:го импульса на выход коммутатора поступает сигнал с первого из его входов, а при отсутствии - со второго. В нечетных такх-ах сигнал с информационного входа системы через коммутатор 2 поступает на вход основного вспомогательного устройства, а тестовый сигнал с выхода генератора 1 тестовых воздействий через коммутатор ,3 - на вход вспомогательного вычислительного устройства 9 и фиксируетс в блоках памяти 10 и 11 соответств нно. В результате сигналы на первом и втором выходах арифметическо-логического блока 12, в нечетном такте определяются сигналами на информационном входе 16 системы и выходе запоминающего блока 15, а сигналы на первом и втором выходах арифметико-логического блока 13 сигналами на выходе генератора 1 тес товых воздействий и выходе запоминающего блока 14. В четном такте сиг нал с информационного входа 16 системы через коммутатор 3 подключается ко входу вспомогательного вычислительного устройства 9, а тестовый сигнал с выхода генератора 1 через коммутатор 2 подключается ко входу основного вычислительного устройства 8 и фиксируются в блоках буферной памяти 11 и 10 соответственно. В результате сигналы на первом и втором выходах арифметико-логического блока .13 в четном такте определяются сигналами на информационном входе 16 системы и выходе запоминающего устройства 14, а сигналы на первом и втором выходах арифметико-логического блока 12 - сигналом тестовых воздействий на выходе генератора 1 и сигналом на выходе запоминающего блока 15 С приходом каждого тактового импульса синхровхода 17 системы осуществляется запись сигналов со вторых вькодов арифметико-логических блоков 12 и 13 в запоминающие блоки 14 и 15 соответственно. Таким образом, в нечетном такте состояние запоминающих блоков 14 и 15 определяется состоянием основного и вспомогательного вычислительных устройств 8 и 9 в предьщущем (четном) такте, в которые указанные системы переходят под воздействием сигналов с выхода генератора 1 тестовых воздействий информационной системы и входа 16 системы соответственно. В четном такте состояние запоминакмцих блоков 14 и 15 определяется состоянием основного и вспомогательного вычислительных устройств в предыдущем (нечетном) такте в которые указанные системы переходя

под воздействие сигналов с информационного входа 16 системы и с выхода генератора 1 тестовых воздействий. В результате в нечетные такты выходной сигнал основного вычислительного устройства совпадает с реакцией объекта диагностирования на входное воздействие, поступающее с информационного входа 16, а выходной сигнал вспомога3nтельного вычислительного устройства совпадает с реакцией объекта диагностирования на тестовое воздействие. Аналогично, в четные такты выходной сигнал основного вычислительного устройства совпадает с реакцией объекта диагностирования на тест, а выходной сигнал вспомогательного вычислительного устройства совпадает с реакцией объекта диагностирования на входное воздействие. Коммутатор 4 под воздействием тактовых, импульсов с прямого выхода счетного триггера 7 подключает к информационному выходу 20 системы в нечетные такты выход основного вычислительного устройства, а в четные - выход вспомогательного вычислительного устройства, и на информационном выходе 20 системы вырабатывается реакция устройства на входное воздействие. Коммутатор 5 под воздействием такто354вых импульсов с инверсного выхода счетного триггера. 7 пЬдключает к первому входу блока 6 сравнения в нечетные такть выход вспомогательного вычислительного устройства, а вчетныевыход основного вычислительного устройства, и на входе блока 6 сравнения формируется реакция объекта диагностирования на тест. На второй вход блока 6 сравнения поступает эталонная реакция с выхода блока 23 хранения эталонных реакций, С выхода блока 6 сравнения сигнал ошибки, стробированный сигналами с прямого и инверсного выходов счетного триггера 7 в нечетные такты поступает на выход 2 системы, а в четные - на выход 21, В результате появлению сигнала ошибки на выходе 21 системы соответствует ошибка на выходе основного вычислительного устройства 8, а на выходе 22 вспомогательного вычислительного устройства 9.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для сдвига | 1975 |

|

SU723570A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| Устройство для сдвига информации | 1979 |

|

SU1005034A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1809398A1 |

| ОБНАРУЖИТЕЛЬ ФАЗОКОДИРОВАННЫХ СИГНАЛОВ | 1990 |

|

SU1818985A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Устройство для контроля схем сравнения | 1985 |

|

SU1297062A1 |

ЦИФРОВАЯ СИСТЕМА С ТЕСТОВЫМ ДИАГНОСТИРОВАНИЕМ, содержащая генера тор тестовых воздействий, блок хранения эталонных реакций, блок сравнения, основное и вспомогательное вычислительные устройства, каждое из которых состоит из блока буферной памяти, арифметико-логического блока и запоминающего блока, причем выход блока хранения эталонных реакций соединен с первым входом блока сравнения, первый информационный вход каждого арифметико-логического блока .соединен с выходом соответствуняцего блока буферной памяти, первый выход каждого арифметико-логического блока - с информационным входом соответствующего запоминающего блока, входы синхронизации блоков буферной памяти запоминающих блоков, генератора тестовых воздействий и блока хранения эталонных реакций соединены с синхровходом системы, отличающаяс я тем, что, с целью повышения точности диагностирования цифровых систем, введены счетный триггер, два элемента И и четыре коммутатора, причем первые информационные входы первого И второго коммутаторов соединены с информационным входом системы, «торые информационные входы первого t и второго коммутаторов соединены с выходом генератора тестовых воздействий, а выходы первого и второго коммутаторов - соответственно с информационными входами блоков буферной памяти основного и вспомогательного вычислительных устройств, первые информационные входы третьего и четвертого коммутаторов соединены со вторым выходом арифметико-логического блока основного вычислительного устройства, а вторые информационные входы - с цторьм выходом арифметикологического блока вспомогательного вычислительного устройства, выходы третьего и четвертого коммутаторов (Л соединены соответственно с информационным выходом системы и со вторым входом блока сравнения, управляющие входы первого и третьего коммутаторов соединены с прямым выходом счетного триггера, а управляющие входы второго и четвертого коммутаторов с инверсным выходом счетного триггеОд ра, вторые информационные входы со со ел арифметико-логических блоков основного и вспомогательного вычислительнь1х устройств соединены с выходами запоминающих блоков вспомогательного и основного вычислительных устройств соответственно, первые входы элементов И соединены с выходами блока . сравнения, вторые входы первого и второго злементов И соединены с прямым и инверсным выходами счетного триггера соответственно,а выходы первого и второго элементов И являются выходами ми сигналов ошибок вспомогательного и основного вычислительных устройств соот ветственно,вход счетного триггера соединен с синхровходом системы.

Авторы

Даты

1985-08-30—Публикация

1983-07-27—Подача