fO

15

20

25

11297062

Изобретение относится к автоматие и вычислительной технике и может ыть использовано при реализации редств тестового диагностирования иповых блоков дискретной техники.

Целью изобретения является повышеие достоверности контроля.

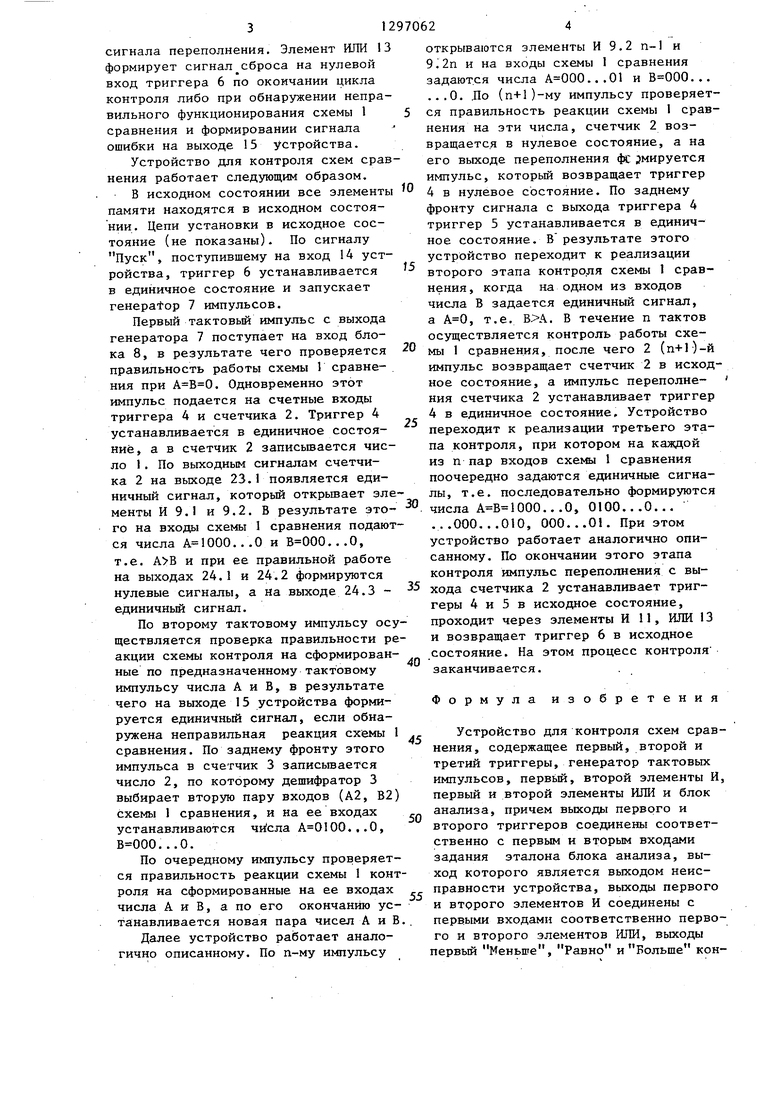

На чертеже приведена функциональ- ая схема устройства для контроля хем сравнения.

Предлагаемое устройство содержит онтролируемую схему 1 сравнения, четчик 2, дешифратор 3, первый 4, торой 5 и третий 6 триггеры, генеатор 7 тактовых импульсов, блок 8 иксации ошибки, группу элементов 9.1-9.2п, первый JO и второй 11 элементы И, первый 12 и второй 13 элементы ИЛИ, вход 14 и выход 15.Блок 8 содержит первый, второй, третий и четвертый элементы И 16-19, коммутатор 20, элемент 21 равнозначности, элемент ШШ-НЕ 22. Выхода 23.1-23.П, выходы 24.1 Меньше, выход 24.2 Равно, выход 24.3 Больше - выходы контролируемой схемы 1 сравнения.

Рассмотрим назначение элементов устройства для контроля схем сравнения.

Схема 1 сравнения является объектом контроля. Она предназначена для сравнения п-разрядных двоичных чисел и формирования по результатам сравнения одного из трех возможных сигналов: - на выходе 24.1; - на выходе 24.2; - на выходе 24.3. При правильной работе схемы 1 сравнения на ее выходах должен присутствовать один и только один единичный сигнал.

Счетчик 2 предназначен для задания номеров проверяемых пар входов схемы 1 сравнения. Он переключается в следующее состояние по заднему фронту тактового импульса, поступающего на его счетный вход. С информационного выхода счетчика I снимается код за- писа:нного в нем числа, а с выхода переполнения - импульс переполнения, свидетельствующий об окончании перебора всех 12 пар входов проверяемой схемы 1 сравнения. При этом счетчик возвращается в исходное состояние.

Дешифратор 3 в соответствии с поступающими на его вход кодами производит выбор проверяемой пары входов схемы 1 сравнения. Единичный сигнал, сформированньй на одном из

30

35

40

45

50

55

е

5

0

5

0

5

0

5

0

5

его выходов, открывает соответствующую пару элементов И 9.1 и 9.(i+l), где i - нечетное число, в результате чего на проверяемую пару входов схемы 1 сравнения через эти элементы подаются испытательные сигналы, формируемые с помощью триггеров 4 и 5. Триггеры 4 и 5 формируют последовательность испытательных сигналов, подаваемых на одноименные входы проверяемой схемы 1 сравнения. Оба триггера переключаются по заднему фронту поступающих на их входы импульсов.

Триггер 6 предназначен для пуска- останова устройства. Он переключается в единичное состояние по сигналу Пуск, поступающему на вход 14 устройства. Возврат триггера 6 в исходное состояние осуществляется по сигналу, формируемому на его вход R с помощью элемента ИЛИ 13. Своим выходным сигналом триггер 6 управляет запуском и остановом генератора 7.

Генератор 7 тактовых импульсов предназначен для формирования последовательности импульсов, управляющих работой устройства. Импульсы на его выходе формируются только при единичном сигнале на его входе.

Блок 8 фиксации ошибки предназначен для определения правильности работы схемы 1 сравнения и формирования сигнала ошибки. Контроль работы схемы 1 сравнения заключается в проверке соответствия выходных сигналов схемы I сравнения испытательным сигналом, формируемым триггерами 4 и 5.

Группа элементов И 9,1-9.2п предназначена для формирования кодов числа на входы схемы 1 сравнения, на которых осуществляется проверка ее функционирования.

Элемент И 10 5гправляет переключением триггера 4. Он пропускает тактовый импульс на вход триггера 4 только тогда, когда триггеры 4 и 5 находятся в исходном состоянии. Элемент И 1 1 пр€;дназначен для формирования, сигнала на останов триггера 6 в конце цикла контроля, когда триггеры 4 и 5 находятся в единичном состоянии, а 2 сформировал сигнал переполнения.

Элемент ИЛИ 12 формирует сигналы на счетный вход триггера 4 в процессе контроля схемы 1 сравнения, а также в конце очередного этапа контроля при формировании счетчиком 2

сигнала переполнения. Элемент ИЛИ 13 формирует сигнал сброса на нулевой вход триггера 6 по окончании цикла контроля либо при обнаружении неправильного функционирования схемы 1 сравнения и формировании сигнала ошибки на выходе 15 устройства.

Устройство для контроля схем сравнения работает следующим образом.

открываются элементы И 9,2 n-l и 9.2п и на входы схемы 1 сравнения задаются числа ...01 и .. ...0. .По (п+1)-му импульсу проверяе ся правильность реакции схемы 1 срав нения на эти числа, счетчик 2 возвращается в нулевое состояние, а на его выходе переполнения фс рмируется импульс, который возвращает триггер

В исходном состоянии все элементы в нулевое состояние. По заднему

памяти находятся в исходном состоя-фронту сигнала с выхода триггера 4

нии. Цепи установки в исходное сое-триггер 5 устанавливается в единичтояние (не показаны). По сигналуное состояние. В результате этого

Пуск, поступившему на вход 14 уст-устройство переходит к реализации

20

ройства, триггер 6 устанавливается - в единичное состояние и запускает reHepatop 7 импульсов.

Первый тактовый импульс с выхода генератора 7 поступает на вход блока 8, в результате чего проверяется правильность работы схемы 1 сравнения при . Одновременно этот импульс подается на счетные входы триггера 4 и счетчика 2. Триггер 4 устанавливается в единичное состояние, а в счетчик 2 записьюается число 1. По выходным сигналам счетчика 2 на выходе 23.1 появляется единичный сигнал, который открьшает элементы И 9.1 и 9.2. В результате это- числа ...0, 0100...0... го на входы схемы I сравнения подают- ...000...010, 000...01. При этом

25

второго этапа контроля схемы 1 сравнения, когда на одном из входов числа В задается единичный сигнал, а , т.е. . В течение п тактов осуществляется контроль работы схемы 1 сравнения, после чего 2 (п+Г)-й импульс возвращает счетчик 2 в исход ное состояние, а импульс переполне- кия счетчика 2 устанавливает триггер 4 в единичное состояние. Устройство переходит к реализации третьего этапа контроля, при котором на каждой из п пар входов cxebcj 1 сравнения поочередно задаются единичные сигналы, т.е. последовательно формируются

ся числа ...0 и ...0, т.е. и при ее правильной работе на выходах 24.1 и 24.2 формируются нулевые сигналы, а на выходе 24.3 - единичный сигнал.

По второму тактовому импульсу осуществляется проверка правильности реакции схемы контроля на сформированные по предназначенному тактовому импульсу числа А и В, в результате чего на выходе 15 устройства формируется единичный сигнал, если обнаружена неправильная реакция схемы 1 сравнения. По заднему фронту этого импульса в счетчик 3 записьгоается число 2, по которому дешифратор 3 выбирает вторую пару входов (А2, В2) схемы 1 сравнения, и на ее входах

устанавливаются числа .,.0, ...0.

По очередному импульсу проверяется правильность реакции схемы 1 контроля на сформированные на ее входах числа А и В, а по его окончанию устанавливается новая пара чисел А и В. ,

Далее устройство работает аналогично описанному. По п-му импульсу

открываются элементы И 9,2 n-l и 9.2п и на входы схемы 1 сравнения задаются числа ...01 и ... ...0. .По (п+1)-му импульсу проверяется правильность реакции схемы 1 сравнения на эти числа, счетчик 2 возвращается в нулевое состояние, а на его выходе переполнения фс рмируется импульс, который возвращает триггер

в нулевое состояние. По заднему

числа ...0, 0100...0... ...000...010, 000...01. При этом

второго этапа контроля схемы 1 сравнения, когда на одном из входов числа В задается единичный сигнал, а , т.е. . В течение п тактов осуществляется контроль работы схемы 1 сравнения, после чего 2 (п+Г)-й импульс возвращает счетчик 2 в исходное состояние, а импульс переполне- кия счетчика 2 устанавливает триггер 4 в единичное состояние. Устройство переходит к реализации третьего этапа контроля, при котором на каждой из п пар входов cxebcj 1 сравнения поочередно задаются единичные сигналы, т.е. последовательно формируются

устройство работает аналогично описанному. По окончании этого этапа контроля импульс переполнения с выхода счетчика 2 устанавливает триггеры 4 и 5 в исходное состояние, проходит через элементы И 11, ИЛИ 13 и возвращает триггер 6 в исходное состояние. На этом процесс контроля заканчивается.

Формула изобретения

Устройство для контроля схем сравнения, содержащее первый, второй и третий триггеры, генератор тактовых импульсов, первьй, второй элементы И, первый и второй элементы ИЛИ и блок анализа, причем выходы первого и второго триггеров соединены соответственно с первым и вторым задания эталона блока анализа, выход которого является выходом неисправности устройства, выходы первого и второго элементов И соединены с первыми входами соответственно первого и второго элементов ИЛИ, выходы первый Меньше, Равно и Больше кон

тролируемой сравнения соединены соответственно с первым, вторым и третьим информационными входами блока анализа, о, тли чающееся тем, что, с целью повышения достовер- нести контроля, в устройство введены счетчик, дешифратор и группа элементов И, причем вход пуска устройства соединен с единичным входом третьего триггера, выход которого соединен с входом запуска генератора тактовых импульсов, выход генератора тактовых импульсов соединен с входом синхронизации блока анализа, прямым входом первого элемента И и счетным входом счетчика, выход переполнения которого соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента И, выход первого элемента ИЛИ соединен с счетным входом пер- вого триггера, прямой выход которого соединен с первым входом каждого нечетного элемента И группы, с первым инверсным входом первого элемента И, с вторым входом второго элемента И и с счетным входом второго триггера, прямой выход которого соединен с первыми входами каждого четного элемента И группы, с вторым инверсным входом первого элемента И и с третьим входом второго элемента И, выходы .счетчика соединены с входами дешифратора, i-й выход дешифратора (,n) соединен с вторым входом i-ro элемента И группы, выход блока анализа яв- ляется контрольньм выходом устройства и соединен с вторым входом второго элемента ИЛИ, выход которого соединен

Составитель И. Сафронова Редактор Т. Ларфенова Техред Л. Сердюков а Корректор И. Муска

Заказ 783/53Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4.

0 5

5

0

с входом установки нуля третьего триггера, блок анализа содержит первый, второй, третий и четвертый элементы И, коммутатор, элемент равнозначности и элемент ШШ-НЕ, причем первый информационный вход блока соединен с первыми инверсньпми входами первого и второго элементов И и с первым входом третьего элемента И, второй информационный вход блока соединен с прямым входом первого элемента И и управляющим входом компаратора, выход которого соединен с первым входом элемента ИЛИ-НЕ, первый и второй входы задания эталона блока соединены соответственно с первым и вторым, входами элемента равнозначности, выход которого соединен с первым входом четвертого элемента И, первый и второй входы задания эталонов соединены: соответственно с вторым входом второго эталона И и с вторым инверсным входом третьего элемента И, выход которого соединен с первым инверсным входом коммутатора, второй вход задания эталона блока соединен с вторым входом третьего элемента И и с вторым инверсным входом второго элемента И, выход которого соединен с вторым информационным входом коммутатора, выход первого элемента И соединен с вторым входом четвертого элемента И, выход которого соединен с вторым входом элемента ШШ-НЕ, третий информационный вход блока соединен с инверсным входом элемента ИЛИ- НЕ , выход которого является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля схем сравнения | 1986 |

|

SU1383367A1 |

| Устройство для контроля схем сравнения | 1979 |

|

SU960822A1 |

| Устройство для программного управления | 1990 |

|

SU1784939A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Счетчик | 1987 |

|

SU1437993A1 |

| Устройство для проверки схем сравнения двоичных чисел | 1973 |

|

SU481898A1 |

| Устройство для формирования тестовой последовательности | 1986 |

|

SU1529293A1 |

| Устройство для формирования тестовых воздействий | 1988 |

|

SU1552187A1 |

| Устройство для контроля времени выполнения программ | 1984 |

|

SU1176336A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации средств тестового диагностирования типовьпс блоков дискретной техники. Цель изобретения - повышение достоверности контроля. Сущность изобретения заключается в следующем: повышение достоверности контроля путем исключения из схемы сравнения сдвигающих регистров и блокировка вьщачи ложных сигналов ошибки на выходе устройства. Это достигается за счет введения счетчика 2 и его связей, что позволяет осуществлять перебор проверяемых пар входов схемы, введения дешифратора 3 и его связей, что позволяет производить выбор проверяемой пары кодов, введения группы элементов И 9.1-9.2 и ее связей, что обеспечивает формирование кодов чисел на входах схем сравнения, введения новых связей для первого и второго элементов И и ИЛИ, что позволяет управлять работой схемы, и введения новых связей для генератора импульсов, что позволяет исключить формирование ложных сигналов ощибки и синхронизировать работу схемы. 1 ил. « (Л ю со О О) ю

| Устройство для проверки схем сравнения | 1976 |

|

SU583436A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля схем сравнения | 1978 |

|

SU767767A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-22—Подача