1

Изобретение относится к области вычислительной техники и может быть применено в процессорах малой и средней производительности.

Известно устройство, содержащее блок управления, память, регистры, триггеры, элементы ИЛИ, И l.

Однако, оно имеет недостаточное быстро деист ви е.

Наиболее близким по технической сущности к предложенному является устройство, содержащее узел контроля, первый и второй входы которого соединены соответственно с первым входом устройства и первым выходом блока микропрограммного управления, второй и третий выходы которого соединены соответственно с первыми выходом устройства и входом локальной памяти, первый и второй выходы которой соединены соответственно со вторым выходом устройства и третьим входом узла контроля, а второй вход локальной памяти является вторым входом устройства, узел прерываний, первый выХОД которого соединен с первым входом блока микропрограммного управления 2.

Однако это устройство также имеет низкое быстродействие при выполнении процедуры восстановления после обнаружения ошибки.

Цель изобретения - повышения быстродействия устройства.

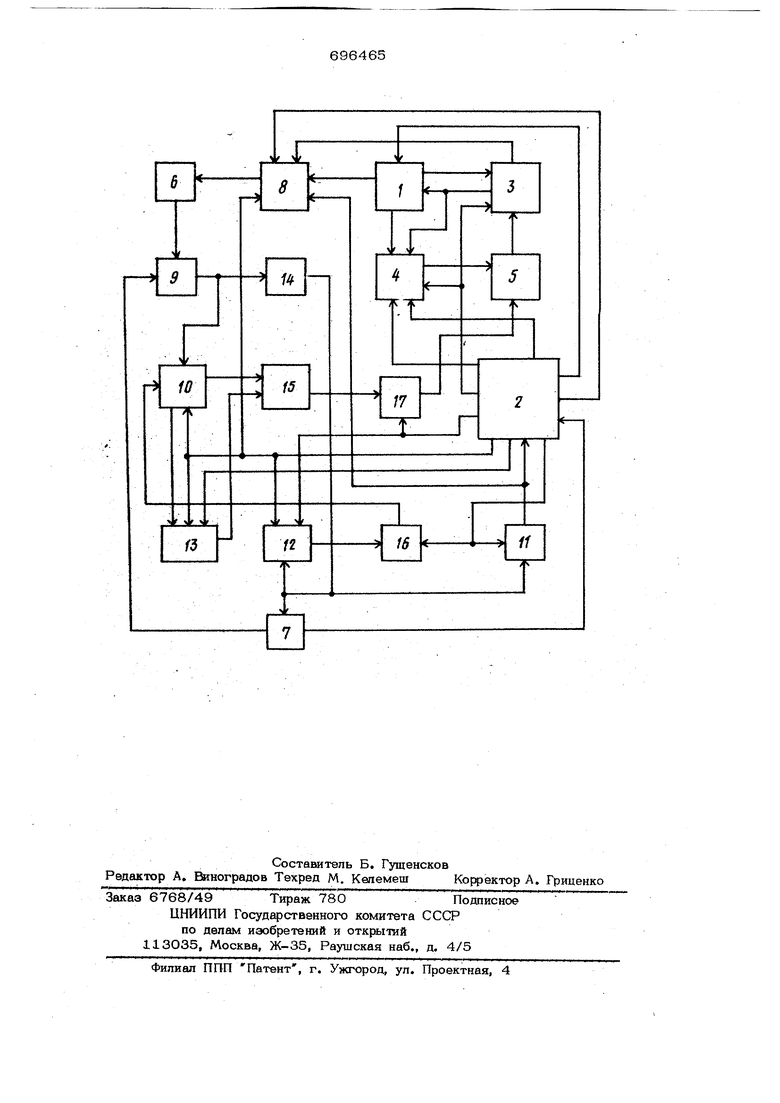

Это достигается тем, что в устройст во введены блок вспомогательных регистров, блок регистров повтора, коммутатор, два регистра, три триггера, элет 1енты ИЛИ и И. Выход узла контроля через коммутатор соединен со входом первого регистра. Второй выход узла прерываний через регистр соединен с первым входом второго регистра и входом первого элемента ИЛИ, выход которого соединен с входом узла прерываний, первыми входами первого-к второго триггеров. Выход первого триггера соединен с четвертым входом узла контроля и вторым входом блока микропрограммного управления, четвертый выход которого соединен со вторым входом первого триггера и чфез первый элемент И - со вторым входом второго регистра, первый выход которого соединен с первым входом третьего триггера, а второй выход через последовательно соединенные второй элемент ИЛИ и второй элемент И сое динен с первым входом блока регистров .повтора, второй вход и выход которого соединены соответственно с выходом блока вспомогательных регистров и третьим входом локальной . Входы блока вспомогательных регистров соединены с третьим входом устройства, первым выходом локальной памяти, третьим, пятым и шестым выходами блока микропрограммного управления, седьмой выход которого соединен со вторьши входами второго и третьего триггеров, третьим входом второго регистра и пятым входом узла контроля. Восьмой выход блока микропрограммного управления через третий триггер соединен с входом второго элемента ИЛИ. Девятый шаход блока микропрограммного удравления соединен с входом второго элемента И и череэ второй триггер - со входом первого элемента И Блок - схема устройства приведена на чфтеже. Устройство для восстановпеиия работы процессора содержит блок 1 офаботки, блок 2 микротфограммного управления, локальную память 3, блок 4 вспомогательных регистров, блок 5 регистров повтора, коммутатор в, узел 7 прерываНИИ, узел 8 контроля, регистры 9 и 10, триггеры 11-13, элементы ИЛИ 14 и 15, элементы И 16 и 17. Устройство работает следующим образом. Каждая микрокоманда задает два операнда в локальной памяти 3 и функцию блока 1. В процессе выполнения микрокоманды выполняется этап чтения исходных операндов из локальной памяти 3 и выполнения операции в блоке 1; и этап записи результата оптации на место одного из исходных операндов в локальной п амати 3. Блок 2 осуществляет дешифра цию микрокоманд и. синхронизацию работы устройства, вырабатывая четыре серии синхросигналов, сдвинутых друг относительно друга: СИ 1- СИ 4 с четверто го, девятого, шестого и восьмого выходов блока 2 соответственно. Выполнение каждого этапа микрокоманды синхронизируется последовательностью СИ 1-СИ 4 причем второй этап каждой микрокоманды по времени выполнения совмещается с первым этапом следующей микрокоманды. Узел 8 контролирует работу устройства. При возникновении сбоякоммутатор 6 выделяет типы ошибок соответственно этапу исполнения микрокоманды, в котоой они возникли. Сигналы типов посупают на врет,1енное хранение в регистр 9. По установленному разряду регистра 9 элемент 14 вырабатывает запрос на микропрограммное прерывание, поступающий в узел 7 и на входы триггеров 11 и 12. В результате прерывания управление передается микропрограмме повтора, после чего регистр 9 сбрасывается сигналом из узла 7. До выхода на прерываiffle устанавливается триггер 11, который запрещает любое иаленение состояния устройства. Устройство содержит два блока регистров 4 и 5. Каждый цикл в блок 5 по СИЗ принимается информация о состоянии устройства, которая необходима для повторения текущей микрокоманды. Это - адрес локальной памяти 3 и адрес микрокоманды из блока 2, первоначальное содержимое и еняемой ячейки локальной памятм 3 и состояние блока 1. В следующая цикле по СИ2 через элемент 17 эта информация переписывается в блок 5. В случае ошибки в данной микрокоманде регистр 9, триггеры 12 и 13, элементы 15 и 16 обеспечивают блокировку изменения информации в блоке 5 в тот момент, когда в нем находится информация, относящаяся к сбойной микрок(Ж1анде. Для этого по СИ1 через элемент 16 информация п еписывается из регистра 9 в регистр Ю. При ошибке типа, соответствующего второму эт&пу, блокировка производится немедленно через элемент 15 и инверсный вход элемента 17. При ошибке типа, соответствующего первому этапу по СИ4 устанавливается триггер 13, и блокировка, таким образом, задерживается на один цикл.. Для предотвращения сфоса блокировки по СИ2 устанавливается тужггер 12, инверсный ылход которого запрещает прохождение СЙ1 через элемент 16, Микропрограмма повтора, пользуясь информацией из блока 5, восстанавливает состояние устройства, непосредственно предшествующее сбойной микрокоманде, сбрасывает узел 8, регистр 10, триггфы 12 и 13 сигналом с седьмого выхода, блока 2, после чего осуществляет возврат к сбойной микроксн 1анде. Таким образом уменьшаются потери времени на повторение, поскольку повторяется самый элементарный шаг в вычислениях - микрокоманда. Кроме того расширяются возможности повторения, так как различные системные действия (прерывания, операции ввода-вывода и т. п.) реалиэуют ся микропрограммным путем. ФЬрмула изобретения Устройство для восстановления работы процессора, содержащее узел контроля, первый и второй входы которого соединены соответственно с первым входом устройства и первым выходом блока микропрограммного управления, второй и тре тий выходы которого соединены соответственно с первым выходом устройства и входом локальной памята, первый и второй выходы которой соединены соответственно со вторым выходом устройства и третьим входом узла контроля, второй вход локальной памята является вторым входом устройства, узел прерываний, первый выход которого соединен с nepffiiiM входом блока микропрограммно го управления, отличающее ся тем, что, с целью повышения быстродействия устройства, в него введены блок вспомогательных регистров, блок регист ров. повтора, коммутатор, два регистра, три триггера, элементы ИЛИ и И, причем выход уапа контроля через коммутатор соединен со входом первого регистра, второй выход узла прерываний чфез первый ретистр соединен с первым входо второго регистра и входом первого элемента ИЛИ, выход которого соединен С входом узла прерываний, первыми входами первого и второго триггеров, выход первого триггера соединен с четвертым входом узла контроля и вторым входом блока микропрограммного управления, четвертый выход которого соединен со вторым входом первого триггера и через первый элемент И - со вторым входом второго регистра, первый выход которого соединен с первым входом третьегх) триггера, а второй выход через последовательно соединенные второй элемент ИЛИ и второй элемент И соединен с первым входом блока регистров повтора, второй вход и выход которого соединены соответственно с выходснл блока вспомогательных регистров и третьим входом локальной памяти, входа блока вспомогательных регистров соединены с третьим входом устройства, первым выходом локальной памяти, третьим, пятым и шестым выходами блока микропрограммного управления, седвАюй выход которого соединен со вторыми входами второго и третьего триггеров, третьим входом второго регистра и пятым входом узла контроля, восьмой выход блока микропрограммного управления через третий триггер соединен с входом второго элемента ИЛИ, девятый выход блока микропрограммного управления соединен с входом второго эл«лента И и через второй триггер - со входом элемента И, Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СХГСР № 535567, шт. Q Об F 9/16, 1974. 2.Патент США № 3533О65, кл. 34Q-172.5 197О (протютип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для восстановления процессора после сбоя | 1979 |

|

SU857999A1 |

| Устройство для выборки микрокоманд | 1976 |

|

SU615478A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

Авторы

Даты

1979-11-05—Публикация

1977-08-17—Подача