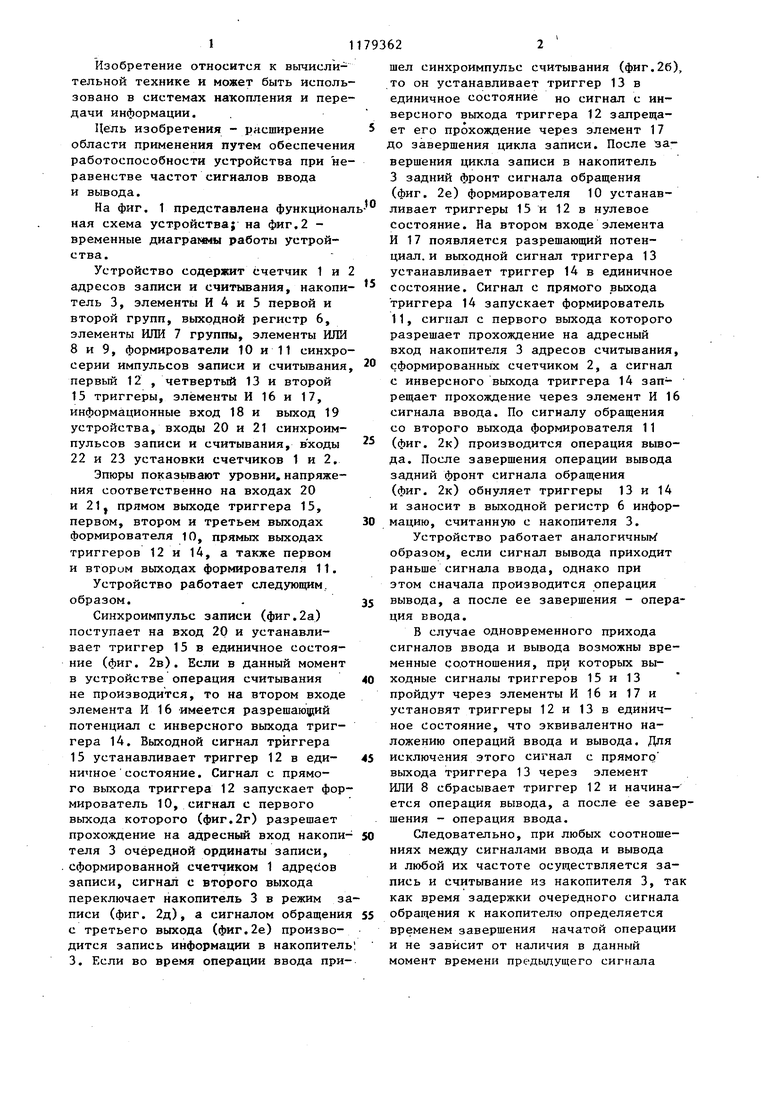

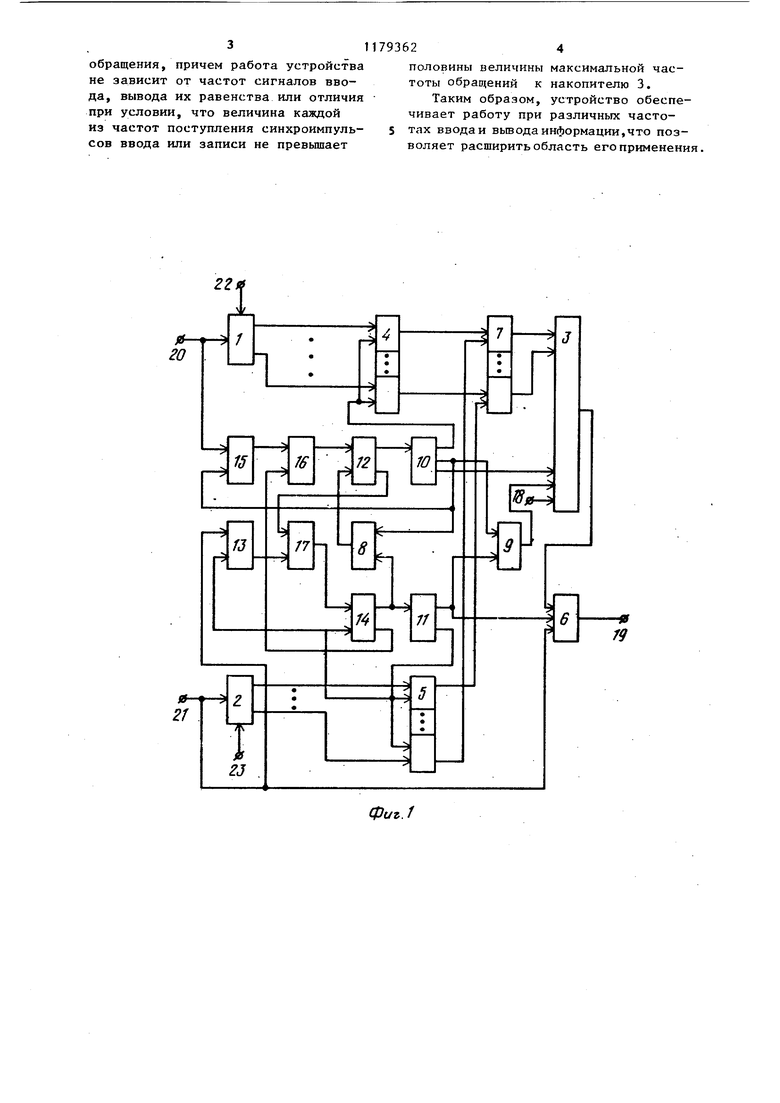

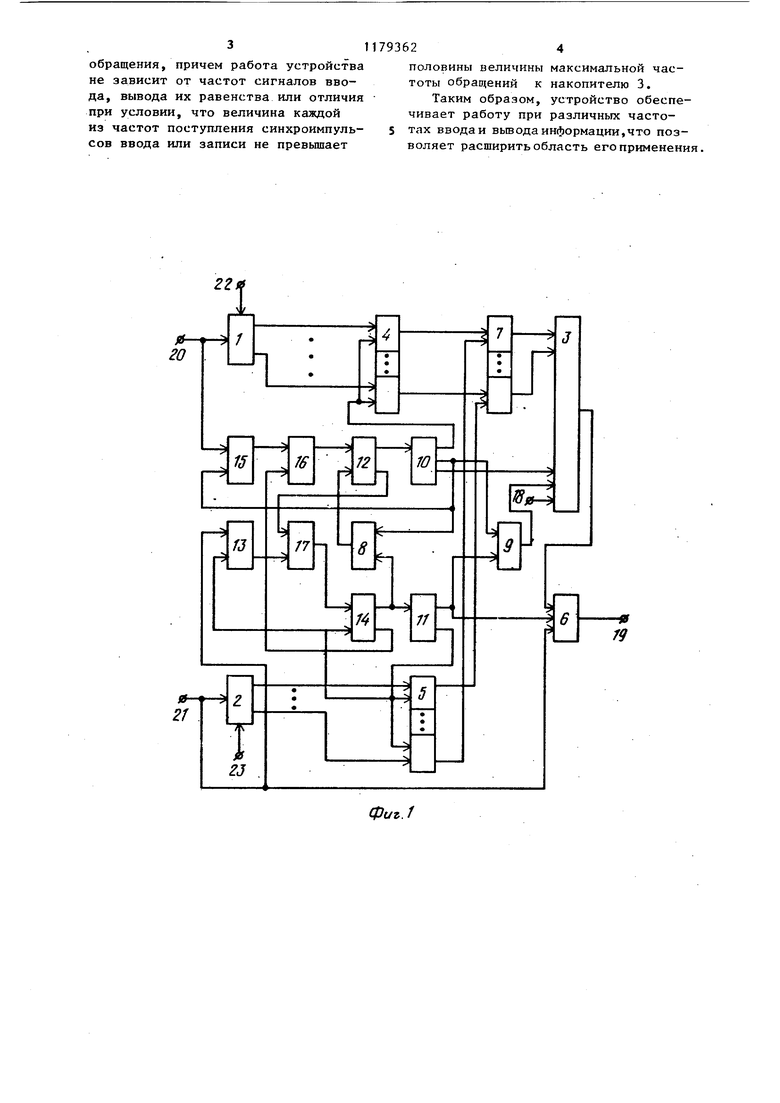

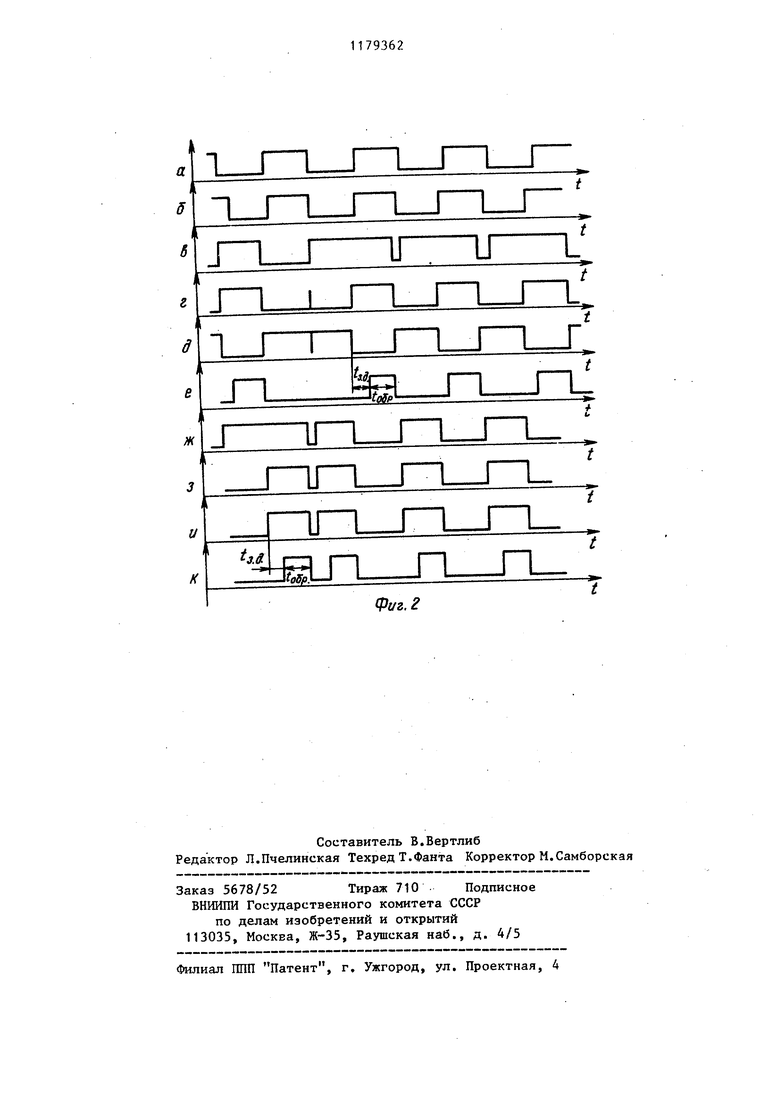

Изобретение относится к вычислительной технике и может быть использовано в системах накопления и передачи информации. Цель изобретения - расширение области применения путем обеспечения работоспособности устройства при неравенстве частот сигналов ввода и вывода. На фиг. 1 представлена функционал ная схема устройства; на фиг.2 временные диагра1(мы работы устройства. Устройство содержит счетчик 1 и адресов записи и считывания, накопи тель 3, элементы И 4 и 5 первой и второй групп, выходной регистр 6, элементы ИЛИ 7 группы, элементы ИЛИ 8 и 9, формирователи 10 и 11 синхр серии импульсов записи и считывани первый 12 , четвертый 13 и второй 15 триггеры, элементы И 16 и 17, информационные вход 18 и выход 19 устройства, входы 20 и 21 синхроим пульсов записи и считывания, входы 22 и 23 установки счетчиков 1 и 2. Эпюры показывают уровни.напряжения соответственно на входах 20 и 21j прямом выходе триггера 15, первом, втором и третьем выходах формирователя 10, прямых выходах триггеров 12 и 14, а также первом и втором выходах формирователя 11. Устройство работает следующим, образом. Синхроимпульс записи (фиг.2а) поступает на вход 20 и устанавливает триггер 15 в единичное состояние (фиг. 2в). Если в данный момент в устройстве операция считывания не производится, то на втором входе элемента И 16 имеется разрешающий потенциал с инверсного выхода триггера 14. Выходной сигнал триггера 15 устанавливает триггер 12 в единичное состояние. Сигнал с прямого выхода триггера 12 запускает фор мирователь 10, сигнал с первого выхода которого (фиг,2г) разрешает прохождение на адресный вход накопи теля 3 очередной ординаты записи, . сформированной счетчиком 1 адресов записи, сигнал с второго выхода переключает накопитель 3 в режим з писи (фиг. 2д), а сигналом обращени с третьего выхода (фиг.2е) производится запись информации в накопител 3. Если во время операции ввода при 1 622 шел синхроимпульс считывания (фиг.2б), то он устанавливает триггер 13 в единичное состояние но сигнал с инверсного выхода триггера 12 запрещает его прохождение через элемент 17 до завершения цикла записи. После завершения цикла записи в накопитель 3 задний фронт сигнала обращения (фиг. 2е) формирователя 10 устанавливает триггеры 15 и 12 в нулевое состояние. На втором входе элемента И 17 появляется разрешающий потенциал, и выходной сигнал триггера 13 устанавливает триггер 14 в единичное состояние. Сигнал с прямого выхода триггера 14 запускает формирователь 11, сигнал с первого выхода которого разрешает прохождение на адресный вход накопителя 3 адресов считывания, сформированных счетчиком 2, а сигнал с инверсного выхода триггера 14 зап- рещает прохождение через элемент И 16 сигнала ввода. По сигналу обращения со второго выхода формирователя 11 (фиг. 2к) производится операция вывода. После завершения операции вьгоода задний фронт сигнала обращения (фиг. 2к) обнуляет триггеры 13 и 14 и заносит в выходной регистр 6 информацию, считанную с накопителя 3. Устройство работает аналогичны образом, если сигнал вывода приходит раньше сигнала ввода, однако при этом сначала производится операция вывода, а после ее завершения - операция ввода. В случае одновременного прихода сигналов ввода и вывода возможны временные соотношения, при которых выходные сигналы триггеров 15 и 13 пройдут через элементы И 16 и 17 и установят триггеры 12 и 13 в единичное состояние, что эквивалентно наложению операций ввода и вывода. Для исключения этого сигнал с прямого выхода триггера 13 через элемент ИЛИ 8 сбрасывает триггер 12 и начина- ется операция вывода, а после ее завершения - операция ввода. Следовательно, при любых соотношениях между сигналами ввода и вывода и любой их частоте осуществляется запись и считывание из накопителя 3, так как время задержки очередного сигнала обращения к накопителю определяется временем завершения начатой операции и не зависит от наличия в данный момент времени предыдущего сигнала

обращения, причем работа устройства не зависит от частот сигналов ввода, вывода их равенства или отличия при условии, что величина каждой из частот поступления синхроимпульсов ввода или записи не превышает

половины величины максимальной частоты обращений к накопителю 3.

Таким образом, устройство обеспечивает работу при различных частотах ввода и вьшода информации,что позволяет расширить область его применения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения блоков памяти | 1981 |

|

SU964649A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для контроля записи информации в блоках памяти | 1982 |

|

SU1076954A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ С ПАМЯТЬЮ, содержащее счетчик адресов записи и счетчик адресов считывания, счетные входы которых явля:ются соответственно входами синхроимпульсов записи и считывания устройства, а группы выходов соответственно подключены к первым входам элементов И первой и второй групп, выходы которых подключены соответственно к первым и вторым входам элементов ИЛИ групп, а вторые входы элементов И первой и второй групп - соответственно к первым выходам формировате ;ля синхросерии импульсов записи и формирователя синхросерии импульсов считывания, вторые выходы которых соединены соответственно с входами разрешения записи накопителя и выходного регистра, синхровход и выход которого соединены соответственно с входом синхроимпульсов считывания устройства и информационным выходом устройства, а информационный вход - с выходом накопителя, адресный вход которого подключен к выходам элементов ИЛИ группы, два элемента И, два элемента ИЛИ и первый триггер, входом сброса соединенный с выходом первого элемента ИЛИ, отличающееся тем, что, с целью расширения области применения устройства, в него введены три триггера, причем третий выход формирователя синхросерии импульсов записи подключен к первым входам первого и второго элементов ИЛИ и входу сброса второго триггера, а вход к прямому выходу первого триггера, установочные входы первого и третье го триггеров подключены соответственно к выходам первого и второго элементов И, первые входы которых соединены соответственно с выходами второго и четвертого триггеров, а вторые входы - соответственно с инверсными выходами третьего и первого триггеров, информационный вход накопителя является информационным входом устройства, вход обращения,накопителя соединен с выходом второго элемента И, вторым входом подключенного к второму выходу формирователя синхросерии импульсов считывания, первый выход которого соединен с входами сброса третьего и четвертого триггеров, а вход - с выходом третьего триггера и вторым входом первого элемента РШИ, установочные входы второго и четвертого триггеров соединены соответственно с входами синхроимпульсов записи и считывания устройства.

Фиъ.1

LJ

П

J

ж

Г1П

i,.t

и

и

J-L

Г-L

Фиг. г

| Устройство для сопряжения блоков памяти | 1977 |

|

SU624231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения блоков памяти | 1981 |

|

SU964649A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-01-25—Подача