(Б) УСТРОЙСТВО для СОПРЯЖЕНИЯ БЛОКОВ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Динамическое запоминающее устройство и формирователь синхросигналов для него | 1980 |

|

SU936030A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения с памятью | 1984 |

|

SU1179362A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Запоминающее устройство | 1989 |

|

SU1718272A1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

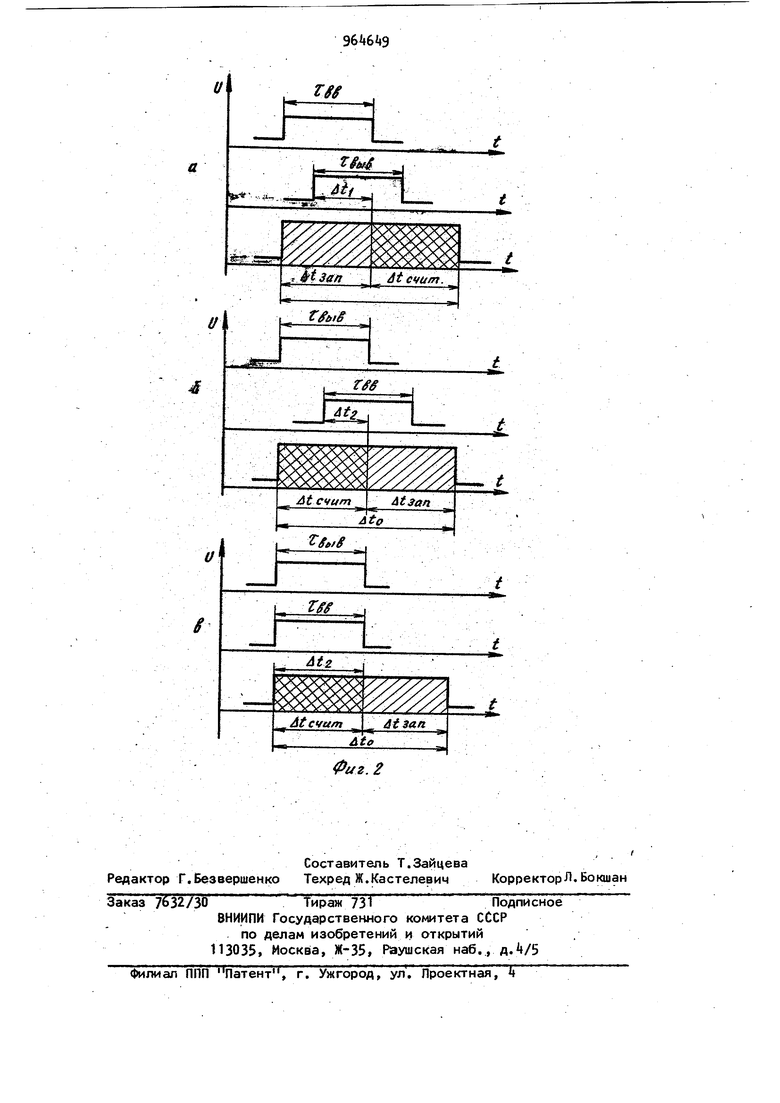

1 Изобретение относится к вычислительной технике и мoжet быть исполь зовано в системах накопления и передачи информации.. Известно устройство для сопряжения блоков памяти, которое содержит накопитель, шины записи и считывания, подключенные к входам формиров телей записи, считывания и строба, а также элемент задержки, включенны между входом накопителя и выходом формирователя строба записи t1. Недостатком этого устройства является низкая надежность. Наиболее близким к изобретению является устройство для сопряжения блоков памяти,содержащее элемент НЕ три элемента И и элемент ИЛИ, соединенный через второй элемент И с первым элементом И, а через третий элемент И с одним из формирователей строба, формирователем считывания и элементом НЕ, выхрд которого подключен к одним из входов первого и второго элементов И, другие входы которых подключены соответственно к выходам формирователей строба и записи, ВЫХОДЫ элемента ИЛИ и первого элемента И соединены с соответствующими входами накопителя 2. Недостатком известного устройства является низкое быстродействие, так как длительность цикла записи-считывания равна утроенному времени обращения к накопителю для осуществления операции записи или считывания, т.е. быстродействие устройства в три раза ниже быстродействия накопителя. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для сопряжения блоков памяти, содержацее формирователь сигнгчлов записи, формирователь сигналов считывания, накопитель, элементы И, первый элемент ИЛИ, выход которого подключен к первому входу накопителя, а входы соединены с выходами первого и второго элементов И, первые входы которых подключены соответственно к выходу формирователя сигналов записи и выходу формирователя сигналов считывания, первый формирователь сигналов стробирования выход которого соединен с вторыми входами первого элемента И и накопителя, и второй формирователь сигналов стробирования, выход которого подключен к второму входу второго элемента И, введены триггеры, элементы НЕ, генераторы одиночных си|- налов, второй и третий элементы ИЛИ и элементы И с третьего по восьмой, причем выходы третьего и четвертого элементов И соединены соответственно с входами второго элемента ИЛИ, выход которого подключен к первому вхо ду первого триггера, второй вход которого соеднгнен с выходом третьего элемента ИЛИ, входы которого подключены соответственно к выходам пятого и шестог элементов И, первый вход третьего элемента И соединен с входом формирователя сигналов записи, первым входом седьмого элемента И, входом первого элемента НЕ и входом первого генератора одиночных сиг налов, выход которого подключен к первому входу пятого элемента И, выход первого элемента НЕ подключен к входу второго генератора одиночных сигналов и первому входу шестого эле мента И, второй вход которого соединен с первым входом восьмого элемента И и входами второго элемента НЕ, формирователя сигналов считывания и третьего генератора одиночных сигналов, выход которого подключен к второму в.ходу пятого элемента И, второй вход третьего элемента И соединен с выходом второго элемента НЕ и входом четвертого генератора одиночных сигналов, выходы второго и четвертого генераторов одиночных сигналов подкл чены соответственно к входам четвертого элемента tl, выходы первого триг гера соединены соответственно с вторыми входами седьмого и восьмого эле ментов И, выходы которых подключены соответственно к входам первого и второго формирователей сигналов стро бирования, выход второго формирователя сигналов стробирования соединен с первым входом второго триггера, второй вход которого соединен с выхо дам накопителя, а выход - с первым входом третьего триггера, второй вхо которого подключен к входу формирователя сигналов считывания, а выход является выходом устройства. На фиг. 1 представлена структурная схема предлагаемого устройства) на фиг. 2 - временные диаграммы, поясняющие его работу. Устройство содержит формирователь 1 сигналов записи, первый формироватёль 2 сигналов стробирования, первый элемент И 3 пер.вый элемент ИЛИ Ц, накопитель 5 первый триггер 6, формирователь 7 сигналов считывания, второй формирователь 8 сигналов ctpoбирования, второй 9, третий 10 и четвертый 11 элементы И, второй элемент ИЛИ 12,. пятый 13 и шестой 1 элементы И, третий элемент ИЛИ 15, второй тригг;ер 16, седьмой .17 и восьмой 18 элементы И, первый 19 и второй 20 генераторы одиночных сигналов, первый элемент НЕ 21, третий 22 и четвертый 23 генераторы одиночных сигналов, второй элемент НЕ 24 и третий триггер 25. На фиг. 1 обозначены вход 2б записи и вход 27 считывания устройства и выход 28 устройства. На фиг. 2 обозначены длительность Гаасигнала ввода на входе записи устройства, длительность Твь1бсигнала вывода на входе считывания устройства, длительность tp цикла записи - считывания, время ut задержки сигнала вывода -при прохождении его через первый элемент НЕ, длительность t3anOn6P9UMM записи, длительность t ц пepaции считывания, время dt задержки цикла записи относительно начала сигнала ввода. Устройство работает следующим образом. Сигнал ввода Tgg(фиг. 2) поступает на первый вход элемента И 10 и вход формирователя 1. При отсутствии е данный момент времени сигнала вы вода fgfj, на входе 27 на втором входе элемента И 10 присутствует разрешающий потенциал. При этом сигнал ввода проходит через элемент ИЛИ 12 и устанавливает триггер 6 в единичное состояние. Сигнал с прямого выходатриггера 6 разрешает прохождение, сигнала ввода через элемент И 17 на вход, формирователя 2. .Сигнал ввода запускает формирователь 2, выходной сигнал которого разрешает прохождение на вход накопителя 5 очередного сигнала записи, сформиро-.

ванного формирователем 1, и переключает накопитель 5 в режим записи.

Если сигнал вывода приходит после сигнала ввода, а цикл записи в накопителе 5 не закончился (фиг. 2а), сигнал вывода не пройдёт через элемент И. 14, так как сигнал ввода через элемент НЕ 21 запретит его прохождение на время &t завершения цикла записи. После завершения цикла записи сигнал вывода проходит через элемент И I, элемент ИЛИ 1 и переключает триггер 6 в нулевое состояние. Сигнал с инверсного выхода три ггера 6 разрешает прохождение сигнала вывода, через элемент И 18 на вход формирователя 8..Сигнал вывода ; запускает формирователь 8, выходной сигнал которого разрешает прохождение на вход накопителя 5 сигнала считывания,. сформированного формирователем 7.

В случае, если сигнал вывода приходит раньше сигнала ввода (фиг. 2,6) цикл считывания начинается с приходом сигнала вывода, а цикл записи задерживается на время (фиг.2,6/ до окончания сигнала вывода, так как сигналлвывода через элемент НЕ 2k запрещаетпрохождение сигнала ввода через элемент И 10. Если же сигналы ввода и вывода приходят одно1вреНенно (фиг. 2,в) ни один из них не пройдет через элементы И 10 и 14, так как на их вторых входах будет запрещающий потенциал. Но.при этом выходные сигналы генераторов 19 и 22, которые запускаются передними фронтами сигналов ввода и вывода, соответственно, совпадают во времени и проходят через элемент И 13, сигнал с выхода которого через элемент ИЛИ 15 устанавливает триггер 16 в нулевре состояние, и начинается цикл считывания. Цикл записи начнется после срабатывания генераторов 20 и 23, которые запускаются задними фронтами сигналов ввода и вывода, соответственно, по окончании цикла считывания.. Длительность iTQ.iy сигналов на выходах генераторов 19, 20, 22 и 23 выбирается из условия

ОАН тр 1

где время задержкираспространения при включении или выключении триггера 6.

При этом, если сигнал ввода поступает раньше сигнала вывода на время

, триггер 6 сначала устанавливается в единичное состояние сигналом ввода, а затем в нулевое сигналом совпадения выходных сигналов генераторов 19 и 22. В этом случае устройство работает аналогично случаю одновременного прихода сигнала ввода и вывода, а время цикла записи-считывания удлинится на время 2 . Но так как , этим увеличением можно пренебречь.

Следовательно, при любых соотношениях во времени между сигналами ввода и вывода осуществится запись и считывание из накопителя 5, но выходной сигнал накопителя 5 может задержаться относительно сигнала вывода на величину xit-i (фиг. 2, а). Чтобы устранить этот недостаток, сигнал с накопителя 5 заносится стробом .считывания в триггер 16 и переписывается в триггер 25 по, сигналу вывода.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно обеспечивает более высокое быстродействие по сравнению с известным.

Формула изобретения

Устройство для сопряжения блоков памяти, содержа1чее формирователь сигналов записи, формирователь сигналов считывания, накопитель, элементы И, первый элемент ИЛИ, выход которого подключен к первому входу накопителя , а входы - к выходам первого и второго элементов И, первые входы которых подключены соответственно к выходу формирователя сигналов записи и выходу формирователя сигналов считывания, первый формирователь сигнало стробирования, выход которого соединен с вторыми входами первого элемента И и накопителя, и второй формирователь сигналов стробирования, выход которого подключен к второму входу второго элемента И, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит триггеры, элементы НЕ, генераторы одиночных сигналов, второй и третий,элементы ИЛИ и элементы И с третьего и четвертого элементов И соединены соответственно с входаш второго элемента ИЛИ, выход кот торого подключен к первому входу перIвого триггера, второй вход последнего соединен с выходом третьего элемента И Ш, входы которого подключены соответств®1но к выходам пятого и шестого элементов И, первый вход тре тьего элемента И соединен с входом формирователя сигналов записи, первым входом седьмого элемента И, входом первого.элемента НЕ и входом пер вого генератора одиночных сигналов, выход которого подключен к первому входу пятого элемента И, выход перво го элемента НЕ подключен к входу вто рого генератора одиночных сигналов и первому входу шестого элемента И, втр|эой вход которого соединен с первым входом восьмого элемента Ни с входами второго элемента НЕ, формирователя сигналов считывания и третьего генератора одиноч.ных сигналов, выход которого подключен к второму входу пятого элемента И, второй вход третьего элемента И соединен с выхо.дом второго элемента НЕ и входом чет вертого генератора одиночных сигналов, выходы второго и четвертого генераторов одиночных сигналов подключены соответственно к входам четвертого элемента И, выходы первого триггера соединены,.Соответственно с вторыми входами седьмого и восьмого элементов И, выходы которых подключены соответственно к входам первого и второго формирователей сигналов стробирования-, выход формирователя сигналов стробирования соединен с первым входом второго триггера, второй вход которого соединен с выходом накопителя, а выход - с первым входом третьего триггера, второй вход которого подключен к входу формирователя сигналов считывания, а выход является выходом устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 01999, кл. G 06 F 13/02, 1973. 2.Авторское свидетельство СССР , кл. G 06 F 13/02, 1978 (прототип).

Авторы

Даты

1982-10-07—Публикация

1981-03-18—Подача