тановки нуля триггера, с третьими входом второго элемента И, с вторым единичным входом триггера блока управления, третий н четвертый выходы распределителя импуЯьсов блока управления соединены соответственно с первым входом третьего элемента И и третьим утфавлякщим входом коммутатора блока управления, выход генератора тактовых сигналов блока управления соединен с информационным входом коммутатора блока управ1151973

ления, выход элемента И-НЕ блока управления соединен с вторым входом третьего элемента И блока управления выходы первого, второго и третьего элементов И блока управления соединены соответственно с тактовым входом блока регистрации, с входом записи и счетным входом счетчика , четвертый управляющий вход коммутатора блока управления со5 единен с входом сброса устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для контроля и диагностики радиоэлектронной аппаратуры | 1986 |

|

SU1432463A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ЭЛЕКТРОМЕХАНИЧЕСКИХ БЛОКОВ, содержащее счетчик, блок регистрации, блок сравнения и блок управления, содержащий генератор одиночных сигналов, генератор тактовых сигналов,, элемент НЕ и триггер, причем вход сброса и пуска устройства соединены соответственно с нулевым входом триггера и входом генератора одиночньо; сигналов блока управления, выход генератора одиночных сигналов со1вдинев с входами начальной установки счетчика и блока регистрации, информационнь1й вход устройства соединен с первым информационным входом блока регистрации и с первым информащюнHbiM входом блока сравнения, выход которого соединен с входом элемента НЕ блока управления, о т л и ч а ющ е е с я тем,: что, с целью повышения достоверности контроля, в устройство введены таймер, регистр начального адреса, группа элементов И и блок памяти, а в блок управленияпервый и второй элементы задержки, коммутатор, распределитель импульсов, три элемента И и элемент И-НЕ, причем выход генератора одиночных сигналов блока управления через пер|вый элемент задержки соединен с первым единичным входом триггера блока управления, единичный выход триггера блока управления соединен с входом обращения блока памяти и через второй элемент задержки блока управления - с входом запуска таймера и первыми входами элементов И грзплпы, выходы которых являются выходом устройства, выход элемента НЕ блока управления соединен с первыми входами первого и второго элементов И и элемента И-НЕ блока управления, первый, второй и третий информационные выходы блока памяти, выход адреса перехода, выход призйака услов. ного ;гестирова,ния и выкод признака п конца теста блока памяти соединены соответственно с информационным входом таймера, с вторым информационным входом блока сравнения, с вторыми входами элементов И группы, с пер,вым информационным входом счетчика, с вторыми входами второго элемента И iH элемента И-НБ блока управления, СП с первьм зтаравлякнцйм входом коммутатора блока управления вьрсод реС0 гистра начального адреса соединен oi с вторым информационным входом счетчика, выход которого соединен с яд- ресным входом блока памяти и йторым информационным входом блока регистрации, выход таймера соединен с вторым управляюпцш входом коммутатора блока управления, шосод коммун татора блока управления соединен с тактовым входом распределителя импульсов, первый, второй, ретий и четвертый вглкоды которого соединены (соответственно с вторым входом первого элемента И, с вторым входом ус

Изобретение относится к автоматизированному контролю и может быть использовано при тестовом контроле различных электромеханических объектов .

Цель изобретения - повышение достоверности контроля.

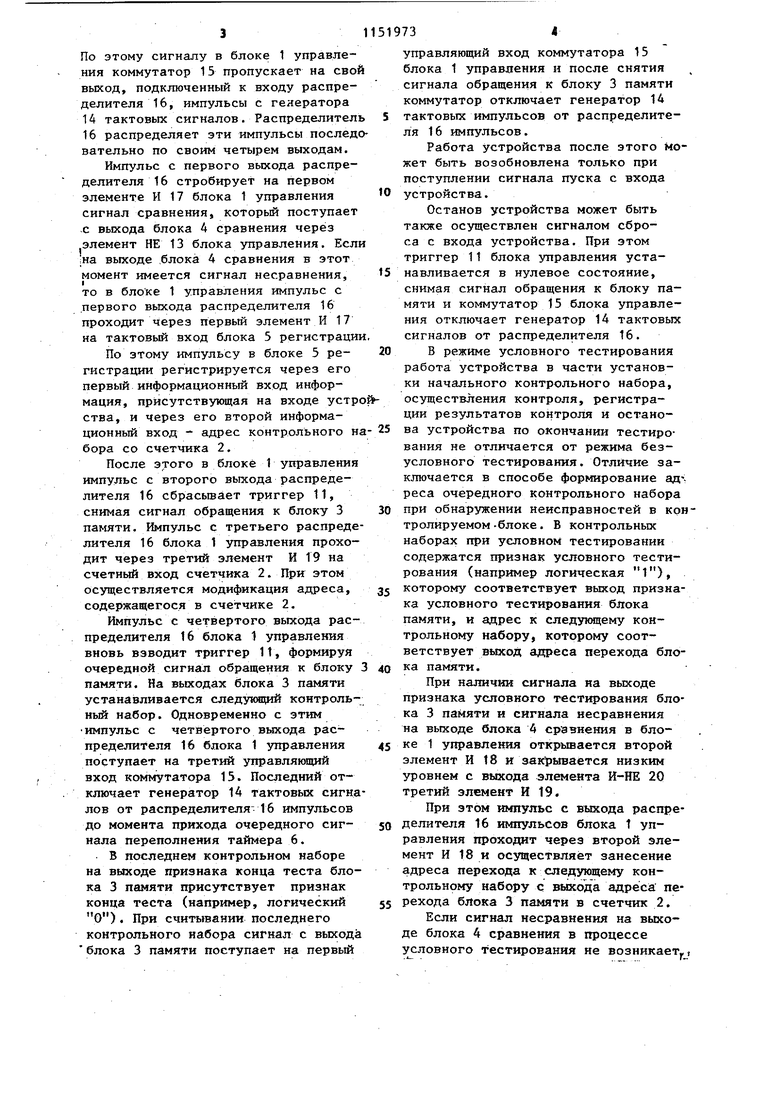

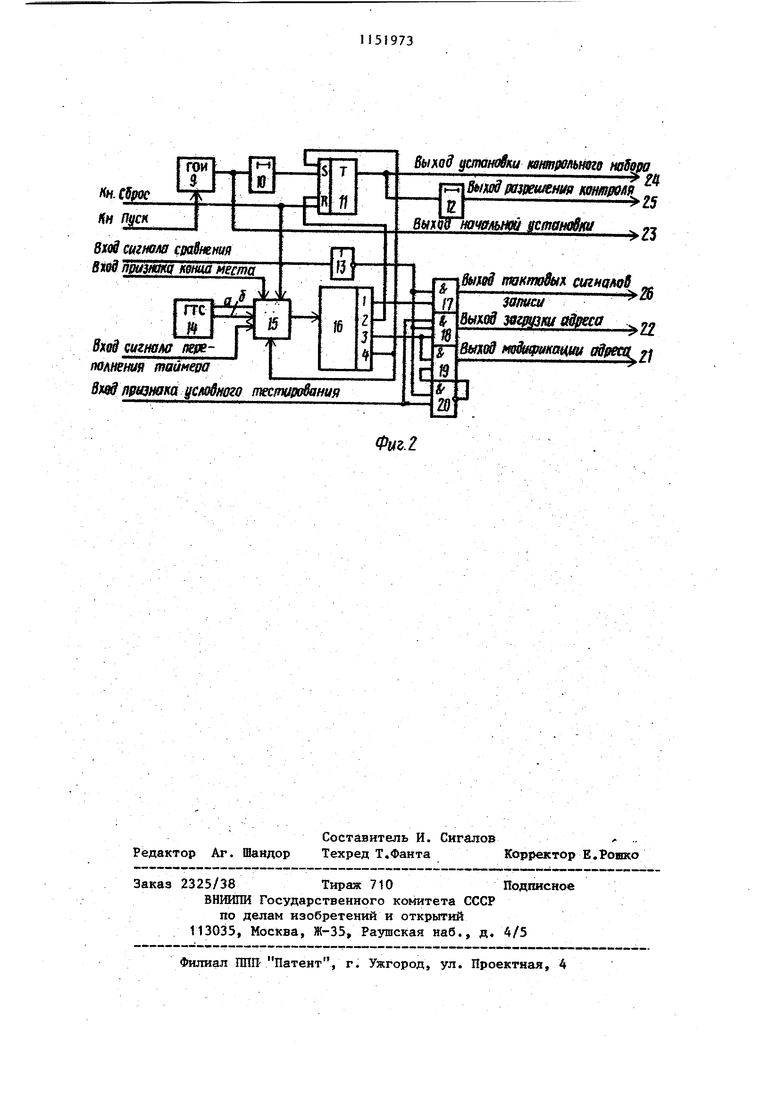

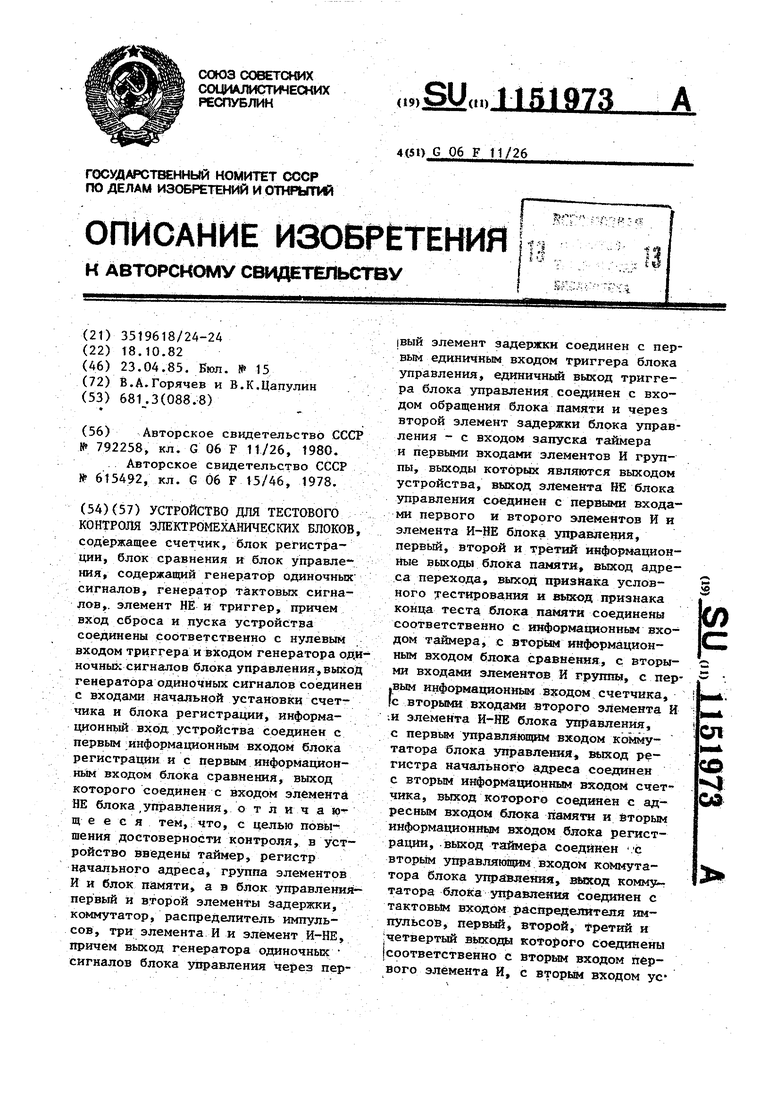

На фиг, 1 показана структурная схема предлагаемого устройства; на фиг. 2 - структурная схема блока управления.

Устройство содержит .блок 1 управления, счетчик 2, блок 3 памяти, блок 4 сравнения, блок 5 регистрации таймер 6, группу элементов И 7, регистр 8 начального адреса. Блок управления содержит генератор 9 одиночных сигналов, первый элемент 10 задержки, триггер t1, второй элемент 12 задержки, элемент НЕ 13, генератор 14 тактовых сигналов, коммутатор 15, распределитель 16 шшульcoBj элементы И 17-19, элемент И-НЕ 20, выход 21 модификации адреса, выход 22 загрузки адреса, выход

23начальной установки, выход

24установки контрольного набора, выход 25 разрешения контроля, выход 26 тактовых сигналов записи.

Устройство работает в двух режимах: условного и безусловного тестирования.

В режиме безусловного тестирования в блоке 1 управления при поступлении сигнала пуска с входа генератор 9 одиаочньБС сигналов формирует импульс, который проходит как сигнал начальной установки на входы начальной установки счетчика 2 и

блока 5 регистрации. По сигналу начальной уст-ановки в счетчик 2 заносится адрес первого контрольного набора с регистра 8 начального адреса.

После этого в блоке 1 управления через время, определяемое элементом 10 задержки, взводится триггер 11, единичный сигнал с выхода

которого разрешает обращение к блоку 3 памяти. На въкодах последнего устанавливается первый контрольный набор.

При этом в таймер 6 с первого информационного выхода блока 3 памяти загружается код временного интервала, определяющий промежуток времени, в течение которого контролируемьй электромеханический блок должен вьтолнить опера1Д1И, задаваемые входньм контрольным набором.

Через время, необходимое для загрузки таймера, на выходе элемента 12 задержки блока 1 управления появляется сигнал, которьй осуществляет запуск таймера 6 и разрешает прохождение входного контрольного набора с третьего информационного выхода блока 3 памяти через элементы И 7 группы на выход устройства.

Ответная реакция контролируемого электромеханического блока, поступившая на вход устройства, сравнивается в блоке 4 сравнения е эталонным набором с второго информационJHoro еыхода блока 3 памяти. При обнулении таймера б возникающий на его выходе сигнал переполнения поступает на второй управлякяф{й вход коммутатора 15 блока 1 управления. По этому сигналу в блоке 1 управления коммутатор 15 пропускает на сво выход, подключенный к входу распределителя 16, импульсы с генератора 14 тактовых сигналов. Распределител 16 распределяет эти импульсы послед вательно по своим четырем выходам. Импульс с первого выхода распределителя 16 стробирует на первом элементе И 17 блока 1 управления сигнал сравнения, который поступает -С выхода блока 4 сравнения через элемент НЕ 13 блока управления. Есл ;на выходе .блока 4 сравнения в этот момент имеется сигнал несравнения, то в блоке 1 управления импульс с первого выхода распределителя 16 проходит через первый элемент И 17 на тактовый вход блока 5 регистраци По этому импульсу в блоке 5 регистрации регистрируется через его первый информационный вход информация, присутствующая на входе устр ства, и через его второй информационный вход - адрес контрольного н

бора со счетчика 2.

После этого в блоке 1 управления импульс с второго выхода распределителя 16 сбрасьшает триггер 11, снимая сигнал обращения к блоку 3 памяти. Импульс с третьего распределителя 16 блока 1 управления проходит через третий элемент И 19 на счетный вход счетчика 2. При этом осуществляется модификация адреса, содержащегося в счетчике 2.

Импульс с четвертого выхода распределителя 16 блока 1 управления вновь взводит триггер 11, формируя очередной сигнал обращения к блоку памяти. На выходах блока 3 памяти устанавливается следующий контрольный набор. Одновременно с этим

импульс с четвертого выхода распределителя 16 блока 1 угфавления поступает на третий управляющий вход коммутатора 15. Последний отключает генератор 14 тактовых сигналов от распределителя 16 импульсов до момента прихода очередного сигнала переполнения таймера 6.

В последнем контрольном наборе на выходе признака конца теста блока 3 памяти присутствует признак конца теста (например, логический О). При считывании последнего контрольного набора сигнал с выхода

блока 3 памяти поступает на первый

вания не отличается от режима безусловного тестирования. ОтлИчие заключается в способе формирование адреса очередного контрольного набора при обнаружении неисправностей в контролируемом -блоке. В контрольных наборах при условном тестировании содержатся признак условного тестирования (например логическая 1), которому соответствует выход признака условного тестирования блока памяти, и адрес к следукяцему контрольному набору, которому соответствует выход адреса перехода блока памяти.

При наличии сигнала на выходе признака условного тестирования блока 3 памяти и сигнала иесравнения на выходе блока 4 сравнения в блоке 1 управления открывается второй элемент И 18 и зак рывается низким уровнем с выхода элемента И-НЕ 20 третий элемент И 19.

При этом импульс с выхода распределителя 16 импульсов блока 1 управления проходит через второй элемент И 18 и осуществляет занесение адреса перехода к следующему контрольному набору с выхода адреса перехода блока 3 памяти в счетчик 2.

Если сигнал несравнения на выходе блока 4 сравнения в процессе

условного тестирования не возникает.

rJ 734 управляющий вход коммутатора 15 блока 1 управления и после снятия сигнала обращения к блоку 3 памяти ко1 1мутатор отключает генератор 14 тактовых импульсов от распределителя 16 импульсов. Работа устройства после этого Может быть возобновлена только при поступлении сигнала пуска с входа устройства. Останов устройства может быть также осуществлен сигналом сброса с входа устройства. При этом триггер 11 блока управления устанавливается в нулевое состояние, снимая сигнал обращения к блоку памяти и коммутатор 15 блока управления отключает генератор 14 тактовых сигналов от распределителя 16. В режиме условного тестирования работа устройства в части установки начального контрольного набора, осуществления контроля, регистрации результатов контроля и останова устройства по окончании тестиро51

то второй элемент И 18 блока 1 управления закрыт, а третий элемент И 19 блока I управления открыт и импульсы с выхода распределителя 16 проходят через третий элемент И 19 на счетный вход счетчика 2.

Таким образом при условном -тести: ровании в программе проверки сиганизуется ветвлейие при каждой отрицательной реакции контролируемого электромеханического блока В блоК 5 регистрации входят элементы инди;кации и И групп многоразрядпик регистров (где П- число контрольных наборов) с последоватбльН Л4 режимом

Т973

заполнения и индикации состояний каждой из групп регистров.

Технико-экономическое преимущество предлагаемого устройства заключается в повышении достоверности контроля за счет организации режима условного тестирования и контроля временньк параметров электромеханических объектов.

to к примеру при контроле накопителей на магнитных дисках устройство позволяет осуществлять поиск неисправностей до уровня типового элемен та замены (ТЭЗ), а также контролиfS ровать временные параметры системы позиционирования, в том числе время перемещения магнитной головки.

Фиъ.г

| Устройство для тестового диагностирования | 1978 |

|

SU792258A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения и диагностики неисправностей логических блоков | 1976 |

|

SU615492A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1982-10-18—Подача