ления, первые входы девятого и десятого элементов И являются четвертым и пятым входами блока управления соответственно, выходы первого и второго элементов ИЛИ являются первым и вторым выходами блока управления соответственно, первый выход генератора импульсов соединен с синхровходами первого и второго триггеров и является третьим выходом блока управления,выходы первого, второго, седьмого, восьмого элементов И и элемента НЕ являются четвертым, пятым, шестым, седьмым, восьмым выходами блока управления соответственно, при этом в блоке управления выход первого элемента И-ИЛИ соединен с вторым входом девятого элемента И, вькод которого соединен с информационным входом первого триггера, единичный выход которого соединен с первыми входами одиннадцатого и двенадцатого элементов И, выход которого соединен с вторыми входами третьего и четвертого элементов И, вьгчод которого соединен с первым входом первого элемента ИЛИ второй вход которого соединен с выходом пятого элемента И, второй вход которого соединен с выходом тринадцатого элемента И и вторым входом шестого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, нулевой выход первого триггера соединен с третьим входом девятого элемента И, выход второго элемента ИИЛИ соединен с вторым входом десятого элемента И, выход которого соединен с информационным входом второго триггера, единичный выход которого соединен с первыми входами тринадцатого и четырнадцатого элементов И, выход которого соединен с вторыми входами седьмого и восьмого элементов И, нулевой выход второго триггера соединен с третьим входом десятого элемента И, второй выход генератора импульсов соединен с вторыми входами четырнадцатого и одиннадцатого элементов И, выход которого соединен с вторыми входами первого и второго элементов И, третий выход генератора импульсов соединен с вторыми входами двенадцатого и тринадцатого элементов И.

2.Устройство по п. 1, о т л ичающееся тем, что блок определения переполнения содержит два элемента И-ИЛИ и триггер, причем первый и второй входы первого и второго элементов И-ИЛИ являк1тся управляющим входом блока определения переполнения, третьи и четвертые входы первого и второго элементов И-ИЛИ являются первым и вторьм информационными входами блока определения переполнения, выход триггера является выходом блок определения переполнения, при этом в блоке определения переполнения единичньй и нулевой входы триггера соединены

с выходами первого и второго элементов И-ЙПИ соответственно.

3.Устройство по п. 1, отличающееся тем, что блок определения режима работы содержит триггер и два элемента И-ИЛИ, причем информационный и синхронизирующий входы триггера являются информационным и синхронизирующим входами блока определения режима работы соответственно, первые входы первого и второго элементов И-ИЛИ являются входом переполнения блока определения режима работы, выходы первого и второго элементов И-ИЛИ являются выходами разрешения записи и считывания блока определения режима работы соответственно, при этом в блоке определения режима работы единичный выход триггера соединен с вторыми входами первого и второго элементов И-ИЛИ, третьи входы которых соединены с нулевым выходом триггера.

Изобретение относится к вычислительной технике, в частности к устройствам для обмена данными и может быть использовано в качестве буфера данных в каналах ввода-вывода ЭВМ,

Целью изобретения является повышение быстродействия устройства.

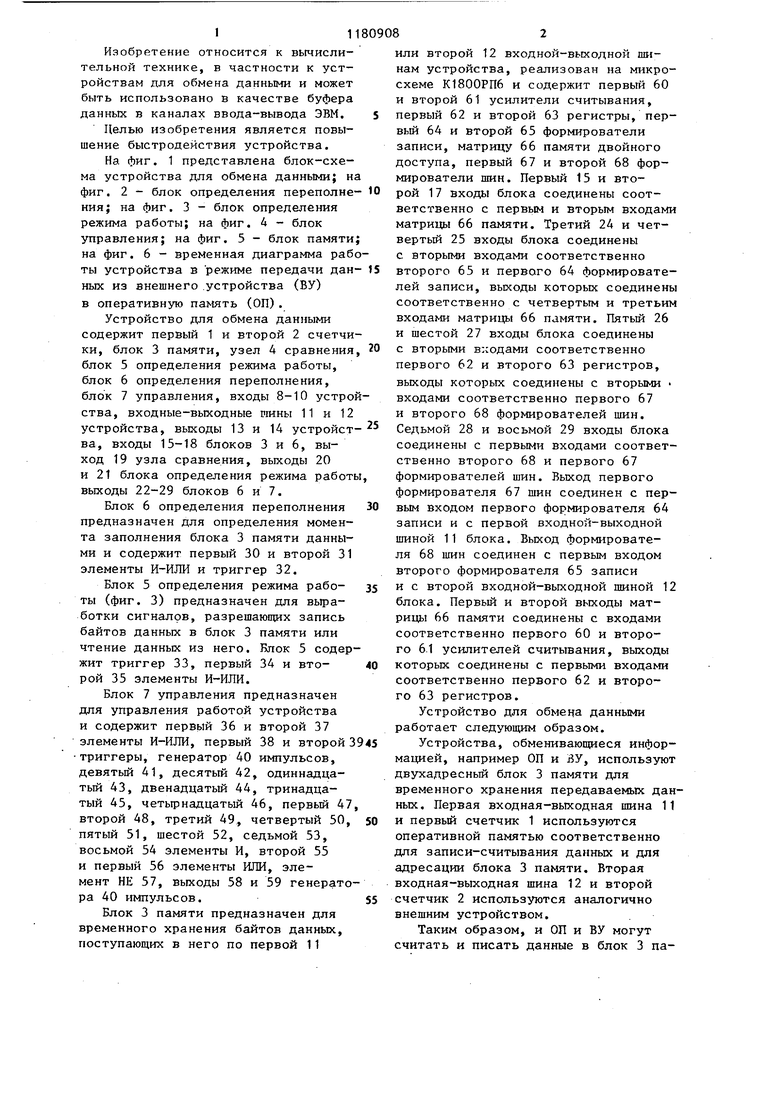

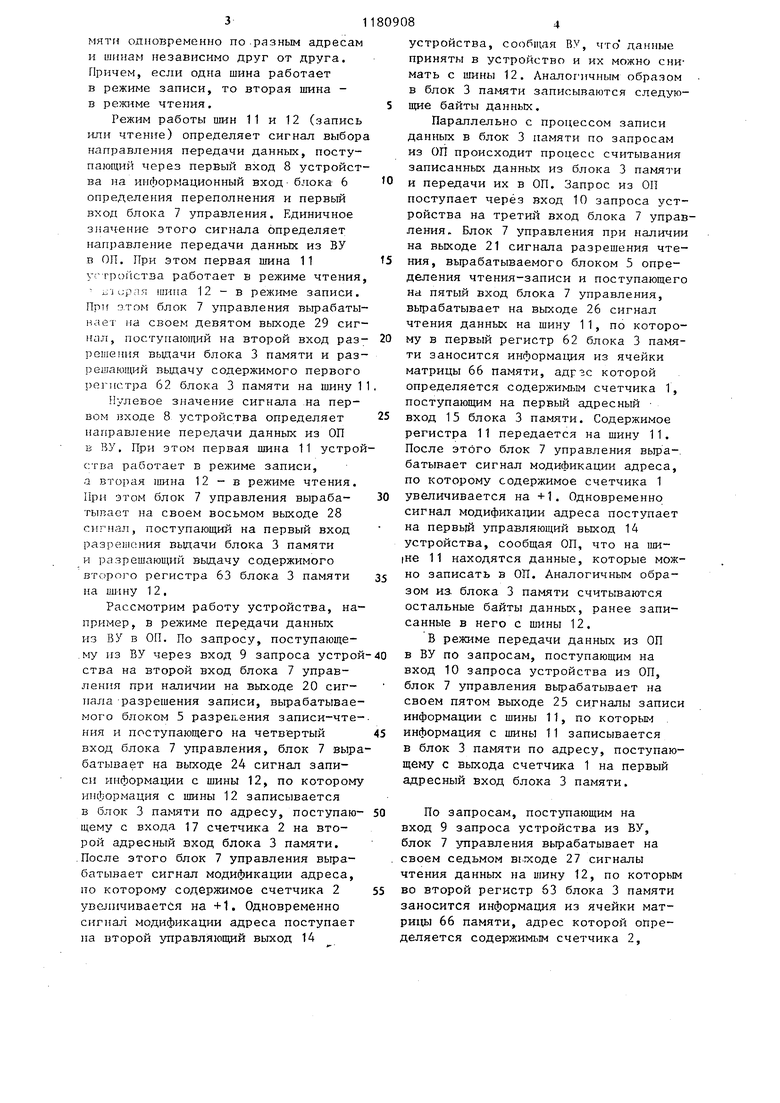

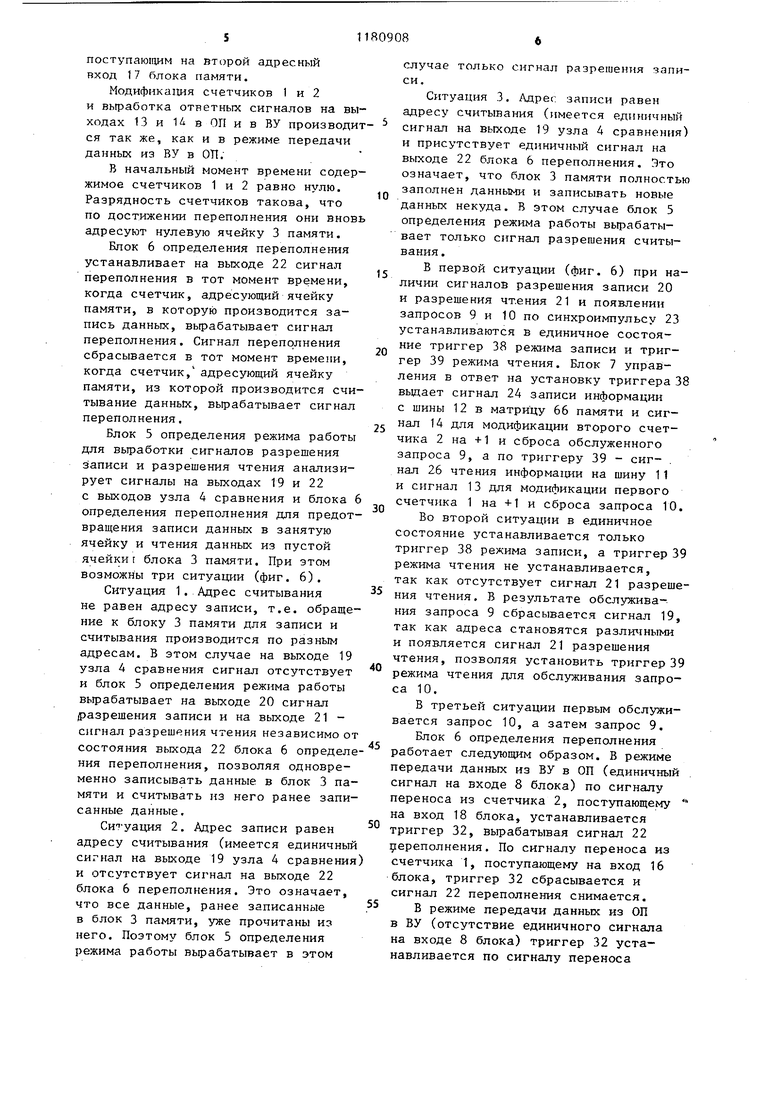

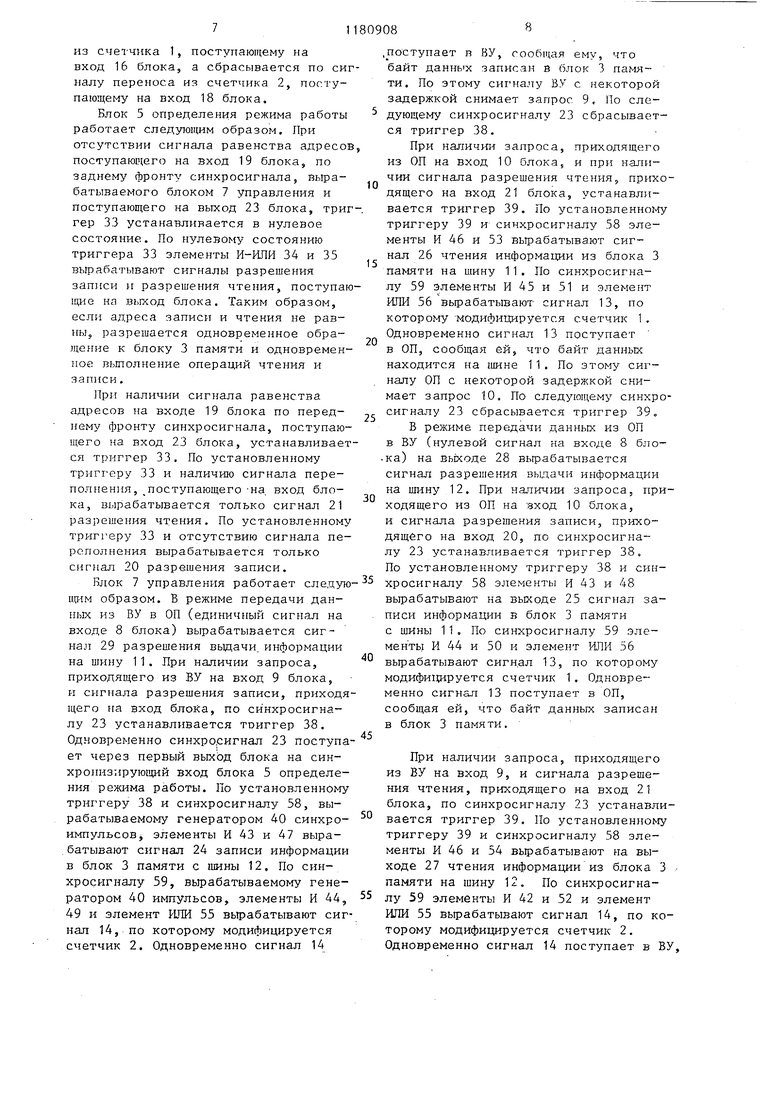

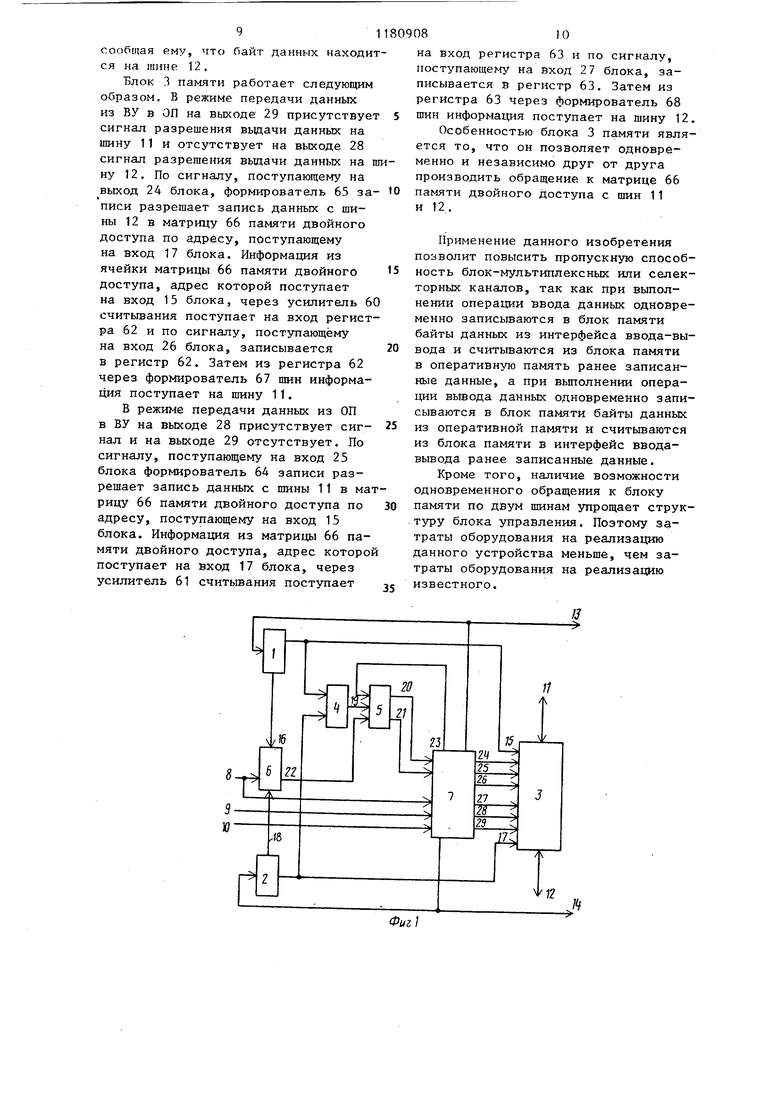

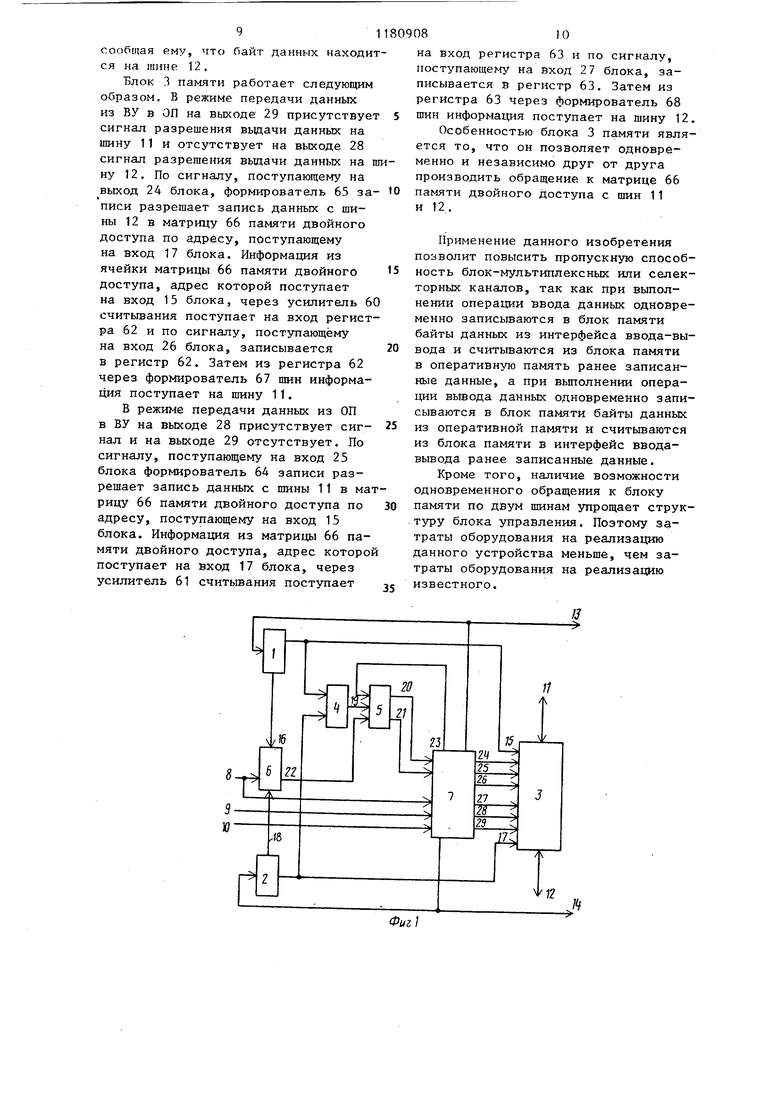

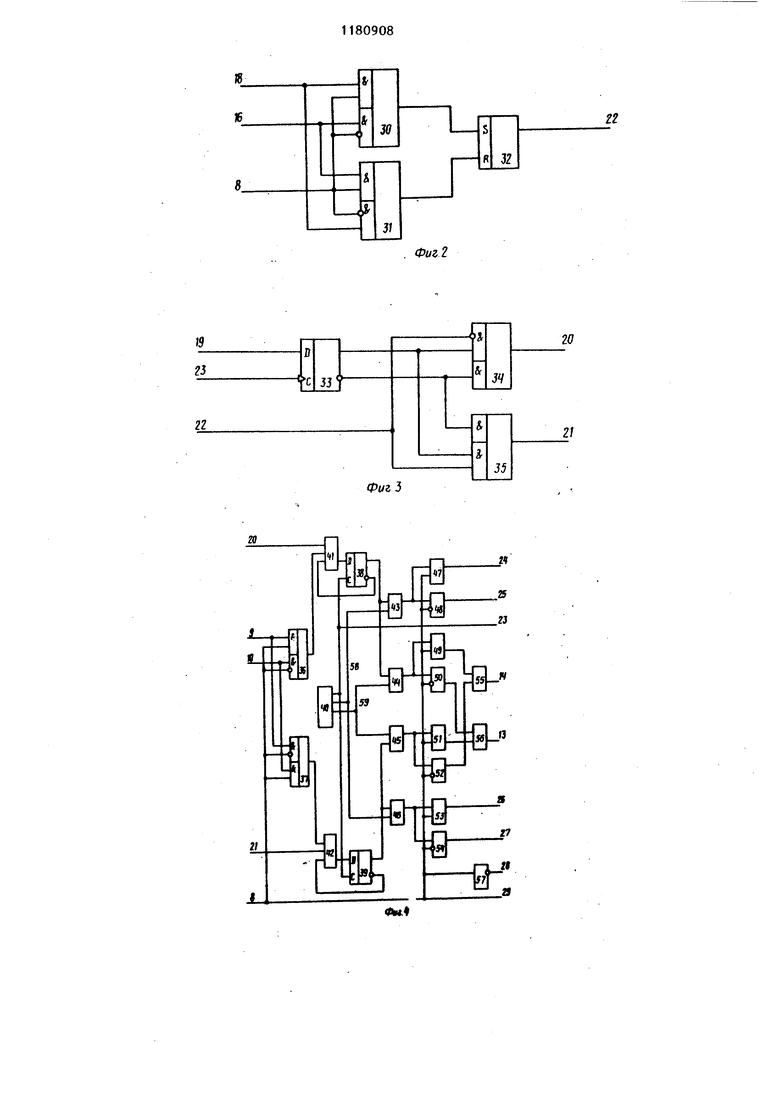

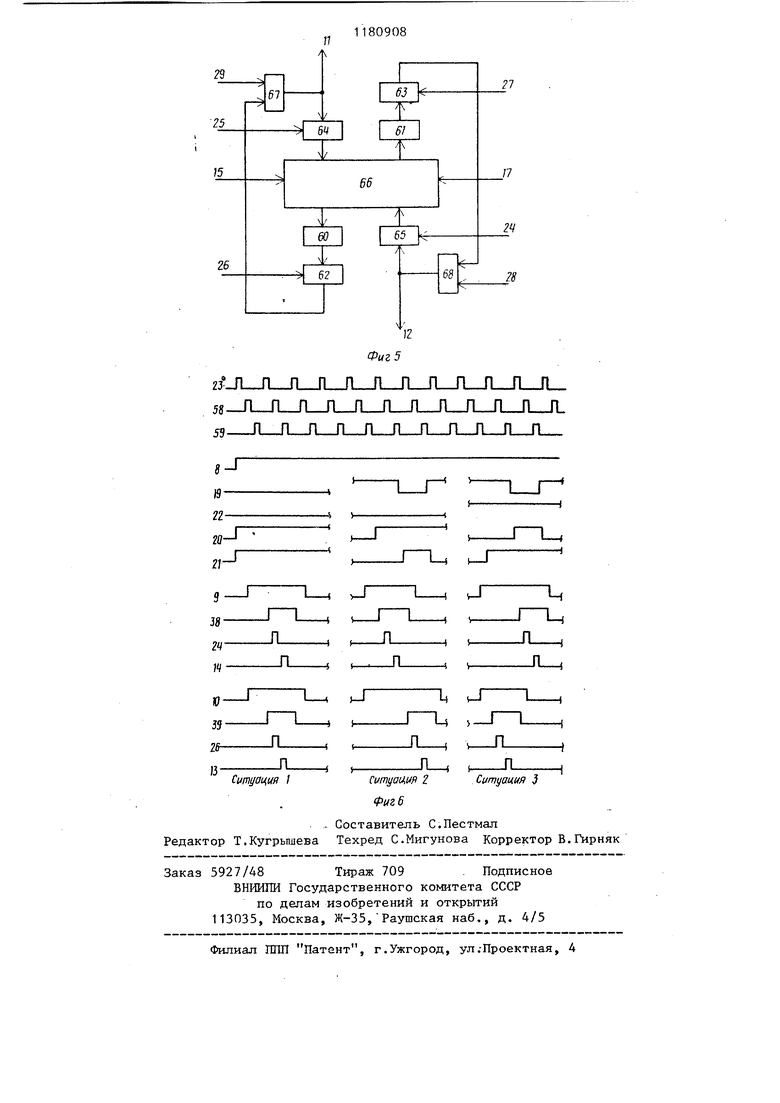

На фиг. 1 представлена блок-схема устройства для обмена данными; на фиг. 2 - блок определения переполне- кия; на фиг. 3 - блок определения режима работы; на фиг. 4 - блок управления; на фиг. 5 - блок памяти; на фиг. 6 - временная диаграмма работы устройства в режиме передачи данных из внешнего .устройства (ВУ) в оперативную память (ОП).

Устройство для обмена данными содержит первый 1 и второй 2 счетчики, блок 3 памяти, узел 4 сравнения, блок 5 определения режима работы, блок 6 определения переполнения, блок 7 управления, входы 8-10 устройства, входные-выходные ршны 11 и 12 устройства, выходы 13 и 14 устройства, входы 15-18 блоков 3 и 6, выход 19 узла сравнения, выходы 20 и 21 блока определения режима работы выходы 22-29 блоков 6 и 7.

Блок 6 определения переполнения предназначен для определения момента заполнения блока 3 памяти данными и содержит первый 30 и второй 31 элементы И-ИЛИ и триггер 32.

Блок 5 определения режима работы (фиг. 3) предназначен для выработки сигналов, разрешающих запись байтов данных в блок 3 памяти или чтение данных из него. Клок 5 содержит триггер 33, первый 34 и второй 35 элементы И-ИЛИ.

Блок 7 управления предназначен для управления работой устройства и содержит первый 36 и второй 37 элементы И-ИЛИ, первый 38 и второй 3 триггеры, генератор 40 импульсов, девятый 41, десятый 42, одиннадцатый 43, двенадцатый 44, тринадцатый 43, четырнадцатый 46, первый 47, второй 48, третий 49, четвертый 50, пятый 51, шестой 52, седьмой 53, восьмой 54 элементы И, второй 55 и первый 56 элементы ИЛИ, элемент НЕ 57, выходы 58 и 59 генератора 40 импульсов.

Блок 3 памяти предназначен для временного хранения байтов данных, поступающих в него по первой 11

или второй 12 входной-вькодной шинам устройства, реализован на микросхеме К1800РП6 и содержит первый 60 и второй 61 усилители считывания, первый 62 и второй 63 регистры, первый 64 и второй 65 формирователи записи, матрицу 66 памяти двойного доступа, первый 67 и второй 68 формирователи шин. Первый 15 и второй 17 входы блока соединены соответственно с первым и вторым входами матрицы 66 памяти. Третий 24 и четвертый 25 входы блока соединены с вторыми входами соответственно второго 65 и первого 64 формирователей записи, выходы которых соединены соответственно с четвертым и третьим входами матрицы 66 памяти. Пятый 26 и шестой 27 входы блока соединены с вторыми входами соответственно первого 62 и второго 63 регистров, выходы которых соединены с вторыми входами соответственно первого 67 и второго 68 формирователей шин. Седьмой 28 и восьмой 29 входы блока соединены с первыми входами соответственно второго 68 и первого 67 формирователей шин. Выход первого формирователя 67 шин соединен с первым входом первого формирователя 64 записи и с первой входной-выходной шиной 11 блока. Выход формирователя 68 шин соединен с первым входом второго формирователя 65 записи и с второй входной-выходной шиной 12 блока. Первый и второй выходы матрицы 66 памяти соединены с входами соответственно первого 60 и второго 6.1 усилителей считывания, выходы которых соединены с первыми вxoдa m соответственно первого 62 и второго 63 регистров.

Устройство для обмена данными работает следующим образом.

Устройства, обменивающиеся информацией, например ОП и ВУ, используют двухадресный блок 3 памяти для временного хранения передаваемых данных. Первая входная-выходная шина 11 и первый счетчик 1 используются оперативной памятью соответственно для записи-считывания данных и для адресации блока 3 памяти. Вторая входная-выходная шина 12 и второй счетчик 2 используются аналогично внешним устройством.

Таким образом, и ОП и ВУ могут считать и писать данные в блок 3 памятп одновременно по .разным адресам и шниам независимо друг от друга. Причем, если одна шина работает в режиме записи, то вторая шина в режиме чтения. Режим работы шин 11 и 12 (запись или чтение) определяет сигнал выбор направления передачи данных, поступающий через первый вход 8 устройст ва на информационный вход блока 6 определения переполнения и первый вход блока 7 управления. Единичное значение этого сигнала определяет направление передачи данных из ВУ в ОП. При этом первая шина 11 устройства работает в режиме чтения x.j ирая iiiHita 12 - в режиме записи. При этом блок 7 управления вырабаты вает на своем девятом выходе 29 сиг нал, поступающий на второй вход раз решения выдачи блока 3 памяти и раз реигающий выдачу содержимого первого регистра 62 блока 3 памяти на шину Нулевое значение сигнала .на первом входе 8 устройства определяет направление передачи данных из ОП Б ВУ. При этом первая шина 11 устро ства работает в режиме записи, а вторая шина 12 - в режиме чтения. При этом блок 7 управления вырабатывает на своем восьмом выходе 28 сигнал, поступающий на первый вход разреиюния блока 3 памяти и ра.зрешающий выдачу содержимого втсфого регистра 63 блока 3 памяти на шину 12. Рассмотрим работу устройства, на пример, в режиме передачи данных из ВУ в ОП. По запросу, поступающему из ВУ через вход 9 запроса устро ства на второй вход блока 7 управления при наличии на выходе 20 сигнала разрешения записи, вьфабатывае мого блоком 5 разрешения записи-чте ния и поступающего на четвертый вход блока 7 управления, блок 7 выр батывает на выходе 24 сигнал записи информации с шины 12, по котором информация с шины 12 записывается в блок 3 памяти по адресу, поступаю щему с входа 17 счетчика 2 на второй адресный вход блока 3 памяти. .После этого блок 7 управления вырабатывает сигнал модификации адреса, по которому содержимое счетчика 2 увеличивается на +1. Одновременно сигнал модификации адреса поступает на второй управляющий выход 14 устройства, сообщая ВУ, что данные приняты в устройство и их можно снимать с шины 12. Аналогичным образом в блок 3 памяти записываются следующие байты данных. Параллельно с процессом записи данных в блок 3 памяти по запросам из ОП происходит процесс считывания записанных данных из блока 3 памяти и передачи их в ОП. Запрос из ОП поступает через вход 10 запроса устройства на третий вход блока 7 управления. Блок 7 управления при наличии на выходе 21 сигнала разрешения чтения, вырабатываемого блоком 5 определения чтения-записи и поступающего на пятый вход блока 7 управления, вырабатывает на выходе 26 сигнал чтения данных на шину 11, по которому в первый регистр 62 блока 3 памяти заносится информация из ячейки матрицы 66 памяти, адрэс которой определяется содержимым счетчика 1, поступающим на первый адресный вход 15 блока 3 памяти. Содержимое регистра 11 передается на шину 11. После этого блок 7 управления выра-. батывает сигнал модификации адреса, по которому содержимое счетчика 1 увеличивается на +1. Одновременно сигнал модификатдаи адреса поступает на первь)й управляющий выход 14 устройства, сообщая ОП, что на ши|не 11 находятся данные, которые можно записать в ОП. Аналогичным образом из. блока 3 памяти считываются остальные байты данных, ранее записанные в него с шины 12. В режиме передачи данных из ОП в ВУ по запросам, поступающим на вход 10 запроса устройства из ОП, блок 7 управления вырабатывает на своем пятом выходе 25 сигналы записи информации с шины 11, по которым информация с шины 11 записывается в блок 3 памяти по адресу, поступающему с выхода счетчика 1 на первый адресный вход блока 3 памяти. По запросам, поступающим на вход 9 запроса устройства из БУ, блок 7 управления вьфабатывает на своем седьмом вг.тходе 27 сигналы чтения данных на шину 12, по которым во второй регистр 63 блока 3 памяти заносится информация из ячейки матрицы 66 памяти, адрес которой определяется содержимым счетчика 2, поступаю1дим на второй адресный вход 17 блока памяти. Модификация счетчиков 1 и 2 и выработка ответных сигналов на вы ходах 13 и 1i в СП и в ВУ производи ся так же, как и в режиме передачи данных из ВУ в ОТТ. В начальный момент времени содер жимое счетчиков 1 и 2 равно нулю. Разрядность счетчиков такова, что по достижении переполнения они внов адресуют нулевую ячейку 3 памяти. Блок 6 определения переполнения устанавливает на выходе 22 сигнал переполнения в тот момент времени, когда счетчик, адресующий ячейку пись данных, вырабатывает сигнал переполнения. Сигнал переполнения сбрасывается в тот момент времени, когда счетчик, адресующий ячейку памяти, из которой производится счи тывание данных, вырабатывает сигнал переполнения. Блок 5 определения режима работы для выработки сигналов разрешения записи и разрешения чтения анализирует сигналы на выходах 19 и 22 с выходов узла 4 сравнения и блока определения переполнения для предот вращения записи данных в занятую ячейку и чтения данных из пустой ячейки г блока 3 памяти. При этом возможны три ситуации (фиг. 6). Ситуация 1. Адрес считывания не равен адресу записи, т.е. обращ ние к блоку 3 памяти для записи и считывания производится по разным адресам. В этом случае на выходе 1 узла 4 сравнения сигнал отсутствуе и блок 5 определения режима работы вырабатывает на выходе 20 сигнал разрешения записи и на выходе 21 сигнал разрешения чтения независимо о состояния выхода 22 блока 6 определ ния переполнения, позволяя одновре менно записывать данные в блок 3 п мяти и считывать из него ранее зап санные данные. Си- уация 2. Адрес записи равен адресу считывания (имеется единичн сигнал на выходе 19 узла 4 сравнени и отсутствует сигнал на выходе 22 блока 6 переполнения. Это означает что все данные, ранее записанные в блок 3 памяти, уже прочитаны из него. Поэтому блок 5 определения режима работы вырабатывает в этом случае только сигнал разрешения записи. Ситуация 3. Адрес записи равен адресу считывания (имеется единичный сигнал на вьгходе 19 узла 4 сравнения) и присутствует единичный сигнал на выходе 22 блока 6 переполнения. Это означает, что блок 3 памяти полностью заполнен данными и записывать новые данных некуда. В этом случае блок 5 определения режима работы вырабатывает только сигнал разрешения считывания . В первой ситуации (фиг. 6) при наличии сигналов разрешения записи 20 и разрешения чтения 21 и появлении запросов 9 и 10 по синхроимпульсу 23 устанавливаются в единичное состояние триггер 38 режима записи и триггер 39 режима чтения. Блок 7 управления в ответ на установку триггера 38 вьщает сигнал 24 записи информации с шины 12 в матрицу 66 памяти и сигнал 14 для модификации второго счетчика 2 на +1 и сброса обслуженного запроса 9, а по триггеру 39 - сигнал 26 чтения информации на шину 11 и сигнал 13 для модификации первого счетчика 1 на +1 и сброса запроса 10. Во второй ситуации в единичное состояние устанавливается только триггер 38 режима записи, а триггер 39 режима чтения не устанавливается, так как отсутствует сигнал 21 разрешения чтения. В результате обслуживания запроса 9 сбрасывается сигнал 19, так как адреса становятся различными и появляется сигнал 21 разрешения чтения, позволяя установить триггер 39 режима чтения для обслуживания запроса 10. В третьей ситуации первым обслуживается запрос 10, а затем запрос 9. Блок 6 определения переполнения работает следующим образом. В режиме передачи данных из ВУ в ОП (единичный сигнал на входе 8 блока) по сигналу переноса из счетчика 2, поступающему на вход 18 блока, устанавливается триггер 32, вырабатывая сигнал 22 9ереполнения. По сигналу переноса из счетчика 1, поступающему на вход 16 блока, триггер 32 сбрасывается и сигнал 22 переполнения снимается. В режиме передачи данных из ОП в ВУ (отсутствие единичного сигнала на входе 8 блока) триггер 32 устанавливается по сигналу переноса из счетчика 1, поступающему на вход 16 блока, а сбрасывается по си налу переноса из счетчика 2, поступающему на вход 18 блока. Блок 5 определения режима работы работает следующим образом. При отсутствии сигнала равенства адресо поступаюп1его на вход 19 блока, по заднему фронту синхросигнала, вырабатываемого блоком 7 управления и поступающего на выход 23 блока, три гер 33 устанавливается в нулевое состояние. По нулевому состоянию триггера 33 элементы И-ИЛИ 34 и 35 7зырабатывают сигналы разрешения записи и разрешения чтения, поступа щие на выход блока. Таким образом, если адреса записи и чтения не равны, разрешается одновременное обращение к блоку 3 памяти и одновремен ное вьтолнение операций чтения и записи. При наличии сигнала равенства адресов на входе 19 блока по переднему фронту синхросигнала, поступаю щего на вход 23 блока, устанавливае ся триггер 33. По установленному триггеру 33 и наличию сигнала переполр ен ш, поступающего -на. вход блока, вырабатывается только сигнал 21 разз ешения чтения. По установленному триггеру 33 и отсутствию сигнала пе реполнения вырабатывается только сигнал 20 разрешения записи. Блок 7 управления работает следую щим образом. Б режиме передачи данньк из ВУ в ОП (единичный сигнал на входе 8 блока) вырабатывается сигнал 29 разрешения вьщачи. информации на шину 11. При наличии запроса, приходящего из ВУ на вход 9 блока, и сигнала разрешения записи, приходя щего 1га вход блока, по синхросигналу 23 устанавливается тоиггер 38. Одновременно синхросигнал 23 поступа ет через первый выход блока на синхронизируюрдий вход блока 5 определения режима работы. По установленному триггеру 38 и синхросигналу 58, вырабатываемому генератором 40 синхроимпульсов элементы И 43 и 47 вырабатывают сигнал 24 записи информации в блок 3 памяти с шины 12. По синхросигналу 59, вырабатываемому генератором 40 импульсов, элементы И 44, 49 и элемент РШИ 55 вырабатывают сиг нал 14, по которому модифицируется счетчик 2. Одновременно сигнал 14 поступает в ВУ, сообщая ему, что байт данньх записан в блок 3 памяти. По этому сигналу ВУ с некоторой задержкой снимает запрос 9, По следующему синхросигналу 23 сбрасывается триггер 38. При наличии запроса, приходящего из ОП на вход 10 блока, и при наличии сигнала разрешения чтения, приходящего на вход 21 блока, устанавливается триггер 39. По установленному триггеру 39 и синхросигналу 58 элементы И 46 и 53 вырабатывают сигнал 26 чтения информахщи из блока 3 памяти на шину 11. По синхросигналу 59 элементы И 45 и 51 и элемент ИЛИ 56 вырабатывают сигнал 13, по которому модифицируется счетчик 1, Одновременно сигнал 13 поступает в ОП, сообщая ей, что байт находится на шине 11. По этому сигналу ОП с некоторой задержкой снимает запрос 10. По следующему синхросигналу 23 сбрасывается триггер 39. В режиме передачи данных из ОП в ВУ (нулевой сигнал на входе 8 блока) на вьЬсоде 28 вырабатывается сигнал разрешения вьщачи информации на щину 12. При наличии запроса, приходящего из ОП на вход 10 блока, и сигнала разрешения записи, приходящего на вход 20, по синхросигналу 23 устанавливается триггер 38, По установленному триггеру 38 и синхросигналу 58 элементы И 43 и 48 вырабатывают на выходе 25 сигнал записи информации в блок 3 памяти с шины 11, По синхросигналу 59 элементы И 44 и 50 и элемент ИЛИ 56 вырабатывают сигнал 13, по которому модифи1щруется счетчик 1. Одновременно сигнал 13 поступает в ОП, сообщая ей, что байт данных записан в блок 3 памяти. При наличии запроса, приходящего из ВУ на вход 9, и сигнала разрешения чтения, приходящего на вход 21 блока, по синхросигналу 23 устанавливается триггер 39. По установленному триггеру 39 и синхросигналу 58 элементы И 46 и 54 вырабатывают на выходе 27 чтения информации из блока 3 / памяти на шину 12. По синхросигналу 59 элементы И 42 и 52 и элемент ИЛИ 55 вырабатывают сигнал 14, по которому модифицируется счетчик 2. Одновременно сигнал 14 поступает в БУ, сообщая ему, что байт данных находит ся на т}ше 12. Блок 3 памяти работает следующим образом. В режиме передачи данных из ВУ в ОП на выходе 29 присутствует сигнал разрешения выдачи данных на шину 11 и отсутствует на выходе 28 сигнал разрешения вьщачи данных на ну 12. По сигналу, поступающему на выход 24 блока, формирователь 65 за писи разрешает запись данных с шины 12 в матрицу 66 памяти двойного доступа по адресу, поступающему на вход 17 блока. Информация из ячейки матрицы 66 памяти двойного доступа, адрес которой поступает на вход 15 блока, через усилитель 6 считывания поступает на вход регист ра 62 и по сигналу, поступающему на вход 26 блока, записывается в регистр 62. Затем из регистра 62 через формирователь 67 шин информация поступает на шину 11. В режиме передачи данных из ОП в ВУ на выходе 28 присутствует сигнал и на выходе 29 отсутствует. По сигналу, поступающему на вход 25 блока формирователь 64 записи разрешает запись данных с шины 11 в ма рицу 66 памяти двойного доступа по адресу, поступающему на вход 15 блока. Информация из матрицы 66 памяти двойного доступа, адрес котор поступает на вход 17 блока, через усилитель 61 считывания поступает

г, / )6

22

9- W

.8

13

п

г-1

2| г

21

75

2Ч 25. 1.

27

Ж1 23

JL а вход регистра 63 и по сигналу, оступающему на вход 27 блока, записывается в регистр 63. Затем из регистра 63 через формирователь 68 шин информация поступает на шину 12. Особенностью блока 3 памяти является то, что он позволяет одновременно и независимо друг от друга производить обращение, к матрице 66 памяти двойного доступа с шин 11 и 12. Применение данного изобретения позволит повысить пропускную способность блок-мультиплексных ипи селекторных каналов, так как при выполнении операции ввода данных одновременно записываются в блок памяти байты данных из интерфейса ввода-вывода и считываются из блока памяти в оперативную память ранее записанные данные, а при выполнении операции вывода данных одновременно записываются в блок памяти байты данных из оперативной памяти и считываются из блока памяти в интерфейс вводавывода ранее записанные данные. Кроме того, наличие возможности одновременного обращения к блоку памяти по двум шинам упрощает структуру блока управления. Поэтому затраты оборудования на реализацию данного устройства меньше, чем затраты оборудования на реализацию известного.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Устройство для сопряжения интерфейсов ввода-вывода с регистратором | 1987 |

|

SU1413636A1 |

| Устройство для запоминания состояний процессора | 1985 |

|

SU1278858A1 |

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1119019A1 |

1. УСТРОЙСТВО ДЛЯ ОБМЕНА ЛАНИЫ Ш МЕЖЛУ ОПЕРАТИВНОЙ ПАМЯТЬЮ И ВНЕШНШ УСТР()Р СТВОМ, содержащее узел сравнения, блок памяти и два счетчика, причем первый и второй информационные входы-выходы блока памяти соединены соответственно с информационными шинами оперативной памяти и внешнего устройства, выходы первого и второго счетчиков соединены с первым и вторым адресными входами блока памяти соответственно, отличающееся тем, что, с целью повышения быстродействия, в него введены блок определения переполнения, блок определения режима работы, блок управления, причем первый и второй выходы блока управления соединены со счетными вxoдa и второго счетчиков и управляющими входами оперативной памяти и внешнего устройства соответственно, управляющий вход блока определения переполнения соединен с первым входом блока управления и является входом выбора направления обмена устройства, второй и третий входы блока управления соединены с выходами запроса внешнего устройства и оперативной памяти соответственно, при этом П1.гходы первого и второго счетчиков соединены с первым и вторым входами узла сравнения соответственно, выход которого соединен с информационным входом блока определения режима работы, выходы разрешения записи и считывания которого соединены с четвертым и пятым входами блока управления соответственно, третий выход которого соединен с синхровходом блока определения режима работы, вход переполнения которого соединен с выходом блока определения переполнения, первый и втоi рой информационные входы которого (Л соединены с выходами переполнения первого и второго счетчиков соответственно, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока управления соединены с первым и вторым входами записи, первым и вторым входами чтения, первым и вторым входами разрешения вьщачи бло00 ка памяти соответственно, при этом о со о блок управления содержит генератор импульсов, два триггера, два элемента И-ИЛИ, четырнадцать элементов И, 00 два элемента ИЛИ и элемент НЕ, причем первый и второй входы первого и второго элементов И-ИЛИ соединены с первыми входами первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого элементов И, входом элемента НЕ и являются первым входом и девятым выходом блока управления, третьи входы первого и второго элементов И-ИЛИ образуют второй вход блока управления, четвертые входы первого и второго элементов ИИЛИ образуют третий вход блока управ

12

Я

| Патент США f 3643221, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Устройтво для обмена данными | 1977 |

|

SU691830A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-04-16—Подача