Изобретение относится к области вычислительной техники, в частности, к устройствам обмена данными. Оно может быть использовано в качестве буфера данных для каналов ввода-вывода ЭВМ.

Цель изобретения - расширение области применения, упрощение структуры устройства, уменьшение затрат оборудования для организации общего буфера данных для группы каналов ввода-вывода.

Сущность изобретения заключается в том, что для расширения области применения, упрощения структуры, уменьшения затрат оборудования структура устройства для обмена данными между оперативной памятью и периферийными устройствами основана на использовании регистров с двунаправленными входами-выходами и двух- входовых полупроводниковых памятей с двунаправленными входами-выходами.

Эта структура позволила соединить двунаправленными магистралями блоки хранения данных, управляющей информации соответственно с канальными регистровыми блоками накопления данных и блоками модификации управляющей информации и управления.

В режиме разделения времени на бесприоритетной основе проводится использование общего оборудования хранения данных, управляющей информации, модификации, управления при работе полупроводниковых памятей по порту В с регистровыми буферами данных каналов.

00 ND О CJ 00

Работа по порту А полупроводниковых памятей в режиме передачи данных производится на приоритетной основе для тех каналов, которые накопили в общем буфере данные, необходимые для обмена с опера- тивной памятью.

При реализации такого устройства были разработаны регистровые буферы, блок формирования циклов обслуживания, регистровый файл (РФ), блок модификации пор- та В РФ, блок адресации порта В БП, блок управления порта В БП, блок модификации порта А РФ, блок управления А БП, блок управления порта А РФ, блок связи с ОП.

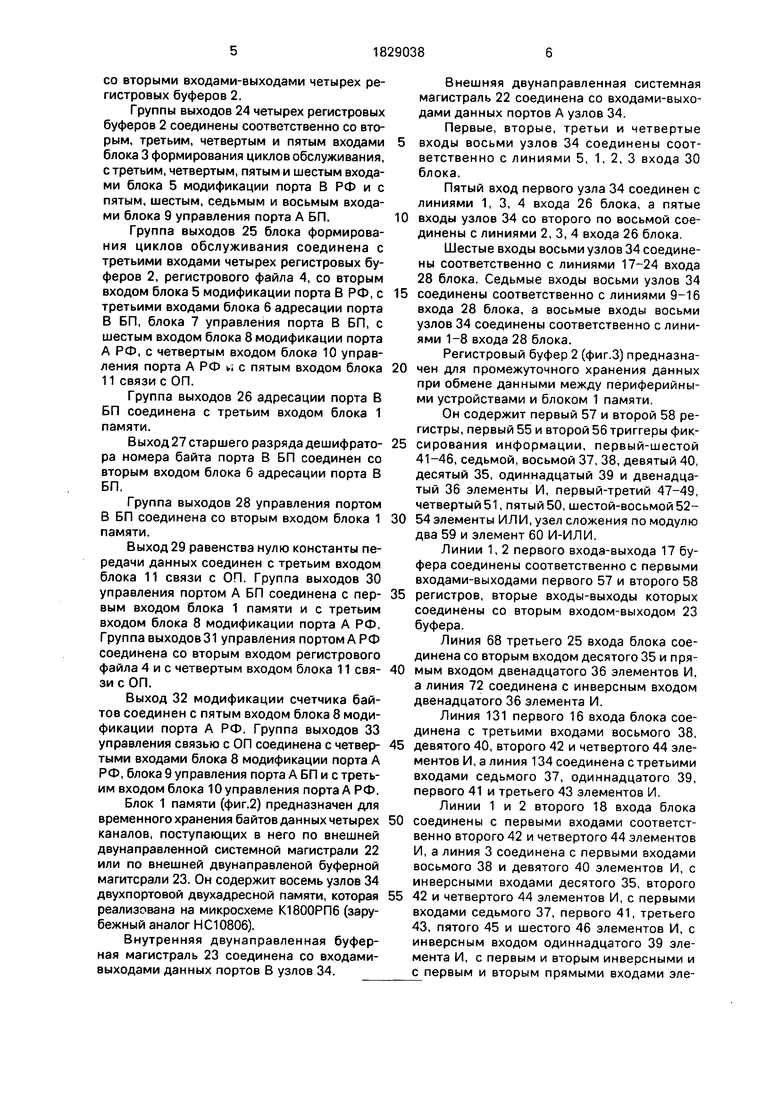

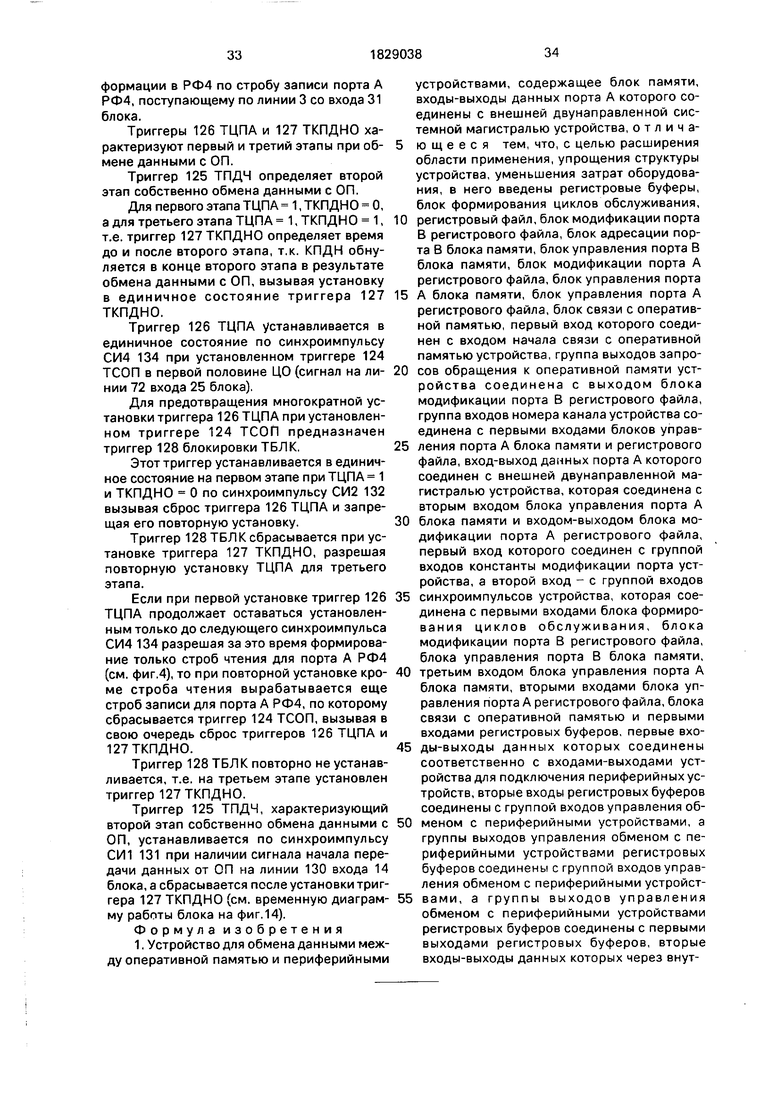

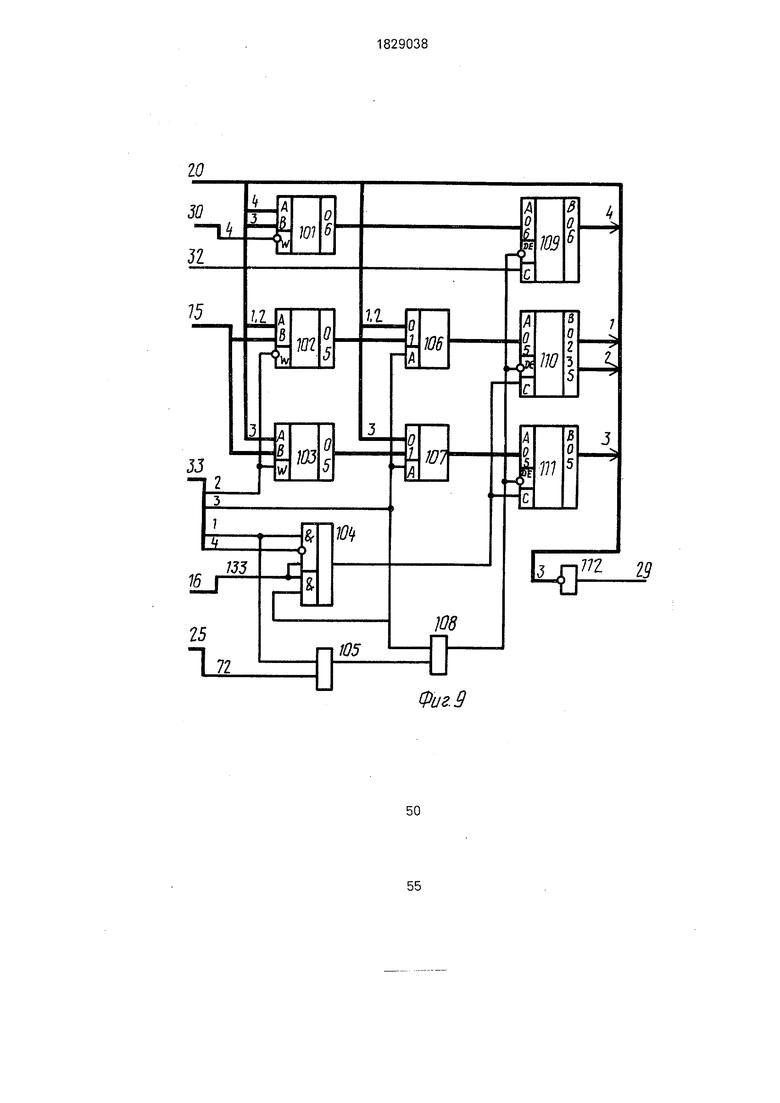

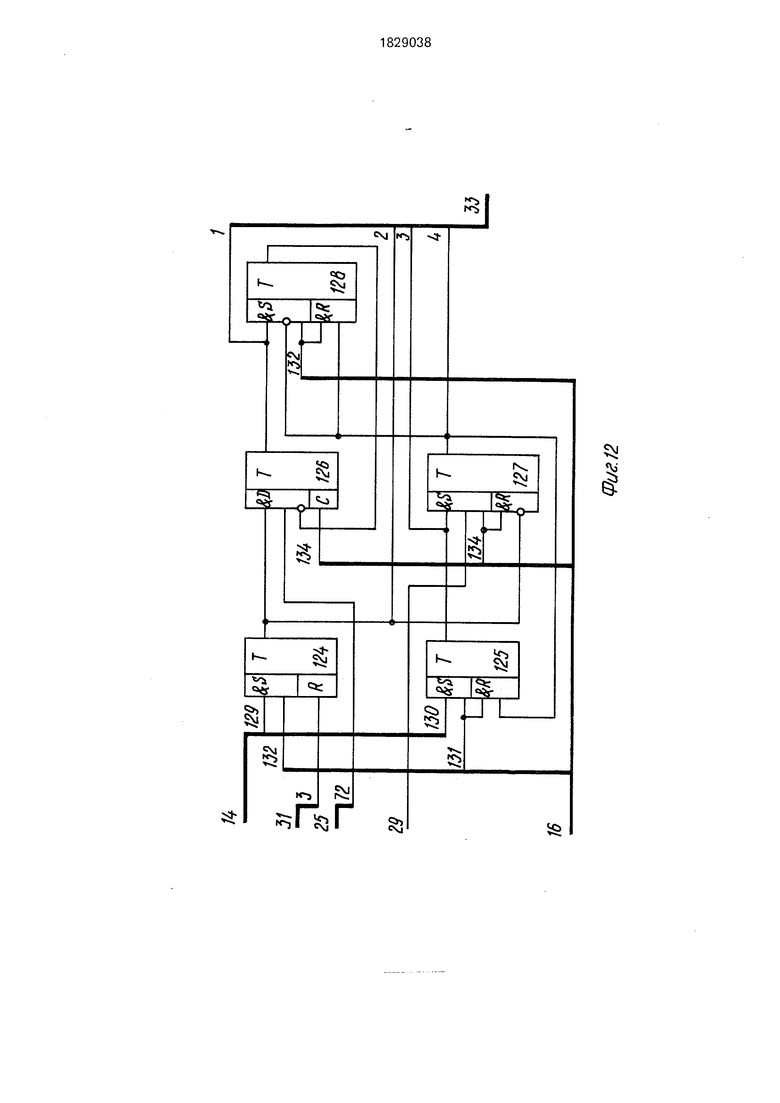

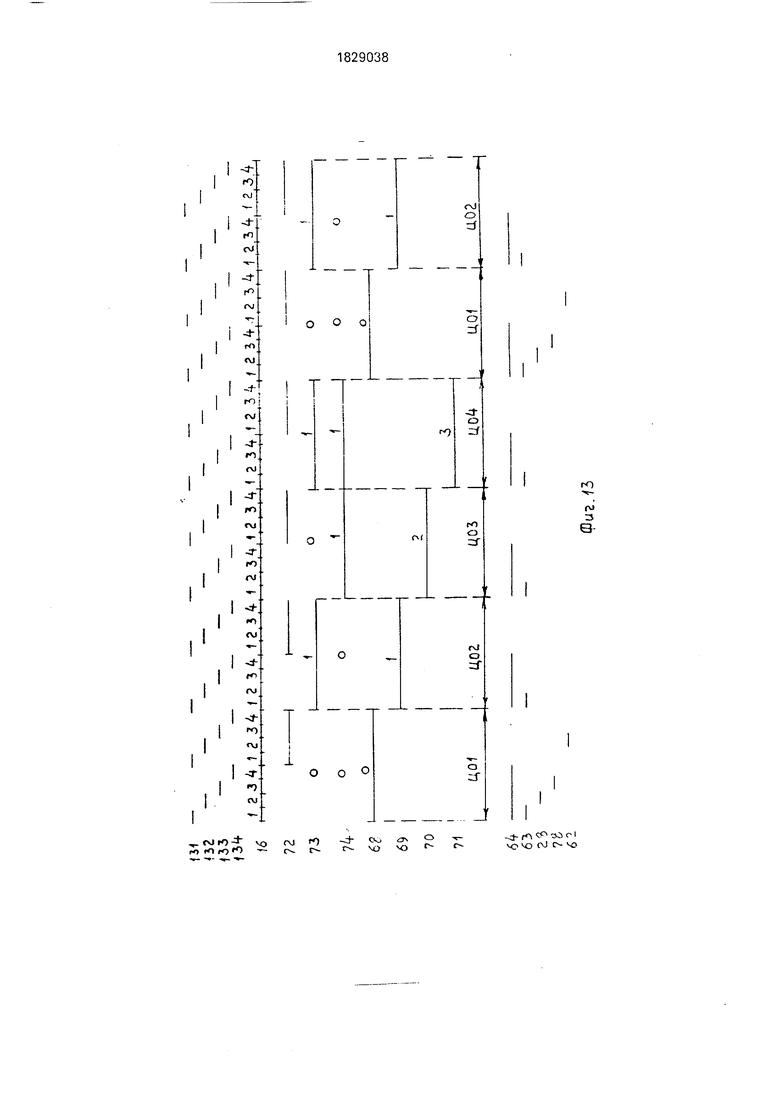

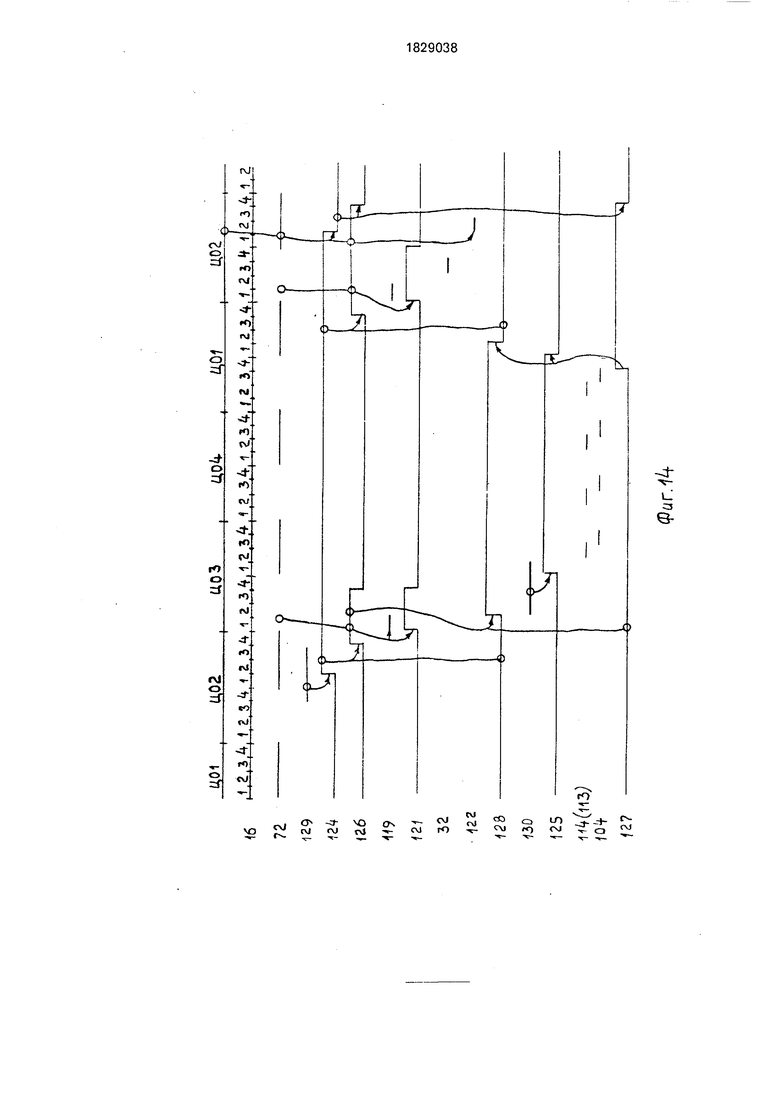

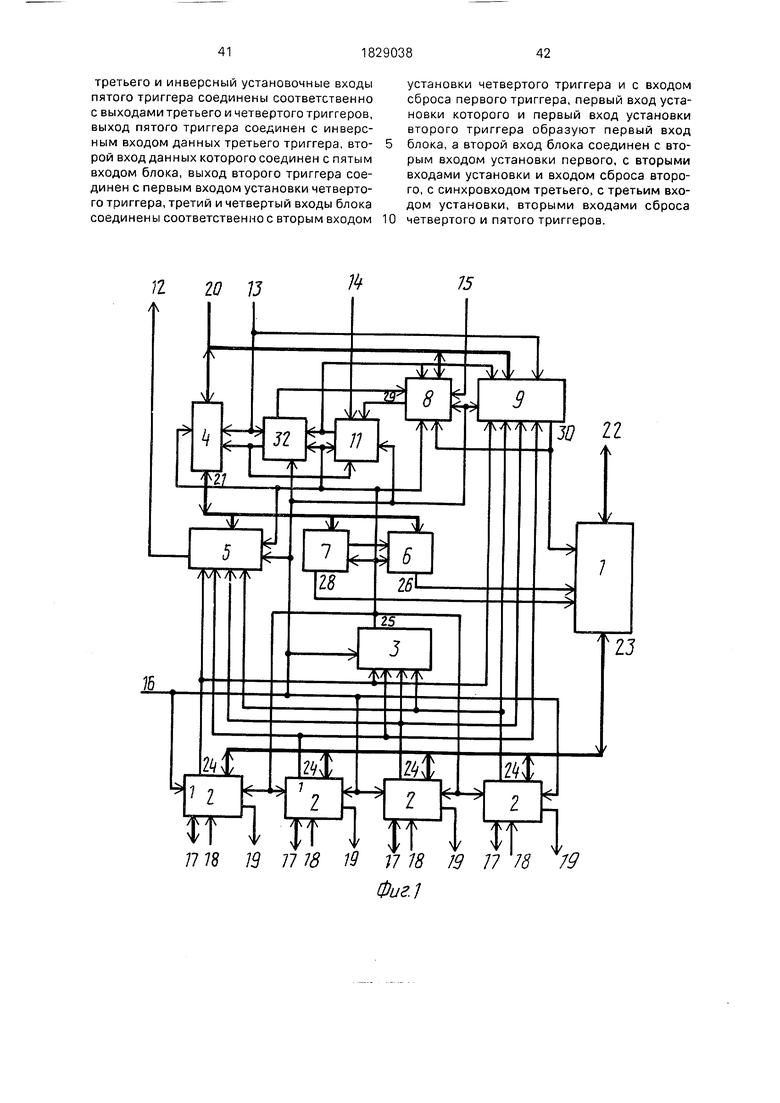

На фиг.1 представлена блок-схема уст- ройства Для обмена данными между оперативной памятью и периферийными устройствами; на фиг.2 - блок памяти; на фиг.З - регистровый буфер; на фиг.4 - блок формирования циклов обслуживания; на фиг.5 - регистровый файл; на фиг.6 - блок модификации порта В РФ; на фиг.7 - блок адресации порта В БП; на фиг.З - блок управления порта В БП; на фиг.9 - блок модификации порта А РФ; на фиг.10 - блок управления порта АБП: на фиг.11 - блок управления порта А РФ; на фиг.12 - блок связи с О.П; на фиг.13 - временная диаграмма обмена данными между регистровыми буферами и портом В блока памяти; на фиг.14 - временная диаграмма обмена данными между ОП и портом А блока памяти; на фиг.15 - распределение и адресация зон блока памяти и регистрового файла между каналами.

Устройство для обмена данными содержит блок 1 памяти, четыре регистровых буфера 2, блок 3 формирования циклов обслуживания, регистровый файл 4, блок 5 модификации порта В РФ, блок 6 адресации порта В БП, блок 7 управления порта В БП, блок 8 модификации порта А РФ, блок 9 управления порта А БП, блок 10 управления порта А РФ, блок 11 связи с ОП, группу выходов 12 запросов обращения к ОП, труп- пу входов 13 номера канала, вход 14 начала связи с ОП, группу входов 15 константы модификации порта А, группу входов 16 синхроимпульсов, входы-выходы 17 устройства для подключения периферийных устройств, четыре группы входов 18 управления обменом с ПФУ, четыре группы выходов 19 управления обменом с ПФУ, внешнюю двунаправленную магистраль 20 устройства, двунаправленную магистраль 21 порта В РФ, внешнюю двунаправленную системную магистраль 22, внутреннюю двунаправленную буферную магистраль 23, четыре группы выходов 24 четырех регистровых буферов, группу выходов 25 блока формирования циклов обслуживания, группу выходов 26 адресации порта В БП, выход 27 старшего разряда дешифратора номера байта порта В БП, группу выходов 28 управления портом В БП, выход 29 равенства нулю константы передачи данных, группу выходов 30 управления портом А БП, группу выходов 31 управления портом А РФ, выход 32 модификации счетчика байтов, группу выходов 33 управления связью с ОП.

Группа выходов 12 запросов обращения и ОП соединена с выходом блока 5 модификации порта В РФ. Группа входов 13 номера канала соединена с первыми входами регистрового файла 4, блока 9 управления порта А БП и блока 10 управления порта А РФ. Вход 14 начала связи с ОП соединен с первым входом блока 11 связи с ОП. Группа входов 15 константы модификации порта А соединена с первым входом блока 8 модификации порта А РФ. Группа входов 16 син- хроимпульсов соединена с первыми входами четырех регистровых буферов 2, блока 3 формирования циклов обслуживания, блока 5 модификации порта В РФ, блока 7 управления порта В БП, со вторым входом блока 8 модификации порта А РФ, с третьим входом блока 9 управления порта А БП, со вторыми входами блока 10 управления порта А РФ и блока 11 связи с ОП. Первые входы-выходы данных четырех регистровых буферов 2 соединены соответственно со входами-выходами 17 устройства для подключения периферийных устройств.

Четыре группы входов 18 управления обменом с ПФУ соединены со вторыми входами соответствующих регистровых буферов 2. Четыре группы выходов 19 управления обменом с ПФУ соединены с выходами управления обменом соответствующих регистровых буферов 2.

Внешняя двунаправленая магистраль 20 устройства соединена со входами-выходами данных регистрового файла 4, со входами-выходами блока 8 модификации порта А РФ и со вторым входом блока 9 управления порта А БП.

Двунаправленная магистраль 21 порта В РФ регистрового файла 4 соединена со входами-выходами данных блока 5 модификации порта В РФ, с первым входом блока 6 адресации порта В БП и со вторым входом блока 7 управления порта В БП.

Внешняя двунаправленная системная магистраль 22 соединена со входами-выходами данных порта А блока 1 памяти.

Внутренняя двунаправленная буферная магистраль 23 соединена со входами- выходами данных порта В блока 1 памяти и

со вторыми входами-выходами четырех регистровых буферов 2.

Группы выходов 24 четырех регистровых буферов 2 соединены соответственно со вторым, третьим, четвертым и пятым входами блока 3 формирования циклов обслуживания, с третьим, четвертым, пятым и шестым входами блока 5 модификации порта В РФ и с пятым, шестым, седьмым и восьмым входами блока 9 управления порта А БП.

Группа выходов 25 блока формирования циклов обслуживания соединена с третьими входами четырех регистровых буферов 2, регистрового файла 4, со вторым входом блока 5 модификации порта В РФ, с третьими входами блока 6 адресации порта В БП, блока 7 управления порта В БП, с шестым входом блока 8 модификации порта А РФ, с четвертым входом блока 10 управления порта А РФ fi с пятым входом блока 11 связи с ОП.

Группа выходов 26 адресации порта В БП соединена с третьим входом блока 1 памяти.

Выход 27 старшего разряда дешифратора номера байта порта В БП соединен со вторым входом блока 6 адресации порта В БП.

Группа выходов 28 управления портом В БП соединена со вторым входом блока 1 памяти.

Выход 29 равенства нулю константы передачи данных соединен с третьим входом блока 11 связи с ОП. Группа выходов 30 управления портом А БП соединена с первым входом блока 1 памяти и с третьим входом блока 8 модификации порта А РФ. Группа выходов 31 управления портом А РФ соединена со вторым входом регистрового файла 4 и с четвертым входом блока 11 связи с ОП.

Выход 32 модификации счетчика байтов соединен с пятым входом блока 8 модификации порта А РФ. Группа выходов 33 управления связью с ОП соединена с четвертыми входами блока 8 модификации порта А РФ, блока 9 управления порта А БП и с третьим входом блока 10 управления порта А РФ.

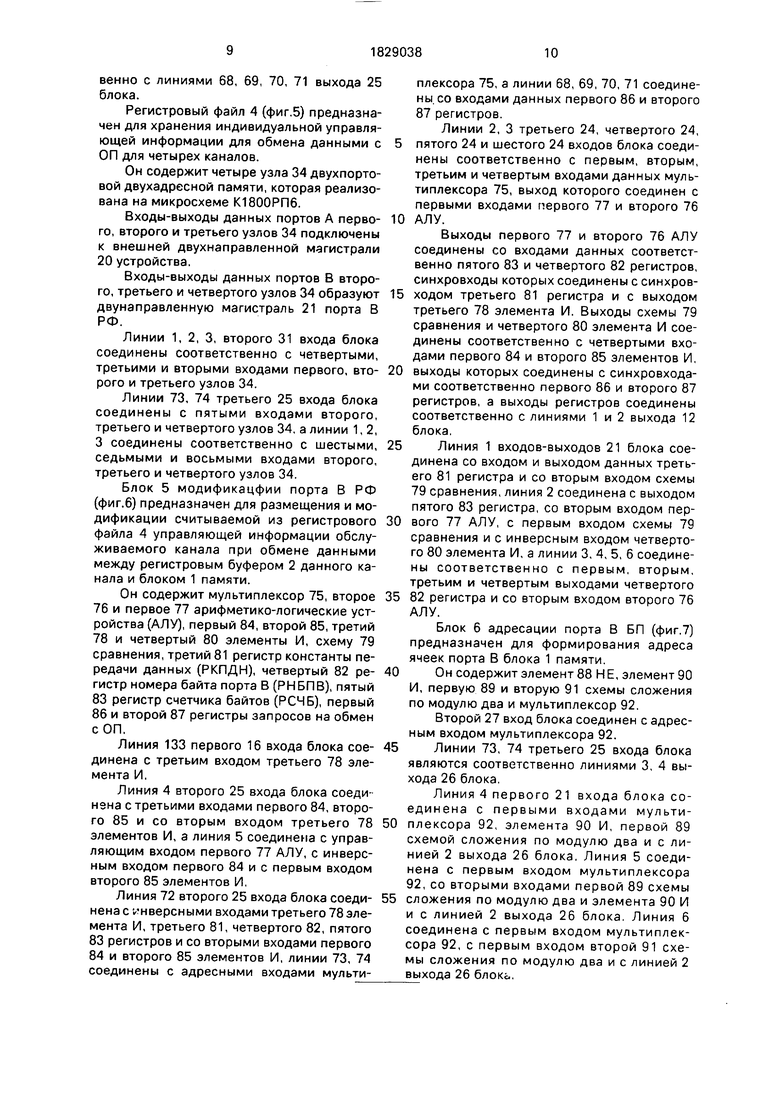

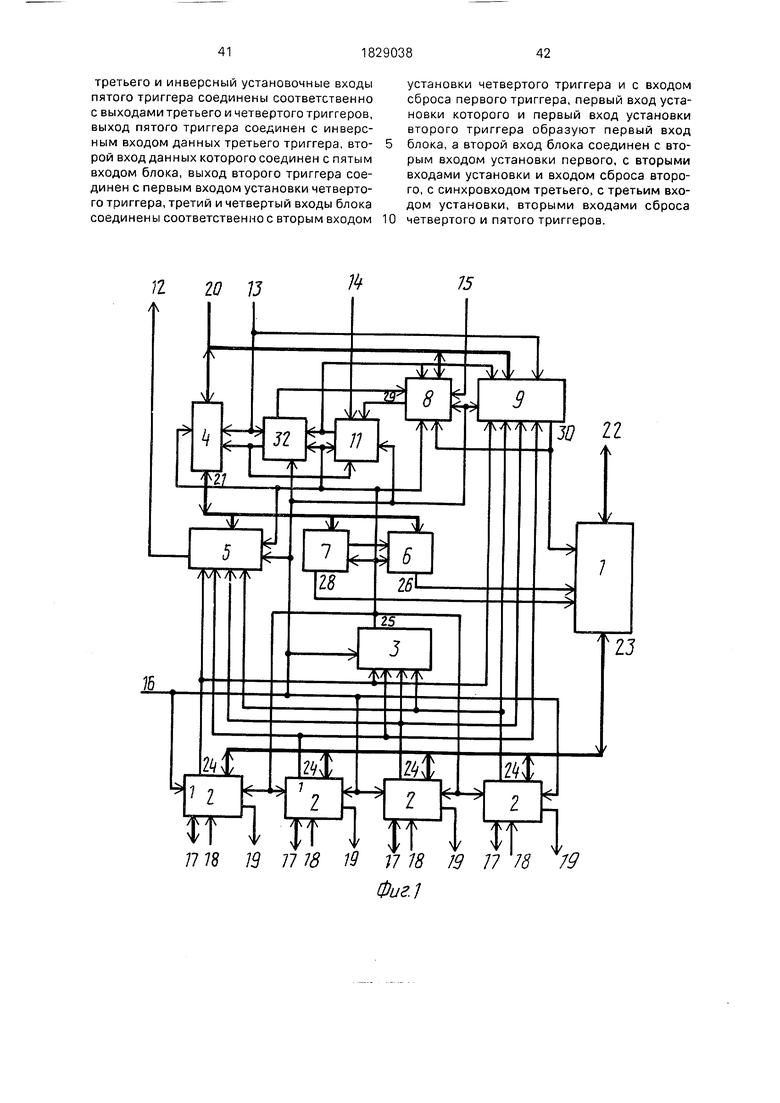

Блок 1 памяти (фиг.2) предназначен для временного хранения байтов данных четырех каналов, поступающих в него по внешней двунаправленной системной магистрали 22 или по внешней двунаправленой буферной магитсрали 23. Он содержит восемь узлов 34 двухпортовой двухадресной памяти, которая реализована на микросхеме К1800РП6 (зарубежный аналог НС10806).

Внутренняя двунаправленная буферная магистраль 23 соединена со входами- выходами данных портов В узлов 34.

Внешняя двунаправленная системная магистраль 22 соединена со входами-выходами данных портов А узлов 34.

Первые, вторые, третьи и четвертые

входы восьми узлов 34 соединены соответственно с линиями 5, 1, 2, 3 входа 30 блока.

Пятый вход первого узла 34 соединен с линиями 1, 3, 4 входа 26 блока, а пятые

0 входы узлов 34 со второго по восьмой соединены с линиями 2, 3, 4 входа 26 блока,

Шестые входы восьми узлов 34 соединены соответственно с линиями 17-24 входа 28 блока. Седьмые входы восьми узлов 34

5 соединены соответственно с линиями 9-16 входа 28 блока, а восьмые входы восьми узлов 34 соединены соответственно с линиями 1-8 входа 28 блока.

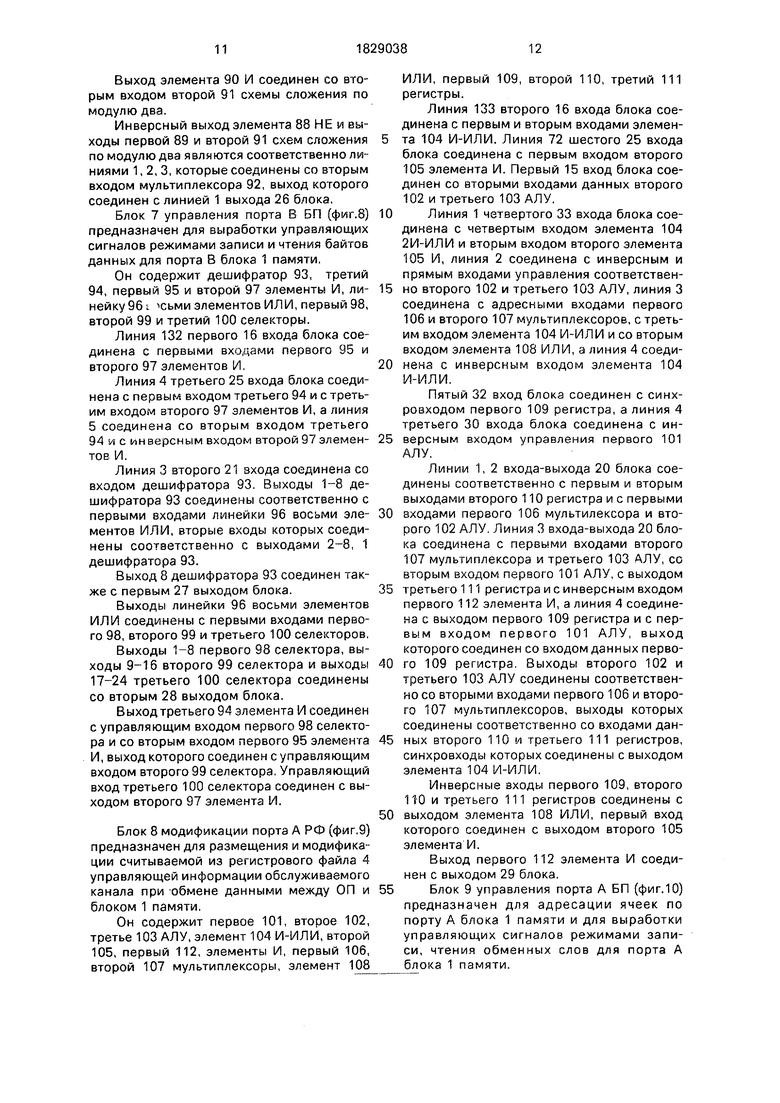

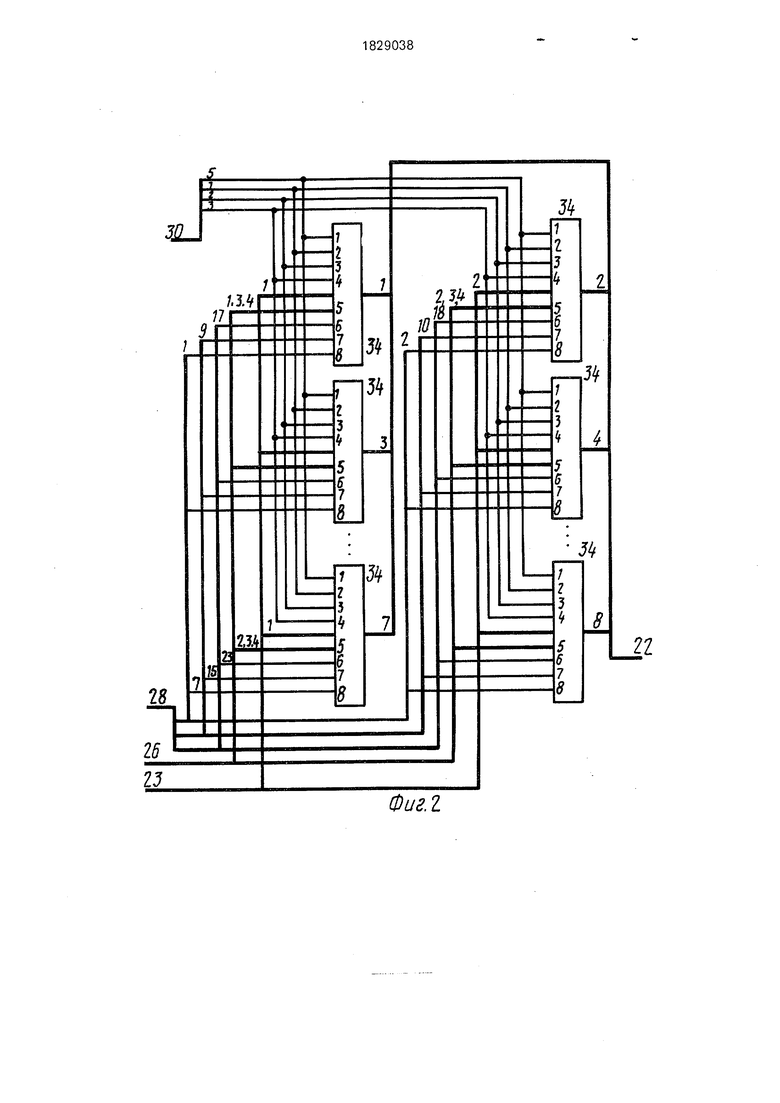

Регистровый буфер 2 (фиг.З) предназна0 чен для промежуточного хранения данных при обмене данными между периферийными устройствами и блоком 1 памяти.

Он содержит первый 57 и второй 58 регистры, первый 55 и второй 56 триггеры фик5 сирования информации, первый-шестой 41-46, седьмой, восьмой 37, 38, девятый 40, десятый 35, одиннадцатый 39 и двенадцатый 36 элементы И, первый-третий 47-49, четвертый 51, пятый 50, шестой-восьмой 520 54 элементы ИЛИ, узел сложения по модулю два 59 и элемент 60 И-ИЛИ.

Линии 1, 2 первого входа-выхода 17 буфера соединены соответственно с первыми входами-выходами первого 57 и второго 58

5 регистров, вторые входы-выходы которых соединены со вторым входом-выходом 23 буфера.

Линия 68 третьего 25 входа блока соединена со вторым входом десятого 35 и пря0 мым входом двенадцатого 36 элементов И, а линия 72 соединена с инверсным входом двенадцатого 36 элемента И.

Линия 131 первого 16 входа блока соединена с третьими входами восьмого 38,

5 девятого 40, второго 42 и четвертого 44 элементов И, а линия 134 соединена с третьими входами седьмого 37, одиннадцатого 39, первого 41 и третьего 43 элементов И.

Линии 1 и 2 второго 18 входа блока

0 соединены с первыми входами соответственно второго 42 и четвертого 44 элементов И, а линия 3 соединена с первыми входами восьмого 38 и девятого 40 элементов И, с инверсными входами десятого 35, второго

5 42 и четвертого 44 элементов И, с первыми входами седьмого 37, первого 41, третьего 43, пятого 45 и шестого 46 элементов И, с инверсным входом одиннадцатого 39 элемента И, с первым и вторым инверсными и с первым и вторым прямыми входами элемента 60 И-ИЛИ, с первыми входами регистров 57, 58 и с линией 1 выхода 24 блока.

Линия 4 второго 18 входа блока соединена со вторыми входами восьмого 38 и пятого 45 элементов И, а линия 5 соединена со вторыми входами и девятого 40 и шестого 46 элементов И.

Выход десятого 35 элемента И соединен с первыми входами седьмого 53 и восьмого 54 элементов ИЛИ, а выход две- надцатого 36 элемента И соединен со вторыми входами седьмого 37, первого 41, и третьего 43 элементов И и с первым входом одиннадцатого 39 элемента И.

Выхо седьмого 37 элемента И соеди- нен со вторыми входами третьего 49 и четвертого 51 элементов ИЛИ, а выход одиннадцатого 39 элемента И соединен со вторыми входами пятого 50 и шестого 52 элементов ИЛИ,

Выходы восьмого 38 и девятого 40 элементов И соединены соответственно с первыми входами пятого 50 и шестого 52 элементов ИЛИ.

Выходы первого 41 и третьего 43 эле- ментов И соединены соответственно с первыми входами первого 47 и второго 48 элементов ИЛИ.

Выход второго 42 элемента И соединен со вторым входом первого 47 и с первым входом третьего 49 элементов ИЛИ, а выход четвертого 44 элемента И соединен со вторым входом второго 48 и с первым входом четвертого 51 элементов ИЛИ.

Выходы пятого 45 и шестого 46 элемен- тов И соединены соответственно со вторыми входами седьмого 53 и восьмого 54 элементов ИЛИ, выходы которых соединены соответственно с инверсными входами первого 57 и второго 58 регистров.

Выходы первого 47 и второго 48 элементов ИЛИ соединены соответственно со вторыми входами первого 57 и второго 58 регистров,

Выходы третьего 49 и пятого 50 элемен- тов ИЛИ соединены соответственно с первым и вторым входами первого 55 триггера, а выходы четвертого 51 и шестого 52 элементов ИЛИ соединены соответственно с первым и вторым входами второго 56 тригг- гера.

Выход первого 55 триггера соединен с первым входом узла 59 сложения по модулю два, с инверсным входом первого 41 элемента И, с третьим прямым и третьим инвер- сным входами элемента 60 И-ИЛИ и с линией 1 выхода 19 управления обменом блока.

Выход второго 56 триггера соединен со вторым входом узла 59 сложения по модулю

два, с инверсным входом третьего 43 элемента И, с четвертым прямым и четвертым инверсным входами элемента 60 И-ИЛИ и с линией 2 выхода 19 блока.

Первый и второй инверсный выходы узла 59 сложения по модулю два соединены соответственно с линиями 2, 3, а выход элемента 60 И-ИЛИ и с линией 4 группы 24 выходов блока.

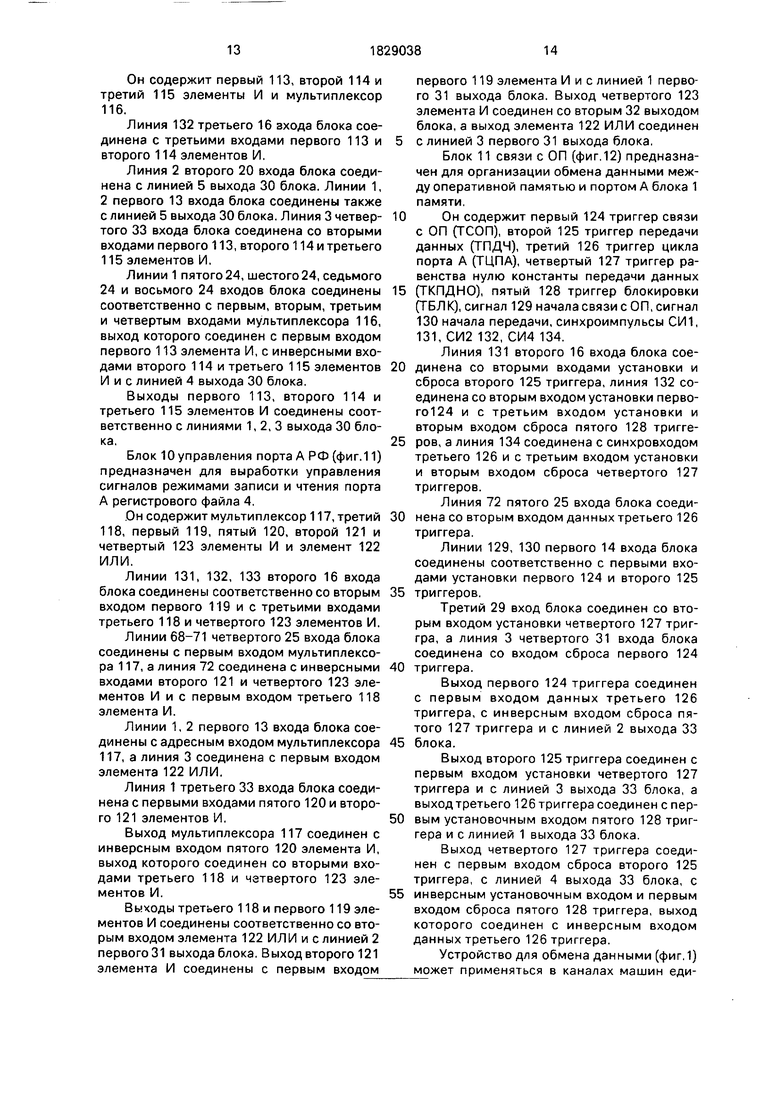

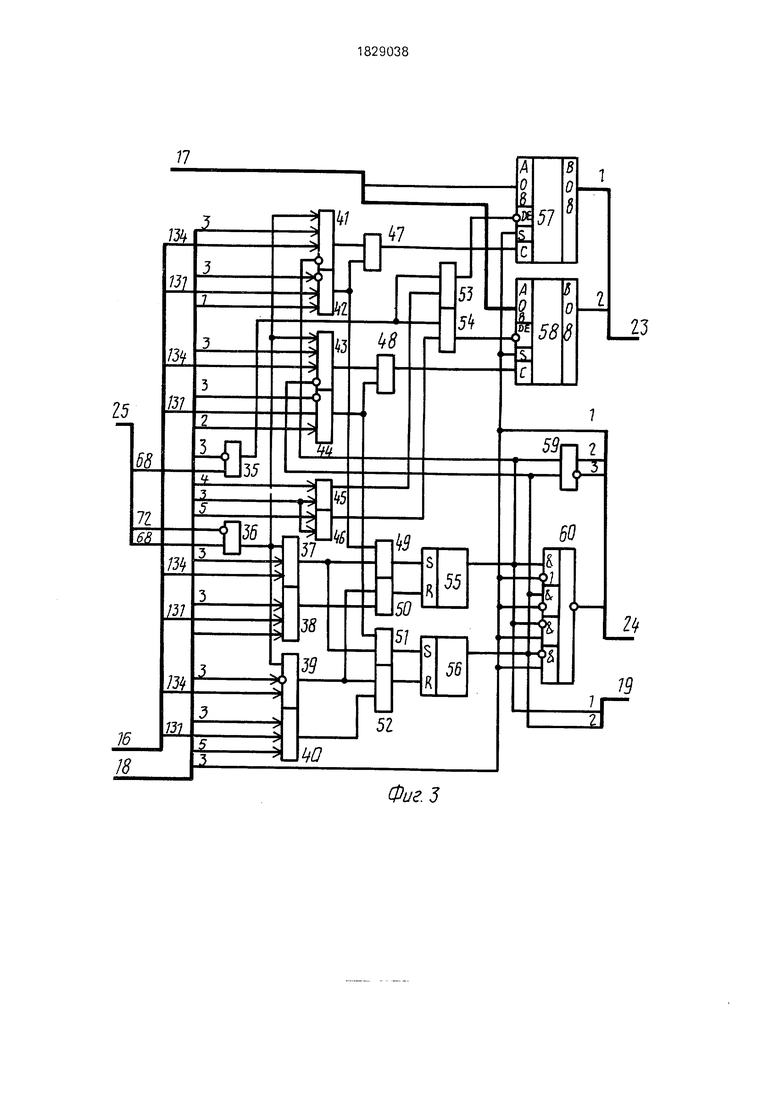

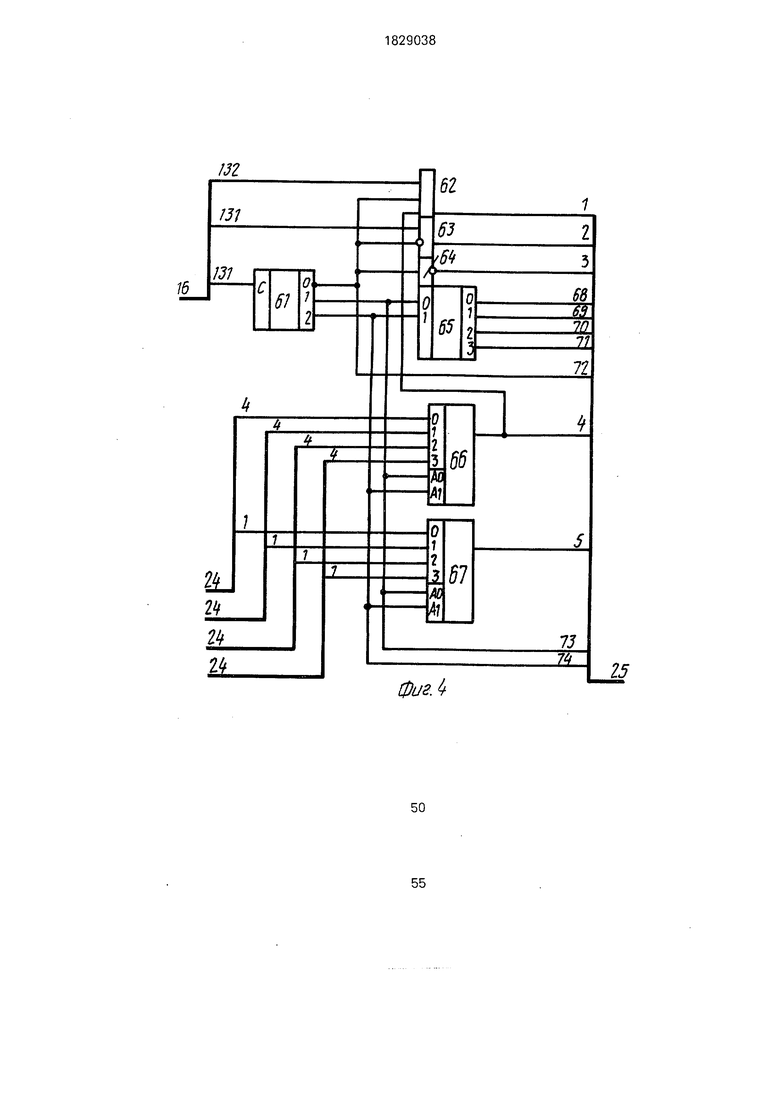

Блок 3 формирования циклов обслуживания (фиг.4) предназначен для выработки циклов поочередного обслуживания четырех каналов при обмене данными между регистровыми буферами 2 и блоком 1 памяти, а также для адресации зон четырех каналов блока 1 памяти и регистрового файла 4,

Он содержит счетчик 61, первый 62, второй 63 элементы И, элемент 64 НЕ, дешифратор 65, первый 66 и второй 67 мультиплексоры.

Линия 131 первого 16 входа блока соединена со входом счетчика 61 и со вторым входом второго 63 элемента И, а линия 132 соединена со вторым входом первого 62 элемента И.

Линия 4 второго 24, третьего 24, четвертого 24 и пятого 24 входов блока соединены соответственно с первым, вторым, третьим и четвертым входами первого 66 мультиплексора, а линии 1 соединены соответственно с первым, вторым, третьим и четвертым входами второго 67 мультиплексора.

Выход первого 66 мультиплексора соединен с третьим входом первого 62 элемента И и с линией 4 выхода 25 блока, а выход второго 67 мультиплексора соединен с линией 5 выхода 25 блока.

Первый выход счетчика 61 соединен с первым входом первого 62 и инверсным входом второго 63 элементов И, со входом элемента 64 НЕ и с линией 72 выхода 25 блока.

Второй выход счетчика 61 соединен с первым входом дешифратора 65 и с первыми адресными входами первого 66, второго 67 мультиплексоров и с линией 73 выхода 25 блока.

Третий выход счетчика 61 соединен со вторым входом дешифратора 65, со вторыми адресными входами первого 66 и второго 67 мультиплексоров и с линией 74 выхода 2Е блока.

Выходы первого 62 и второго 63 элементов И соединены соответственно с линиями 1, 2, а выход элемента 64 НЕ с линией 3 выхода 25 блока.

Первый, второй, третий и четвертый выходы дешифратора 65 соединены соответственно с линиями 68, 69, 70, 71 выхода 25 блока.

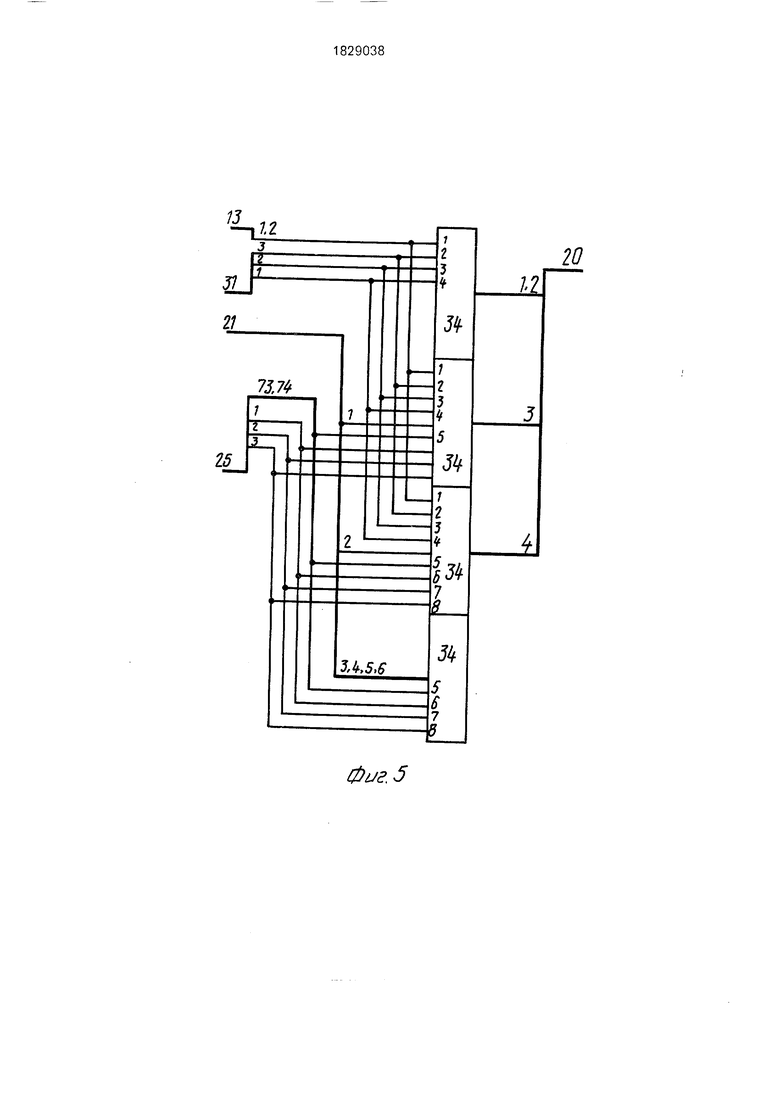

Регистровый файл 4 (фиг.5) предназначен для хранения индивидуальной управляющей информации для обмена данными с ОП для четырех каналов.

Он содержит четыре узла 34 двухпортовой двухадресной памяти, которая реализована на микросхеме К1800РП6.

Входы-выходы данных портов А первого, второго и третьего узлов 34 подключены к внешней двухнаправленной магистрали 20 устройства.

Входы-выходы данных портов В второго, третьего и четвертого узлов 34 образуют двунаправленную магистраль 21 порта В РФ.

Линии 1, 2, 3, второго 31 входа блока соединены соответственно с четвертыми, третьими и вторыми входами первого, второго и третьего узлов 34.

Линии 73, 74 третьего 25 входа блока соединены с пятыми входами второго, третьего и четвертого узлов 34, а линии 1, 2, 3 соединены соответственно с шестыми, седьмыми и восьмыми входами второго, третьего и четвертого узлов 34.

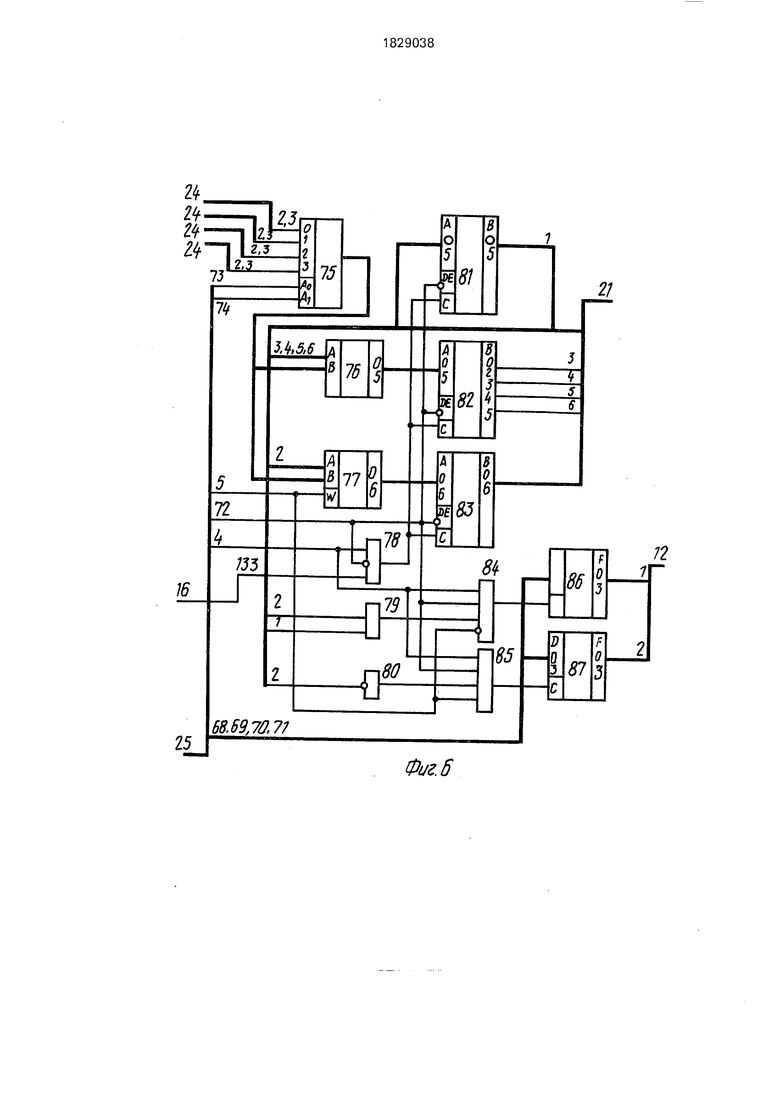

Блок 5 модификацфии порта В РФ (фиг.6) предназначен для размещения и модификации считываемой из регистрового файла 4 управляющей информации обслуживаемого канала при обмене данными между регистровым буфером 2 данного канала и блоком 1 памяти.

Он содержит мультиплексор 75, второе 76 и первое 77 арифметико-логические устройства (АЛУ), первый 84, второй 85, третий 78 и четвертый 80 элементы И, схему 79 сравнения, третий 81 регистр константы передачи данных (РКПДН), четвертый 82 регистр номера байта порта В (РНБПВ), пятый 83 регистр счетчика байтов (РСЧБ), первый 86 и второй 87 регистры запросов на обмен сОП.

Линия 133 первого 16 входа блока соединена с третьим входом третьего 78 элемента И.

Линия 4 второго 25 входа блока соединена с третьими входами первого 84, второго 85 и со вторым входом третьего 78 элементов И, а линия 5 соединена с управляющим входом первого 77 АЛУ, с инверсным входом первого 84 и с первым входом второго 85 элементов И,

Линия 72 второго 25 входа блока соединена с инверсными входами третьего 78 элемента И, третьего 81, четвертого 82, пятого

83регистров и со вторыми входами первого

84и второго 85 элементов И, линии 73, 74 соединены с адресными входами мультиплексора 75, а линии 68, 69, 70, 71 соединены, со входами данных первого 86 и второго 87 регистров.

Линии 2, 3 третьего 24, четвертого 24, пятого 24 и шестого 24 входов блока соединены соответственно с первым, вторым, третьим и четвертым входами данных мультиплексора 75, выход которого соединен с первыми входами первого 77 и второго 76

0 АЛУ.

Выходы первого 77 и второго 76 АЛУ соединены со входами данных соответственно пятого 83 и четвертого 82 регистров, синхровходы которых соединены с синхров5 ходом третьего 81 регистра и с выходом третьего 78 элемента И. Выходы схемы 79 сравнения и четвертого 80 элемента И соединены соответственно с четвертыми входами первого 84 и второго 85 элементов И,

0 выходы которых соединены с синхровхода- ми соответственно первого 86 и второго 87 регистров, а выходы регистров соединены соответственно с линиями 1 и 2 выхода 12 блока.

5 Линия 1 входов-выходов 21 блока соединена со входом и выходом данных третьего 81 регистра и со вторым входом схемы 79 сравнения,линия 2 соединена с выходом пятого 83 регистра, со вторым входом пер0 вого 77 АЛУ, с первым входом схемы 79 сравнения и с инверсным входом четвертого 80 элемента И, а линии 3, 4, 5, 6 соединены соответственно с первым, вторым, третьим и четвертым выходами четвертого

5 82 регистра и со вторым входом второго 76 АЛУ.

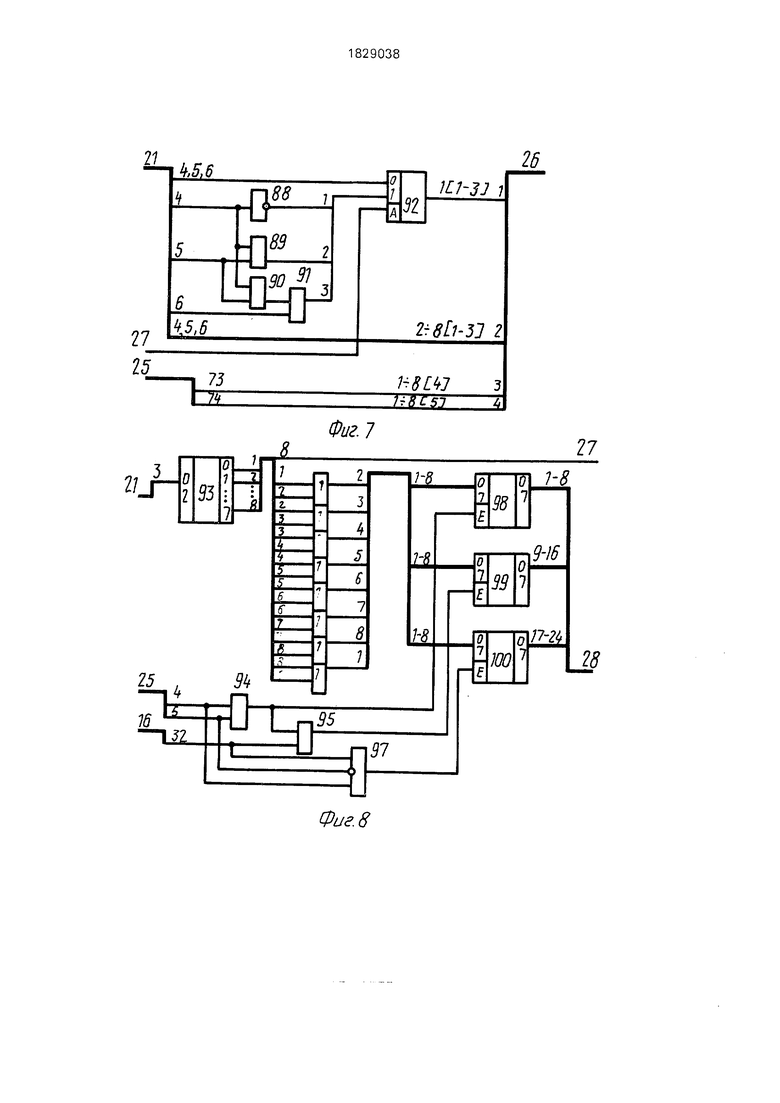

Блок 6 адресации порта В БП (фиг.7) предназначен для формирования адреса ячеек порта В блока 1 памяти.

0Он содержит элемент 88 НЕ, элемент 90

И, первую 89 и вторую 91 схемы сложения по модулю два и мультиплексор 92.

Второй 27 вход блока соединен с адресным входом мультиплексора 92.

5 Линии 73, 74 третьего 25 входа блока являются соответственно линиями 3, 4 выхода 26 блока.

Линия 4 первого 21 входа блока соединена с первыми входами мульти0 плексора 92, элемента 90 И, первой 89 схемой сложения по модулю два и с линией 2 выхода 26 блока. Линия 5 соединена с первым входом мультиплексора 92, со вторыми входами первой 89 схемы

5 сложения по модулю два и элемента 90 И и с линией 2 выхода 26 блока. Линия 6 соединена с первым входом мультиплексора 92, с первым входом второй 91 схемы сложения по модулю два и с линией 2 выхода 26 блоке..

Выход элемента 90 И соединен со вторым входом второй 91 схемы сложения по модулю два.

Инверсный выход элемента 88 НЕ и выходы первой 89 и второй 91 схем сложения по модулю два являются соответственно линиями 1,2,3, которые соединены со вторым входом мультиплексора 92, выход которого соединен с линией 1 выхода 26 блока,

Блок 7 управления порта В БП (фиг.8) предназначен для выработки управляющих сигналов режимами записи и чтения байтов данных для порта В блока 1 памяти.

Он содержит дешифратор 93, третий 94, первый 95 и второй 97 элементы И, линейку 961 элементов ИЛ И, первый 98, второй 99 и третий 100 селекторы.

Линия 132 первого 16 входа блока соединена с первыми входами первого 95 и второго 97 элементов И,

Линия 4 третьего 25 входа блока соединена с первым входом третьего 94 и с третьим входом второго 97 элементов И, а линия 5 соединена со вторым входом третьего 94 и с инверсным входом второй 97 элементов И.

Линия 3 второго 21 входа соединена со входом дешифратора 93. Выходы 1-8 дешифратора 93 соединены соответственно с первыми входами линейки 96 восьми элементов ИЛИ, вторые входы которых соединены соответственно с выходами 2-8, 1 дешифратора 93.

Выход 8 дешифратора 93 соединен также с первым 27 выходом блока.

Выходы линейки 96 восьми элементов ИЛИ соединены с первыми входами первого 98, второго 99 и третьего 100 селекторов.

Выходы 1-8 первого 98 селектора, выходы 9-16 второго 99 селектора и выходы 17-24 третьего 100 селектора соединены со вторым 28 выходом блока.

Выход третьего 94 элемента И соединен с управляющим входом первого 98 селектора и со вторым входом первого 95 элемента И, выход которого соединен с управляющим входом второго 99 селектора, Управляющий вход третьего 100 селектора соединен с выходом второго 97 элемента И.

Блок 8 модификации порта А РФ (фиг.9) предназначен для размещения и модификации считываемой из регистрового файла 4 управляющей информации обслуживаемого канала при -обмене данными между ОП и блоком 1 памяти.

Он содержит первое 101, второе 102, третье 103 АЛУ, элемент 104 И-ИЛИ, второй 105, первый 112, элементы И, первый 106, второй 107 мультиплексоры, элемент 108

ИЛИ, первый 109, второй 110, третий 111 регистры.

Линия 133 второго 16 входа блока соединена с первым и вторым входами элемента 104 И-ИЛИ. Линия 72 шестого 25 входа блока соединена с первым входом второго 105 элемента И. Первый 15 вход блока соединен со вторыми входами данных второго 102 и третьего 103 АЛУ.

0 Линия 1 четвертого 33 входа блока соединена с четвертым входом элемента 104 2И-ИЛИ и вторым входом второго элемента

105И, линия 2 соединена с инверсным и прямым входами управления соответствен5 но второго 102 и третьего 103 АЛУ, линия 3 соединена с адресными входами первого

106и второго 107 мультиплексоров, с третьим входом элемента 104 И-ИЛИ и со вторым входом элемента 108 ИЛИ, а линия 4 соеди0 йена с инверсным входом элемента 104 И-ИЛИ.

Пятый 32 вход блока соединен с синх- ровходом первого 109 регистра, а линия 4 третьего 30 входа блока соединена с ин5 версным входом управления первого 101 АЛУ.

Линии 1, 2 входа-выхода 20 блока соединены соответственно с первым и вторым выходами второго 110 регистра и с первыми

0 входами первого 106 мультилексора и второго 102 АЛУ. Линия 3 входа-выхода 20 блока соединена с первыми входами второго

107мультиплексора и третьего 103 АЛУ, со вторым входом первого 101 АЛУ, с выходом

5 третьего 111 регистра и с инверсным входом первого 112 элемента И, а линия 4 соединена с выходом первого 109 регистра и с первым входом первого 101 АЛУ, выход которого соединен со входом данных перво0 го 109 регистра. Выходы второго 102 и третьего 103 АЛУ соединены соответственно со вторыми входами первого 106 и второго 107 мультиплексоров, выходы которых соединены соответственно со входами дан5 ных второго 110 и третьего 111 регистров, синхровходы которых соединены с выходом элемента 104 И-ИЛИ.

Инверсные входы первого 109, второго 110 и третьего 111 регистров соединены с

0 выходом элемента 108 ИЛИ, первый вход которого соединен с выходом второго 105 элемента И.

Выход первого 112 элемента И соединен с выходом 29 блока.

5Блок 9 управления порта А БП (фиг.10)

предназначен для адресации ячеек по порту А блока 1 памяти и для выработки управляющих сигналов режимами записи, чтения обменных слов для порта А блока 1 памяти.

Он содержит первый 113, второй 114 и третий 115 элементы И и мультиплексор 116.

Линия 132 третьего 16 входа блока соединена с третьими входами первого 113 и второго 114 элементов И.

Линия 2 второго 20 входа блока соединена с линией 5 выхода 30 блока. Линии 1, 2 первого 13 входа блока соединены также с линией 5 выхода 30 блока. Линия 3 четвертого 33 входа блока соединена со вторыми входами первого 113, второго 114 и третьего 115 элементов И.

Линии 1 пятого 24, шестого 24, седьмого 24 и восьмого 24 входов блока соединены соответственно с первым, вторым, третьим и четвертым входами мультиплексора 116, выход которого соединен с первым входом первого 113 элемента И, с инверсными входами второго 114 и третьего 115 элементов И и с линией 4 выхода 30 блока.

Выходы первого 113, второго 114 и третьего 115 элементов И соединены соответственно с линиями 1, 2, 3 выхода 30 блока.

Блок 10 управления порта А РФ (фиг.11) предназначен для выработки управления сигналов режимами записи и чтения порта А регистрового файла 4.

Он содержит мультиплексор 117, третий 118, первый 119, пятый 120, второй 121 и четвертый 123 элементы И и элемент 122 ИЛИ.

Линии 131, 132, 133 второго 16 входа блока соединены соответственно со вторым входом первого 119 и с третьими входами третьего 118 и четвертого 123 элементов И.

Линии 68-71 четвертого 25 входа блока соединены с первым входом мультиплексора 117, а линия 72 соединена с инверсными входами второго 121 и четвертого 123 элементов И и с первым входом третьего 118 элемента И.

Линии 1, 2 первого 13 входа блока соединены с адресным входом мультиплексора 117, а линия 3 соединена с первым входом элемента 122 ИЛИ.

Линия 1 третьего 33 входа блока соединена с первыми входами пятого 120 и второго 121 элементов И,

Выход мультиплексора 117 соединен с инверсным входом пятого 120 элемента И, выход которого соединен со вторыми входами третьего 118 и четвертого 123 элементов И.

Выходы третьего 118 и первого 119 элементов И соединены соответственно со вторым входом элемента 122 ИЛИ и с линией 2 первого 31 выхода блока. Выход второго 121 элемента И соединены с первым входом

первого 119 элемента И и с линией 1 первого 31 выхода блока. Выход четвертого 123 элемента И соединен со вторым 32 выходом блока, а выход элемента 122 ИЛИ соединен с линией 3 первого 31 выхода блока,

Блок 11 связи с ОП (фиг.12) предназначен для организации обмена данными между оперативной памятью и портом А блока 1 памяти.

0Он содержит первый 124 триггер связи

с ОП (ТСОП), второй 125 триггер передачи данных (ТПДЧ), третий 126 триггер цикла порта А (ТЦПА), четвертый 127 триггер равенства нулю константы передачи данных 5 (ТКПДНО), пятый 128 триггер блокировки (ТБЛ К), сигнал 129 начала связи с ОП, сигнал 130 начала передачи, синхроимпульсы СИ1, 131, СИ2 132, СИ4 134.

Линия 131 второго 16 входа блока сое- 0 динена со вторыми входами установки и сброса второго 125 триггера, линия 132 соединена со вторым входом установки перво- го124 и с третьим входом установки и вторым входом сброса пятого 128 тригге- 5 ров, а линия 134 соединена с синхровходом третьего 126 и с третьим входом установки и вторым входом сброса четвертого 127 триггеров.

Линия 72 пятого 25 входа блока соеди- 0 нена со вторым входом данных третьего 126 триггера.

Линии 129, 130 первого 14 входа блока соединены соответственно с первыми входами установки первого 124 и второго 125 5 триггеров.

Третий 29 вход блока соединен со вторым входом установки четвертого 127 триг- гра, а линия 3 четвертого 31 входа блока соединена со входом сброса первого 124 0 триггера.

Выход первого 124 триггера соединен с первым входом данных третьего 126 триггера, с инверсным входом сброса пятого 127 триггера и с линией 2 выхода 33 5 блока.

Выход второго 125 триггера соединен с первым входом установки четвертого 127 триггера и с линией 3 выхода 33 блока, а выход третьего 126 триггера соединен с пер- 0 вым установочным входом пятого 128 триггера и с линией 1 выхода 33 блока.

Выход четвертого 127 триггера соединен с первым входом сброса второго 125 триггера, с линией 4 выхода 33 блока, с 5 инверсным установочным входом и первым входом сброса пятого 128 триггера, выход которого соединен с инверсным входом данных третьего 126 триггера.

Устройство для обмена данными (фиг. 1) может применяться в каналах машин единой системы в качестве общего буфера данных для нескольких каналов.

В устройстве для обмена данными между ОП и несколькими каналами используется общий блок 1 памяти (БП 1), который разделен на зоны по количеству каналов и регистровые буферы 2 индивидуальные для каждого канала.

В общем случае объем блока памяти, ширина формата обмена, величина блока обмена данными с ОП и количество каналов зависит от заданной пропускной способности для каждого канала. При использовании предлагаемого устройства в составе ЭВМ для единого взаимодействия с ОП и ЦП и устройстг ширина формата обмена и величина блока обмена с ОП выбирается как правило одинаковыми равными, принятым в ЭВМ; величина зоны каждого канала - равной не менее двум, принятым в ЭВМ блоком обмена с ОП.

Для простоты изложения в предлагаемом устройстве ширина формата обмена с ОП равна 8 байтам, максимальный блок обмена данными с ОП равен 4x8 байтов, количество каналов равно 4, величина зоны для каждого канала равна удвоенному блоку обмена, то есть 2x4x8 байтам, а объем блока 1 памяти равен четырем зонам по количеству каналов 4x2x4x8 32x8 байтов,

Блок 1 памяти представляет собой двухадресную двухвходовую (двухпортовую) память емкостью 32x8 байтов, позволяющую вести одновременно обмен данными между БП1 и ОП по порту А и между БП1 и регистровыми буферами 2 четырех каналов по порту В.

БП1 содержит восемь узлов 34, Каждый узел представляет собой двухадресную двухпортовую память емкостью 32x1 байт.

Двунаправленные шины данных портов А восьми узлов 34 образуют восьмибайтовую внешнюю системную магистраль 22 для параллельной записи-чтения восьми байтов данных при обмене между ОП и БП1.

Двунаправленные шины портов В нечетных и четных узлов 34 соединены соответственно с регистрами 57 и 58 регистровых буферов 2 четырех каналов образуя внутреннюю двухбайтовую буферную магистраль 23 для записи-чтения двух байтов данных при обмене данными между БП 1 и регистровыми буферами 2.

Каналы, использующие для хранения данных общий блок 1 памяти, разделяют во времени также и общее оборудование порта В для обслуживания обмена данными между регистровыми буферами 2 и портом В БП1 и общее оборудование порта А для обслуживания обмена между ОП и портом А БП1.

К общему оборудованию порта В относятся блок 5 модификации порта В РФ, блок 5 6 адресации порта В БП и блок 7 управления порта В БП.

К общему оборудованию порта А относятся блок 8 модификации порта А РФ, блок 9 управления порта А БП, блок 10 управле0 ния порта А РФ.

Каждый из четырех каналов разделяет общее оборудование портов А и В при обмене данными, используя при этом индивидуальную управляющую информацию,

5 хранящуюся в регистровом файле 4 (РФ4). Регистровый файл 4 также является двухадресной двухпортовой памятью емкостью 32x4 байта, разделенной на четыре зоны по количеству каналов, которая ис0 пользуется в качестве регистровой памяти для хранения управляющей информации каждого канала.

РФ4 содержит четыре узла 34. Двунаправленные шины данных портов

5 В второго, третьего и четвертого узлов 34 РФ4 образуют двунарпэвленную магистраль 21 порта в РФ, к которой подключено общее оборудование порта В.

Двунаправленные шины данных портов

0 А первого, второго и третьего узлов 34 РФ4 образуют двунаправленную магистраль 20 порта А РФ, которая подключена к общему оборудованию порта А и внешней двунаправленной магистрали 20 устройства.

5В зоне каждого канала в регистровом

файле 4 нулевая строка содержит следующую управляющую информацию для организации обмена данными.

Первый байт содержит константу пере0 дачи данных (КПДН), указывающую количество байтов, которым необходимо обменяться с ОП данному ПФУ за один цикл связи.

Второй байт хранит счетчик байтов дан5 ных(СЧБ), содержащихся в зоне БП1 данного канала.

Нулевой и третий байты хранят соответственно номер байта порта А (НБПА) и номер байта порта В (НБПВ) для адресации

0 нужного байта в зоне по порту А БП1 при обмене данными с ОП и по порту В БП1 при обмене с регистровым буфером 2 данного канала.

Применение в качестве БП1 и РФ4 двух5 адресных двухпортовых памятей позволяет организовать одновременную работу блока 1 памяти по двум портам с разными форматами обмена и разными скоростями, обеспечивая параллельное обслуживание четырех каналов.

Рассмотрим работу устройства при обмене данными с ОП четырех каналов,

Для управления обменом данными предварительно по порту А в РФ4 загружаются по магистрали 20 для четырех каналов исходные значения КПДН, НБПА, НБПВ, СЧБ.

Последовательно меняя информацию на магистрали 20 и номер канала на входе 13 устройства в РФ4 будет записана исходная управляющая информация для четырех каналов.

Исходное значение СЧБ всегда равно нулю. Значения НБПВ, НБПА могут быть не равны нулю, если данные предназначенные для обмена, расположены в ОП не по границе обменного слова, т.е. три младшие разряда адреса данных ОП не равны нулю.

В этом случае исходные значения НБПВ при вводе и НБПА при выводе будут равны трем младшим разрядам адреса данных ОП.

Максимальное значение КПДП равно 32 байтам.

Процесс обмена данными между ОП и каналами можно разделить на три независимые процесса:

обмен данными между периферийными устройствами и регистровыми буферами 2, обмен данными между регистровыми буферами 2 и портом В БП1 и обмен данными портом А БП и ОП.

Обмен данными между периферийными устройствами и соответствующими регистровыми буферами 2 осуществляется параллельно, независимо друг от друга.

Обмен данными между ПФУ и регистровым буфером 2 осуществляется следующим образом.

При выполнении операций ввода байты данных от ПФУ поступают по двунаправленной однобайтовой магистрали 17 в регистровый буфер 2.

Максимальное количество байтов, которое может содержать регистровый буфер 2 равно двум.

Как только в регистровом буфере 2 будет содержаться один или два байта на линии 4 выхода 24 регистрового буфера 2 сформируется запрос на передачу этих байтов в БП1, который выдается в блок 3 формирования циклов обслуживания.

При выполнении операций вывода байты данных из регистрового буфера 2 поочередно выдаются в магистраль 17 в ответ на запросы от ПФУ, поступающие со входа 18 устройства.

Как только из регистрового буфера 2 будет выдан один или два байта данных в ПФУ на линии 4 выхода 24 регистрового буфера 2 формируется запрос на прием новых байтов данных из БП1.

Обмен данными между регистровыми буферами 2 и БП1 осуществляется последовательно в режиме разделения времени.

Порядок обслуживания жестко поочередный.

Для этого каждому из четырех каналов отводится одинаковый интервал времени, называемый циклом обслуживания (ЦО) данного канала.

Циклы обслуживания для четырех каналов Ц01-Ц04 вырабатываются непрерывно и строго поочередно соответственно на линиях 68-71 выхода 25 блока 3 формирования

циклов обслуживания.

Длительность циклов обслуживания определена системой синхронизации, применяемой в устройстве. В предлагаемом устройстве используются четыре серии синхросигналов СИ1-СИ4, 131-134, вырабатывающихся последовательно друг за другом с минимальной задержкой относительно друг друга, равной длительности импульса.

Тогда длительность каждого цикла обслуживания равна двум периодам следования синхросигналов. Временная диаграмма выработки циклов обслуживания приведена на фиг. 13.

Блок 3 формирования циклов обслуживзния вместе с циклами обслуживания вырабатывают также адреса зон на линиях 73, 74 выхода 25 для портов В БП1 и РФ4 для адресации на время цикла обслуживания зон БП1 и РФ4 нужного канала.

Циклы обслуживания управляют также разделением буферной магистрали 23 между четырьмя каналами.

Регистровые буферы 2 могут выдавать данные в буферную магистраль 23 при выполнении операций ввода только в цикле своего канала, вне цикла регистровые буферы 2 отключены от магистрали 23.

Прием данных из буферной магистрали 23 в регистровые буферы 2 разрешен только

в цикле своего канала.

Каждый цикл обслуживания делится пополам сигналом на линии 72 выхода 25 блока 3 формирования циклов обслуживания.

Первая половина каждого ЦО отводится

для режима чтения РФ4, а вторая половина для режима записи в РФ4.

В начале циклов обслуживания блок 3 формирования циклов обслуживания вырабатывает на линии 2 выхода 25 строб чтения

для порта В ФР4, а на линии 3 сигнал разрешения выходов порта В РФ4.

Считываемая по порту В РФ4 управляющая информация адресуемого канала выдается в магистраль 21 и воздействует на

общее оборудование порта В.

По НБПВ блок 6 адресации порта В БП вырабатывает адрес строки в зоне обслуживаемого канала, а блок 7 управления порта В БП при выполнении операций ввода вырабатывает на линиях 17-24 выхода 28 два строба записи для записи двух байтов данных в адресуемую строку БП1 из регистрового буфера 2, а при выполнении операций вывода вырабатываются стробы чтения на линиях9-16 и сигналы разрешения выходов на линиях 1-8 выхода 28 для чтения и выдали двух байтов адресуемой строки БП1 в буферную магистраль 23 и последующей их записи в регистровый буфер 2 обслуживаемого канала.

Затем рисутствующие на входе блока 5 модификации порта В РФ НБПВ и СЧБ промодифицируются в блоке на величину константы модификации порта В (КМВ) обслуживаемого канала.

КМВ отражает количество байтов, которым обменялся регистровый буфер 2 с БП1 в своем цикле обслуживания. Величина КМВ может быть равна одному или двум байтам.

Во второй половине ЦО по сигналу на линии 72 выхода 25 блока 3 формирования циклов обслуживания запрещаются выходы порта В РФ4, то есть регистровый файл 4 переводится в режим записи промодифици- рованной управляющей информации, присутствующей на магистрали 21, так как выходы блока 5 разрешены во второй половине ЦО.

Для этого блок 3 формирования циклов вырабатывает на линии 1 строб записи для порта В РФ4,

Стробы записи/чтения порта В БП1, строб записи порта В РФ4 и сигнал записи модифицированной информации для блока 5 модификации порта В РФ вырабатываются только при наличии запроса на обмен данного канала, поступающего из регистрового буфера 2. При отсутствии запроса на обмен цикл данного канала превращается в холостой, управляющая информация В РФ4 не изменится и обслуживание данного канала произойдет в том его цикле, к началу которого будет запрос на обмен от регистрового буфера 2.

В режиме записи промодифицирован- ной информации В РФ4 модифицированный счетчик байтов сравнивается в блоке 5 модификации порта В с константой передачи данных при выполнении операций ввода и если счетчик байтов равен или больше КПДН, то на выход 12 устройства выдается запрос на обмен с ОП данного канала.

При выполнении операций вывода запрос выдается если счетчик байтов исчерпался.

Временная диаграмма обмена данными между регистровым буфером 2 и портом В БП1 для первого канала приведена на фиг.13.

Обмен данными между портом А БП1 и

ОП происходит следующим образом. Какой из четырех каналов будет обслуживаться оперативной памятью в ответ на запросы от каналов, поступающие на выход 12 устрой; ства, определяет ОП, присылая на вход 13 устройства код номера канала по линиям 1,2. Этот код номера канала адресует по порту А РФ4 управляющее слово данного канала и через блок 9 управления порта А БП зону БП1 данного канала.

Он присылает на вход 14 устройства сигнал начала связи по линии 129. По этому сигналу в блоке 11 связи с ОП устанавливается в единичное состояние триггер 124свя- зи с ОП, который определяет длительность связи с ОП данного канала.

Обмен данными с ОП происходит в три этапа.

Первый этап чтения управляющей ин- формации данного канала по порту А РФ 4 и размещения его в регистрах блока 8 модификации порта А РФ.

Сигналы чтения и разрешения выходов для порта А РФ4 вырабатываются соответ- ственно на линиях 2 и 1 выхода 31 блока 10 управления порта А РФ. Управляющая информация обслуживаемого канала выдается в магистраль 20 и в регистры 111, НО блока 8 модификации порта А РФ записываются константа передачи данных и номер байта порта А, После этого выходы порта А РФ4 запрещаются, т.е. отключается регистровый файл 4 от магистрали 20.

Второй этап - непосредственный синх- ронный обмен двойными словами с ОП.

Начало этого этапа определяет ОП, присылая по линии 130 входа 14 устройства сигнал начала передачи. По этому сигналу в блоке 11 связи с ОП устанавливается триг- rep 125 передачи.

На фоне триггера 125 Т ПДЧ разрешаются выходы регистров блока 8 модификации порта А и по магистрали 20 НБПА с выхода регистра 110 проадресуют через блок 9 управления порта А БП в зоне БП1 обслуживаемого канала номер строки, начиная с которой будет вестись обмен данными сОП.

Блок 9 вырабатывает также сигналы чте- ния и разрешения выходов при вводе или сигнал записи при выводе для порта А БП1 соответственно на линиях 2, 3, 1 выхода 30 для выдачи/приема двойного слова в/из системной магистрали 22.

Блок 8 модификации порта А РФ вырабатывает сигнал занесения модифицированных значений НБПА и КПДН соответственно в регистры 110, 111.

Модифицируются НБПА в сторону увеличения, а КПДН в сторону уменьшения на величину константы модификации порта А (КМА), поступающей на вход 15 устройства.

Величина КМА при обмене блоком равна восьми байтам. При обмене неполным двойным словом величина КМА равна константе передачи данных и определяется тремя младшими разрядами адреса данных ОП и величиной счетчика байтов CCW.

После модификации регистр 110 адресует следующую строку в зоне БП1 обслуживаемого канала, байты данных этого двойного слова по следующему сигналу чтения/записи порта А БП1 блока 9 выдадутся или примутся в/из системной магистрали 22.

Количество сигналов чтения/записи порта А БП1 и количество модификаций НБПА и КЦДН зависят от величины передаваемого блока и максимально равны четырем.

Эти сигналы вырабатываются до тех пор пока в результате модификации КПДН станет равна нулю. В этом случае устанавливается в единичное состояние триггер 127 равенства нулю константы передачи данных, по которому сбрасывается триггер 125 ТПДЧ и запрещаются выходы регистров блока 8 модификации в магистраль 20. Окончился второй этап.

Третий этап начинается опять с чтения управляющей информации данного канала по порту А РФ4 для модификации последнего значения счетчика байтов, которое могло измениться за время второго этапа при обмене с ПФУ по порту В БП1.

Блок 10 управления порта А РФ вырабатывает сигналы чтения и разрешения выходов для порта А РФ4 аналогично первому этапу. Величина счетчика байтов поступает по магистрали 20 в блок 8 модификации порта А, где модифицируется АЛУ 101 на величину КПДН и записывается в регистр 109. Выходы порта А РФ4 запрещаются, а выходы регистров блока 8 модификации порта А РФ разрешаются и модифицированные значения НБПА и СЧБ выдаются на магистраль 20 для записи по порту А РФ4 новой управляющей информации обслуживаемого канала.

Сигнал записи новой управляющей информации для порта А РФ4 вырабатывает блок 10 управления порта А РФ на линии 3

выхода 31. По этому же сигналу сбрасывается триггер 124 связи с ОП.

Общее оборудование порта А вновь готово для обмена данными с ОП любого из

каналов.

Блок 1 памяти (фиг.2) работает следующим образом.

Каждому каналу отведена своя зона в БП1, содержащая 8 строк по 8 байтов в

строке. Строки 0-7 образуют зону первого канала, строки 8-150 16-23, 24-31 соответственно зоны второго, третьего и четвертого каналов (фиг. 15).

Адрес зоны определяют два старших

разряда пятиразрядного адреса, а номер строки в зоне три младшие разряды адреса БП1.

При работе по порту В БП1 адрес подается на пятые входы адреса портов В всех

узлов 34 БП1 со входа 26 блока, адресуя зону обслуживаемого канала и номер строки в зоне.

Номер байта в строке начиная с которого будут записаны два байта данных с буферной магистрали 23 при вводе или прочитаны и выданы в буферную магистраль 23 при выходе определяют индивидуальные для каждого байта-узла 34 сигналы записи, чтения и разрешения выходов для портов В

БП1, поступающие на вход 28 блока.

Сигналы записи поступают по линиям 17-24, сигналы чтения по линиям 9-16, сигналы разрешения выходов по линиям 1-8 соответственно на шестые, седьмые и восьмые входы узлов 34.

При работе по порту А адрес поступает по линии 5 со входа 30 блока на первые входы адреса портов А узлов 34, адресуя зону и номер строки в зоне. Проадресованная строка будет прочитана при вводе по сигналу чтения порта А БП, поступающему по лини 2 со входа 30 блока на третьи входы записи портов А всех узлов 34. Прочитанная информация будет выдана в системную магистраль 22 по сигналу разрешения выходов порта А БП1, поступающему по линии 3 со входа 30 блока на четвертые входы узлов 34.

При выводе обменное слово с системной магистрали 22 будет записано в проад- ресованную стоку по сигналу записи порта А БП, поступающему по линии 2 со входа 30 блока на вторые входы узлов 34.

Регистровый буфер 2 (фиг.З) работает

следующим образом.

Регистровый буфер 2 содержит два однобайтовых регистра 57 и 58, выполненных на основе двунаправленных магистральных трансляторов (микросхема К1500ВА7), кото

рые позволяют хранить и передавать дан-ваться регистровый буфер 2 и БП1 в цикле

ные в обоих направлениях.обслуживания своего канала.

Направление передачи данных для обо-В цикле обслуживания своего канала на их регистров определяет код выполняемойвыходе элемента 35 И вырабатывается сиг- операции, который поступает по линии 3 со5 нал разрешения выходов регистров 57, 58 входа 18 устройства. Нулевое состояниедля выдачи содержащихся в них байтов дан- этого сигнала задает операцию ввода,аеди-ных в буферную магистраль 23. После запи- ничное - вывода.си этих байтов в БП1 по синхросигналу СИ4

При выполнении операций ввода на-134 с выхода элемента 39И сбрасываются

правление задано в сторону выдачи байтов10 триггеры 55, 56, сообщая ПФУ через выход

данных в буферную магистраль 23, а при19 о готовности принять следующие байты

выполнении операций вывода в обрат-данных.

ную сторону для приема данных в реги-При выполнении операций вывода по

стры 57, 58.нулевому состоянию триггеров 55, 56 на выПри выполнении операций ввода байты15 ходе элемента 60 И-ИЛИ формируется заданных от ПФУ первый и последующие не-прос на обмен данными с БП1 для записи четные сопровождаются запросами от ПФУбайтов данных в регистровый буфер 2 на прием нечетного байта, поступающимипрочитанных из зоны БП1 данного кана- по линии 1 со входа 18 устройства, а второйла.

и последующие четные сопровождаются за-20 Направление для регистров 57, 58 задапросами от ПФУ на прием четного байта,но в сторону приема информации из буферпоступающими по линии 2 со входа 18 уст-ной магистрали 23.

ройства. .В цикле обслуживания своего канала

В ответ на эти запросы нечетные байтыбайты данных с буферной магистрали 23

с двунаправленной магистрали 17 будут за-25 запишутся в регистры 57, 58 по синхросигписываться в первый регистр 57, а четныеналу СИ4 134с выхода элементов41И и43И.

байты буду записываться во второй регистрЕсли свободны оба регистра 57,58 (оба триг58по синхросигналу СИ1 131 с выходовгера 55, 56 сброшены) запишутся два байта, элементов 42И, 44И.один из регистров свободен, то запишется

Каждому из регистров 57, 58 соответст-30 один байт.

вует свой триггер 55 и 56 фиксирования ин-Триггеры 55, 56 установятся в единичформации.ное состояние по синхросигналу СИ4 134 с

Единичное состояние триггеров 55, 56выхода элемента 37И, сообщая ПФУ через

указывает на наличие информации (байтавыход 19 о готовности выдать байт данных,

данных) в соответствующем регистре 57, 58.35 ПФУ присылает запрос на прием нечетПри занесении байта данных в регистрыных байтов по линии 4, четных - по линии 5

57, 58 одновременно устанавливаются всо входа 18 устройства,

единичное состояние и соответствующиеВ ответ на этот запрос разрешается выим триггеры 55, 56 фиксируя наличие байтаход соответствующего регистра для выдачи

данных в регистрах 57, 58.40 байта данных в магистраль 17.

Прямые выходы триггеров 55, 56 управ-Для регистра 57 разрешение выхода

ляют схемой И-ИЛИ 60, узлом сложения поформирует схема 45И, и для регистра 58

модулю два 59 и поступают на выход 19схема 46И.

устройства.Сбрасывается в соответствующий тригНа выходе схемы И-ИЛИ 60 формиру-45 rep 55 или 56 по синхросигналу СИ1 131 с

ется запрос на обмен данными с БП1 длявыходов элементов 38И в 40И.

записи содержащихся в регистровом бу-Байты поочередно выдаются в ПФУ, а

фере 2 байтов данных в зону БП1 данногопо сброшенным триггерам 55, 56 вновь форканала.мируется запрос на обмен данными с БП 1

На выходе узла сложения по модулю два50 для приема следующих байтов.

59формируется константа модификацииБлок 3 формирования циклов обслужи- порта В (КМВ), равная единице, что соответ-вания (фиг.4) работает следующим обра- ствует состоянию единицы на прямом выхо-зом.

де узла сложения по модулю два 59, илиДля формирования циклов обслужидвум, если оба триггера 55, 56 установлены55 вания четырех каналов используется

в одинаковое состояние, что соответствуетдвоичный трехразрядный счетчик 61 идвухсостоянию нуль на прямом выходе узла ело-входовой дешифратор циклов 65.

жения по модулю два 59. КМВ указываетСчетчик 61 срабатывает от каждого синколичество байтов, которым будут обмени-хроимпульса СИ1 131.

Два старших разряда счетчика 61 управляют дешифратором 65 на выходе которого и вырабатываются четыре последовательности состояний старших разрядов счетчика 61. Эти состояния 00, 01, 10, 11 и являются циклами обслуживания Ц01-Ц04 соответственно 1-4 (см. диаграмму на фиг. 13) каналов.

Старшие разряды счетчика 61 управляют также адресными входами четырехвхо- довых мультиплексоров 66, 67

На 0-3 входы мультиплексора 66 поступают соответственно запросы на обмен данными с БП1 от регистровых буферов 2 каналов 1-4.

На входы мультиплексора 67 поступают коды выполняемой операции также из регистровых буферов 2.

На выходы мультиплексоров 66, 67 будут выдаваться запросы на обмен данными с БП1 и коды выполянемой операции в соответствии с циклами обслуживания каналов.

Эти же разряды, поступая по линиям 73, 74 на выход 25 блока управляют адресами зон БП1, РФ4 по портам В.

Младший разряд счетчика 61, который перебрасывается от каждого синхросигнала СИ1 131 в противоположное состояние, делит цикл обслуживания пополам.

В первой половине каждого цикла (нулевое состояние младшего разряда счетчика 61) на выходе элемента 63И по синхросигналу СИ1 131 вырабатывается строб чтения порта В РФ4, а на выходе элемента 64 НЕ сигнал разрешения выхо- дов порта В РФ4(нулевой сигнал разрешает выходы, а единичный запрещает).

Во второй половине цикла (единичное состояние младшего счетчика 61) на выходе элемента 62И вырабатывается по синхро- сигналу СИ2 132 сигнал записи для порта В РФ4 при наличии запроса на обмен данными с БП1 обслуживаемого канала, поступающего с выхода мультиплексора 66 на вход элемента 62 И.

Регистровый файл 4 (фиг.5) работает следующим образом.

Каждому каналу в РФ4 отведена своя зона из восьми строк по четыре байте в каждой. Строки 0-7, 8-150 16-23 и 24-31 отведены соответственно для каналов 1-4 (фиг. 15).

В каждой зоне для передачи данных используется управляющая информация первой из восьми строк.

Для адресации зон РФ4 по порту В два старшие разряда пятиразрядного адреса порта В РФ4 управляются двумя старшими разрядами 73, 74 счетчика 61 блока 3 формирования циклов, которые поступают со входа 25 на пятые входы адреса порта В узлов 34.

Для адресации зон РФ4 по порту А два старшие разряда пятиразрядного адреса порта А РФ4 управляются двухразрядным номером канала, поступающим со входа 13 на первые входы адреса портов А узлов 34.

Три младшие разряды адреса по обоим портам А и В не используются для адресации и поэтому при адресации номера зоны автоматически адресуется одна строка в зоне, содержащая управляющую информацию для передачи данных.

Стробы записи, чтения и разрешения выходов для порта В РФ4 поступают соответственно на шестые, седьмые и восьмые входы второго, третьего и четвертого узлов 34 по линиям 1, 2, 3 входа 25 блока.

Первый узел 34, содержащий Н БПА, при работе по порту В РФ4 не используется.

Информация принимается и выдается по порту В РФ4 из/в в магистраль 21.

Для порта А РФ4 стробы записи, чтения и разрешения выходов поступают соответственно на вторые, третьи и четвертые входы первого, второго и третьего узлов 34 по линиям 3, 2, 1 входа 31 блока.

Четвертый узел 34, содержащий НБПВ при работе по порту А РФ4 не используется.

Информация принимается и выдается по порту А РФ4 из/в магистраль 20.

Блок 5 модификации порта В РФ (фиг.6) работает следующим образом.

В первой половине каждого цикла обслуживания управляющая информация, присутствующая на магистрали 21, подается на входы второго 76 и первого 77 АЛУ и на вход регистра 81. На вход регистра 81 подается КПДН, на вход второго 76 АЛУ подается НБПВ, а на вход первого 77 АЛУ подается СЧБ. На вторые входы обеих АЛУ поступает КМ В обслуживаемого канала с выхода мультиплексора 75, т.к. адресные разряды мультиплексора управляются старшими разрядами 73, 74 счетчика 61 блока 3 формирования циклов.

Второе 76 АЛУ работает всегда в режиме сложения, а для первого 77 АЛУ режим работы задает код операции обслуживаемого канала, поступающий по линии 5 со входа 25 блока. Нулевое состояние, соответствующее операции ввода задает режим сложения, а единичное при операции вывода задает режим вычитания.

Промодифицированная информация с выходов АЛУ 76,77 записывается соответственно в регистры 82, 83 по синхросигналу

СИЗ 133 с выхода элемента 78И при наличии запроса на обмен данными с БП1 регистрового буфера 2 обслуживаемого канала, поступающего по линии 4 входа 25 блока и в первой половине цикла обслуживания - нулевое значение младшего разряда счетчика 61, поступающего по линии 72 с входа 25 блока. По этому же сигналу с выхода элемента 78И в регистр 81 занесется без изменения значение КПДН.

Регистры 81, 82, 83 выполнены на основе двунаправленных магистральных трансляторов, позволяющих хранить и передавать данные в обоих направлениях.

Направление дли этих регистров задано постоянно в сторону выдачи данных в двунаправленую магистраль 21 (А ).

Выходы регистров 81, 82, 83 отключены от магистрали 21 в первой половине цикла обслуживания, а во второй половине цикла выходы разрешены для выдачи в магистраль 21 промодифицированных значений НБПВ и СЧБ. Для этого входы DE регистров управляются сигналом 72 со входа 25 блока.

Значение КПДН с выхода регистра 81 во второй половине цикла обслуживания сравнивается при вводе с модифицированным счетчиком байтов схемой 79 сравнения, Если СЧБ больше или равен КПДН на выходе элемента 84И вырабатывается сигнал установки в едининчое состояние одного из четырех разрядов регистра 86 запросов на обмен с ОП в соответствии с циклами обслуживания.

При выводе запрос на обмен с ОП данного канала вырабатывается, если в результате модификации СЧБ сигнал равен нулю.

В этом случае устанавливается в единичное состояние соответствующий данному каналу разряд регистра 87.

Блок 6 адресации порта В БП (фиг.7) работает следующим образом.

Для адресации четырех зон по порту В БП1 используются два старшие разряда счетчика 61 блока 4 формирования циклов обслуживания, которые поступают по линиям 73, 74 со входа 25 блока и по линиям 3, 4 выдаются на выход 26 блока как два старших разряда адреса для узлов 34 с первого по восьмой - 1-8 (4), 1-8 (5).

Для даресации восьми строк в зоне используются три старшие разряда НБПВ из регистрового файла 4, поступающие по линиям 4, 5, 6 со входа 21 блока, которые выдаются по линии 2 на выход 26 блока как три младших разряда адреса для узлов 34 со второго по восьмой 2-8 (1-3).

Для первого узла 34 три младших разряда адреса 1(1-3) выдаются с выхода мультиплексора 92 и могут адресовать текущую строку по трем старшим разрядам НБПВ как и для остальных узлов 34 или следующую строку.

Необходимость проадресовать первый узел 34 БП1 следущей строкой возникает, когда тербуется обменяться с регистровым буфером 2 какого-либо канала двумя байтами, причем первый байт является последовательным в текущей строке, а второй байт первым в следующей строке. При этом три младшие разряда НБПВ раны семи.

Эта ситуация возникает из-за возможности обмена с регистровыми буферами 2 одним или двумя байтами.

Номер текущей строки подается на ну- левой вход мультиплексора 92, номер следущей строки на первый вход.

Выбором направления мультиплексора 92 управляет сигнал со входа 27 блока, который вырабатывается при равенстве трех младших разрядов НПБВ семи.

При отсутствии сигнала на входе 27 выбирается нулевое направление и первый узел 34 БП1 адресуется текущей строкой.

При наличии сигнала на входе 27 на выход мультиплексора 92 выдается адрес следующей строки.

Номер следующей строки или строки на единицу больше текущей формирует комбинационная схема, состоящая из элементов 88,90 И и двух схем сложения по модул ю два 89,91.

Комбинационная схема построена по формулам согласно таблицы истинности

где х, у, z - три младшие разряда НБПВ;

x1, - соответствующие три разряда увеличенного на единицу значения разрядов х, у, 2.

Из таблицы видно, что значение младшего разряда z1 равно инверсному значению разряда z, т.е. z z.

Следующие разряды у их определяются по формулам

у xyz + xyz + xyz + xyz yz (x + x) + + yz (x + x) у фг;

x xyz + xyz + xyz + xyz xyz + xyz + + xyz + xyz + xyz xz (y + y) + xy (z + z) + + xyz x (z + y) + xyz xyz + xyz x фуг

Блок 7 управления порта В БП (фиг.8) работает следующим образом.

Сигналы записи, чтения и разрешения выходов для порта В каждого из восьми узлов 34 ПБ1 формируются на выходах соответствующих селекторов 100, 99, 98. В какой из узлов 34 БП1 выдать сигнал записи или чтения и разрешения выходов оп- редлеяет дешифратор 93 по трем младшим разрядам НБПВ, поступающим на вход дешифратора 93 из РФ4. По каждому состоянию дешифратора 93 вырабатывается на выходе линейки 96 ИЛИ пара сигналов, определяющих два узла 34; адресованный по НБПВ и следующий для которых будут выданы сигналы управления для записи или чтения двух байтов в зависимости от кода выполняемой операции и при наличии запроса на обмен данными с регистровым буфером 2 обслуживаемого канала.

Запрос на обмен и код выполняемой операции поступают по линиям 4, 5, со входа 25 блока.

При выполнении операций ввода по синхроимпульсу СИ2 132 со входа 16 блока через элемент 97 И срабатывает селектор 100 и на выход 28 блока будет выдана пара сигналов записи по линиям 17-24.

При выполнении операций вывода по сигналу с выхода элемента 94 И сработает селектор 98, выдавая на выход 28 блока пару сигналов разрешения выходов по линиям 1-8, а по синхроимпульсу СИ2 132 через элемент 95 И сработает селектор 99, выдавая на выход 28 по линиям 9-16 пару сигналов чтения.

Последний выход дешифратора 93, соответствующий состоянию семь выдается на выход 27 блока для управления адресом строки по порту В первого элемента 34 БП1.

Блок 8 модификации порта А РФ (фиг.9) работает следующим образом.

Для хранения исходных и модифицированных значений СЧБ, НБПА, КПДН обслуживаемого канала при обмене данными с ОП используются соответственно регистры 109, 110, 111.

Для модификации значений СЧБ, НБПА, КПДН используются АЛУ 101, 102, 103.

Регистры 109, 110, 111 реализованы на основе двунаправленых магистральных

трасляторов с возможностью отключения выходов, которые позволяют хранить и передавать данные в обоих направоениях.

Направление для регистров жестко задано в сторону выдачи даных в магист0 раль 20.

Выходы регистров запрещены на первом этапе обмена данными с ОП и исходные значения КБПА и КПДН, присутстующие на магистрали 20, заносятся соответственно

5 через нулевые входы мультиплексоров 106 и 107 в регистры 110, 111 по синхроимпульсу СИЗ 133 с выхода первой схемы элемента 104И-ИЛИ.

Первый этап обмена данными с ОП ха0 рактеризуется сигналами на линиях 1, 4 входа 33 блока и соответствующих установленному триггеру 126 ТЦПА и сброшенному триггеру 127 ТКПДНО блока 11 связи с ОП. Во время второго этапа собственно об5 мена данными с ОП по сигналу на линии 3 входа 33 блока (это установлен триггер 125 ТПДЧ блока 11 связи с ОП) выбирается первое направление мультиплексоров 106, 107, выходы регистров разрешены и содержаща0 яся в них информация по магистрали 20 подается на первые входы соответствующих АЛУ.

На вторые входы АЛУ 102, 103 подается КМА со входа 15 блока. Модифицированные

5 на величину КМА значения НБПА и КПДН через первые входы мультиплексоров 106, 107 поступают на входы регистров 110, 111 и по синхроимпульсу СИЗ 133 с выхода второй схемы И элемента 104 И-ИЛИ занесутся

0 в регистры 110, 111. Новые значения НБПА и КПДН поступят по магистрали 20 на входы АЛУ 102, 103 для повторной модификации и записи по следующему синхросигналу СИЗ 133.

5Режимами работы АЛУ 102, 103 управляет триггер 124 ТСОП блока 11 связи с ОП, прямой выход которого поступает по линии 2 со входа 33 блока.

Установленный в единицу триггер 124

0 ТСОП задает для АЛУ 102 режим сложения, а для АЛУ 103 режим вычитания.

Модификация и запись результатов в регистры 110, 111 будет происходить до тех пор, пока на выходе элемента 112 И не вы5 работается сигнал равенства нулю константы передачи данных, поступающий в блок 11 связи с ОП, после этого сбрасывается сигнал на линии 3 входа 33 блока, прекращая запись результатов в регистры 110 111 и запрещая выходы всех регистров.

Во время третьего этапа обмена данны-циклов, т.е. в первой половине ЦО - это

ми с ОП начинают работать АЛУ 101 и ре-режим чтения порта А РФ4.

гистр 109. На первый вход АЛУ 101 подаетсяСигнал с прямого выхода триггера 124

величина СЧБ, а на второй вход величинаТЦПА приходит по линии 1 входа 33 блока,

КПДН по магистрали 20 с выхода РФ4. По5 а младший разряд счетчика 61 поступает по

сигналу, поступающему со входа 32, моди-линии 72 входа 25 блока,

фицированное значение СЧБ запишется вДля третьего этапа в блоке вырабатыварегистр 109. Режим работы АЛУ 101 задаетются сигнал занесения модифицированного

код операции обслуживаемого канала, по-значения СЧБ в-регистр 109 блока 8 модиступающий по линии 4 со входа 30 блока.10 фикации порта А на выходе элемента 123 И

Единичное значение этого сигнала (one-и строб записи для порта А РФ4 по синхрорация вывода) задает режим сложения, аимпульсу СИ2 132 на выходе элемента 119И.

нулевое (операция ввода) режим вычитания.Сигнал занесения вырабатывается в

В конце третьего этапа при установлен-первой половине ЦО в режиме чтения порта

ном триггере 126 ТЦПА (линия 1 входа 33) во15 А РФ4, а строб записи во второй половине

второй половине цикла обслуживания (ли-ЦО в режиме записи для порта А РФ4.

ния 72 входа 25) на выходе элемента 105 ИОба эти сигнала выдаются не в цикле

вырабатывается сигнал разрешения выхо-обслуживания данного канала для предотвдов регистров для выдачи модифицирован-ращения одновременной модификации СЧБ

ных значений СЧБ, НБПА в магистраль 20,20 при обслуживании канала по обоим портам

Блок 9 управления порта А БП (фиг.Ю)А и В БП1 и для предотвращения одновреработает следующим образом.менной записи по одному и тому же адресу

При выполнении второго этапа собст-по портам А и В РФ4.

венно обмена данными с ОП на вход 33Это условие отслеживает мультиплекблока поступает сигнал с прямого выхода25 сор 117. На его входы поступают Ц01-Ц04

триггера 125ТПДЧ из блока 11 связи с ОП.по линиям 68-71 входа 25, а выбором наПо этому сигналу начинают выдаватьсяправления управляют два разряда номера

по синхроимпульсу СИ2 132, поступающемуканала, которые подаются по линиям 1, 2 со

на вход 16 блока, стробы записи с выходавхода 13 устройства.

элемента 113 И или чтения с выхода элемен-30 На выход мультиплексора 117 будет выта 114 И в зависимости от кода выполняв-даваться только ЦО обслуживаемого канала,

мой операции, а на выходе элемента 115 ИСхема 120 И формирует условия разревырабатывается сигнал разрешения выхо-шения выдачи сигнала занесения и строба

дов для порта АБП1.записи при условии отсутствия ЦОобслужиКоды операций от четырех каналов по-35 ваемого канала и наличию установленного в

ступают на входы мультиплексора 116.единицу триггера 126 ТЦПА.

Выбором направления мультиплексораСтроб записи для порта А РФ4 форми116 управляют два разряда номера канала,руется также по сигналу на линии 3 входа 13

поступающие со входа 13 устройства.устройства для предварительной записи исНа выходе мультиплексора 116 всегда40 ходной управляющей информации перед

присутствует код операции обслуживаемогоначалом обмена данными.

канала по обмену данными с ОП.Блок 11 связи с ОП (фиг.12) работает

Эти же два разряда номера канала вме-следующим образом.

сте стремя старшими разрядами НБПА, по-Блок вырабатывает четыре сигнала,

ступающими по линии 2 из магистрали 2045 характеризующих процесс обмена данобразуют пятиразрядный адрес для порта Аными с ОП.

БП1, который по линии 5 выдается на выходЭти четыре сигнала вырабатывают триг30 блока.геры 124 ТСОП, 125 ТПДЧ, 126 ТЦПА и 127

Блок 10 управления порта А РФ(фиг.11)ТКПДНО.

работает следующим образом.50 Триггер 124 ТСОП установлен в единичДля первого и третьего этапов обменаное состояние на время связи с ОП при

данными с ОП блок вырабатывает для портаобмене данными с одним каналом.

А РФ4 стробы чтения по синхроимпульсуУстанавливается тригегр 124 ТСОП по

СИ1 131 на выходе элемента 119 И сигналысинхроимпульсу СИ2 132 в ответ на сигнал

разрешения выходов на выходе элемента55 начала связи с ОП на линии 129 входа 14

121И - при установленном в единичное со-блока. Сбрасывается этот триггер в конце

стояние триггера 128 ТЦПА блока 11 связиобслуживания данного канала оперативной

с ОП и при нулевом состоянии младшегопамятью в момент записи модифицированразряда счетчика 61 блока 4 формированияной в результате обмена управляющей информации в РФ4 по стробу записи порта А РФ4, поступающему по линии 3 со входа 31 блока.

Триггеры 126 ТЦПА и 127 ТКПДНО характеризуют первый и третий этапы при обмене данными с ОП.

Триггер 125 ТПДЧ определяет второй этап собственно обмена данными с ОП.

Для первого этапа ТЦПА 1, ТКПДНО О, а для третьего этапа ТЦПА 1, ТКПДНО 1, т.е. триггер 127 ТКПДНО определяет время до и после второго этапа, т.к. КПДН обнуляется в конце второго этапа в результате обмена данными с ОП, вызывая установку в единичное состояние триггера 127 ТКПДНО.

Триггер 126 ТЦПА устанавливается в единичное состояние по синхроимпульсу СИ4 134 при установленном триггере 124 ТСОП в первой половине ЦО (сигнал на линии 72 входа 25 блока).

Для предотвращения многократной установки триггера 126 ТЦПА при установлен- ном триггере 124 ТСОП предназначен триггер 128 блокировки ТБЛК,

Этот триггер устанавливается в единичное состояние на первом этапе при ТЦПА 1 и ТКПДНО 0 по синхроимпульсу СИ2 132 вызывая сброс триггера 126 ТЦПА и запрещая его повторную установку.

Триггер 128 ТБЛК сбрасывается при установке триггера 127 ТКПДНО, разрешая повторную установку ТЦПА для третьего этапа.

Если при первой установке триггер 126 ТЦПА продолжает оставаться установленным только до следующего синхроимпульса СИ4 134 разрешая за это время формирование только строб чтения для порта А РФ4 (см. фиг.4), то при повторной установке кроме строба чтения вырабатывается еще строб записи для порта А РФ4, по которому сбрасывается триггер 124 ТСОП, вызывая в свою очередь сброс триггеров 126 ТЦПА и 127 ТКПДНО.

Триггер 128 ТБЛК повторно не устанавливается, т.е. на третьем этапе установлен триггер 127 ТКПДНО.

Триггер 125 ТПДЧ, характеризующий второй этап собственно обмена данными с ОП, устанавливается по синхроимпульсу СИ1 131 при наличии сигнала начала передачи данных от ОП на линии 130 входа 14 блока, а сбрасывается после установки триггера 127 ТКПДНО (см. временную диаграмму работы блока на фиг. 14).

Формула изобретения

1. Устройство для обмена данными междуоперативной памятью и периферийными

устройствами, содержащее блок памяти, входы-выходы данных порта А которого соединены с внешней двунаправленной системной магистралью устройства, о т л и ч аю щ е е с я тем, что, с целью расширения области применения, упрощения структуры устройства, уменьшения затрат оборудования, в него введены регистровые буферы, блок формирования циклов обслуживания,

регистровый файл, блок модификации порта В регистрового файла, блок адресации порта В блока памяти, блок управления порта В блока памяти, блок модификации порта А регистрового файла, блок управления порта

А блока памяти, блок управления порта А регистрового файла, блок связи с оперативной памятью, первый вход которого соединен с входом начала связи с оперативной памятью устройства, группа выходов запросов обращения к оперативной памяти устройства соединена с выходом блока модификации порта В регистрового файла, группа входов номера канала устройства соединена с первыми входами блоков управления порта А блока памяти и регистрового файла, вход-выход данных порта А которого соединен с внешней двунаправленной магистралью устройства, которая соединена с вторым входом блока управления порта А

блока памяти и входом-выходом блока модификации порта А регистрового файла, первый вход которого соединен с группой входов константы модификации порта устройства, а второй вход - с группой входов

синхроимпульсов устройства, которая соединена с первыми входами блока формирования циклов обслуживания, блока модификации порта В регистрового файла, блока управления порта В блока памяти,

третьим входом блока управления порта А блока памяти, вторыми входами блока управления порта А регистрового файла, блока связи с оперативной памятью и первыми входами регистровых буферов, первые входы-выходы данных которых соединены соответственно с входами-выходами устройства для подключения периферийных устройств, вторые входы регистровых буферов соединены с группой входов управления обменом с периферийными устройствами, а группы выходов управления обменом с периферийными устройствами регистровых буферов соединены с группой входов управления обменом с периферийными устройствами, а группы выходов управления обменом с периферийными устройствами регистровых буферов соединены с первыми выходами регистровых буферов, вторые входы-выходы данных которых через внутреннюю двунаправленную буферную магистраль соединены с входами-выходами данных порта В блока памяти, первый вход которого соединен с группой выходов блока управления портом А блока памяти и третьим входом блока модификации порта А регистрового файла, выход равенства нулю константы передачи данных которого соединен с третьим входом блока связи с оперативной памятью, группа выходов управления которого соеди- нена с четвертым входом блока модификации порта А регистрового файла, третьими входами блока управления порта А блока памяти и блока управления порта А регистрового файпа, выход модификации счетчика байтов Kowporo соединен с пятым входом блока модификации порта А регистрового файла, группа выходов блока управления портом А регистрового файла соединена с четвертым входом блока связи с оператив- ной памятью и вторым входом регистрового файла, двунаправленная магистраль данных порта В которого соединена с входами- выходами данных блока модификации порта В регистрового файла, первым вхо- дом блока адресации порта В блока памяти и вторым входом блока управления порта В блока памяти, группа выходов управления которого соединена с вторым входом блока памяти, третий вход которого соединен с группой выходов блока адресации порта В блока памяти, второй вход которого соединен с выходом блока управления порта В блока памяти, а третий вход - с группой выходов блока управления циклов обслужи- вания, которая соединена с третьим входом регистрового файла, вторым входом блока модификации порта В регистрового файла, третьим входом блока управления порта В блока памяти, шестым входом блока моди- фикации порта А регистрового файла, четвертым входом блока управления порта А регистрового файла, пятым входом блока связи с оперативной памятью, третьими входами регистровых буферов, группа выхо- дов которых соединена соответственно с вторым, третьим, четвертым и пятым входами блока формирования циклов обслуживания, с третьим, четвертым, пятым и шестым входам блока модификации порта В регист- рового файла, с пятым, шестым, седьмым и восьмым входами блока управления порта А блока памяти.

2. Устройство поп.1,отличающее- с я тем, что блок памяти содержит восемь двухадресных двухпортовых узлов памяти, первые, вторые, третьи и четвертые входы управления которых соединены с первым входом блока, третий вход блока соединен

с пятыми входами управления восьми узлов памяти, а второй вход блока соединен с шестыми, седьмыми и восьмыми входами управления восьми узлов памяти, входы-выходы данных портов В являются одноимен- ными входами-выходами блока, а входы-выходы данных портов А образуют вход-выход данных порта А блока.

3. Устройство по п.1,отличающееся тем, что регистровый буфер содержит двенадцать элементов И, восемь элементов ИЛИ, первый и второй триггеры, первый и второй регистры, узел сложения по модулю два, элемент И-ИЛИ, выход которого и прямой и инверсный выходы узла сложения по модулю два, первые входы первого и второго регистров, первый и второй инверсные и первый и второй прямые входы элемента И-ИЛИ, один разряд второго входа блока образуют группу выходов блока, первые входы с первого по девятый элементов И, инверсные входы второго, четвертого, десятого и одиннадцатого элементов И, вторые входы пятого, шестого, восьмого и девятого элементов И поключены к второму входу буфера, с третьими входами четвертого, шестого, восьмого и девятого элементов И и с первым выходом блока, выход управления обменом блока соединен с первым и вторым входами узла сложения по модулю два, с третьим и четвертым прямым входами и с третьим, четвертым инверсными входами элемента И-ИЛИ, соединенными с выходами первого и второго триггеров и с инверсными входами первого и третьего элементов И, выходы которых соединены соответственно с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с вторыми входами первого и второго регистров, второй вход первого элемента ИЛИ соединен с выходом второго элемента И и с первым входом третьего элемента ИЛИ, второй вход второго элемента ИЛИ соединен с выходом четвертого элемента И и с первым входом четвертого элемента ИЛИ, выходы третьего и четвертого элементов ИЛИ соединены соответственно с первыми входами первого и второго триггеров, вторые входы которых соединены соответственно с выходами пятого и шестого элементов ИЛИ, первые входы которых соединены соответственно с выходами восьмого и девятого элементов И, а вторые входы соединены с выходом одиннадцатого элемента И, первый вход которого соединен с выходом двенадцатого элемента И и с вторыми входами первого, третьего и седьмого элементов И, выход седьмого элемента И соединен с вторыми входами третьего и

четвертого элементов ИЛИ, а третий вход совместно с третьими входами с первого по чтвертый, восьмого, девятого и одиннадцатого элементов И образуют первый вход блока, третий вход которого соединен с инверсным и прямым входами двенадцатого элемента И и с вторым входом десятого элемента И, выход которого соединен с первыми входами седьмого и восьмого элементов ИЛИ, вторые входы которых соединены соответственно с выходами пятого и шестого элементов И, а выходы соединены соответственно с инверсными входами первого и второго регистров, первые входы-выходы которых соединены с первым входом-выходом буфера, а вторые входы-выходы соединены с вторым входом-выходом буфера.

4.Устройство поп.1,отличающее- с я тем, что блок формирования циклов обслуживания содержит счетчик, два элемента И, элемент НЕ, дешифратор и два мультиплексора, причем выходы первого и второго мультиплексоров, выходы первого и второго элементов И, выходы дешифратора, выход элемента НЕ, первый, второй и третий выходы счетчика образуют группу выходов блока, второй, третий выходы счетчика соединены с адресными входами первого и второго мультиплексоров и входами дешифратора, первый выход счетчика соединен с первыми входами первого и второго элементов И и входом элемента НЕ, первый вход блока соединен с вторыми входами первого и второго элементов И и с входом счетчика, а второй, третий, четвертый и пятый входы блока соединены соответственно с объединенными одноименными входами первого и второго мультиплексоров.

5.Устройство по п. 1,отличающее с я тем, что регистровый файл содержит четыре двухадресных двухпортовых узла памяти, причем входы-выходы портов А первого, второго и третьего узлов памяти образуют двунаправленую магистраль порта А регистрового файла, входы-выходы портов В второго, третьего и четвертого узлов памяти образуют двунаправленную магистраль порта В регистрового файла, а первый вход регистрового файла соединен с первыми входами первого, второго и третьего узлов памяти, вторые, третьи и четвертые входы которых соединены с вторым входом регистрового файла, третий вход которого соединен с пятыми, шестыми, седьмыми и восьмыми входами второго, третьего и четвертого узлов памяти.

6.Устройство поп.1,отличающее- с я тем, что блок модификации порта В регистрового файла содержит мультиплексор, два арифметико-логических узла, четыре элемента И, схему сравнения, пять регистров, причем выходы первого и второго регистров соединены с выходом блока, а их

первые входы, адресные входы мультиплексора, управляющий вход первого арифмети- ко-логического узла, соединенный с инверсным входом первого и первым входом второго элементов И, инверсные входы

с первого по третий регистров, соединенные со вторыми входами первого и второго инверсным входом третьего элементов И, второй вход третьего элемента И, соединенный с третьими входами первого и второго

элементов И, образуют второй вход блока, первый вход которого соединен с третьим входом третьего элемента И, а третий, четвертый, пятый и шестой входы блока соединены соответственно с первым, вторым,

третьим и четвертым входами данных мультиплексора, выход которого соединен с вторыми и первыми входами данных первого и второго арифметико-логических узлов, выходы которых соединены соответственно с

входами данных четвертого и пятого регистров, синхровходы которых соединены с выходом третьего элемента И, с третьим синхровходом третьего регистра, вход и выход данных которого соединен с входами-выходами данных блока, с группами выходов четвертого и пятого регистров, с вторыми входами данных первого и второго арифметико- логических узлов, с первым, вторым входами схемы сравнения и с инверсными входами

четвертого элемента И, выходы схемы сравнения и второго элемента И соединены соответственно с четвертыми входами первого и второго элементов И, выходы которых соединены соответствен нос синхровходами четвертого и пятого регистров.

7. Устройство по п.1,отличающееся тем, что блок адресации порта В блока памяти содержит элемент НЕ, два узла сложения по модулю два, элемент И и