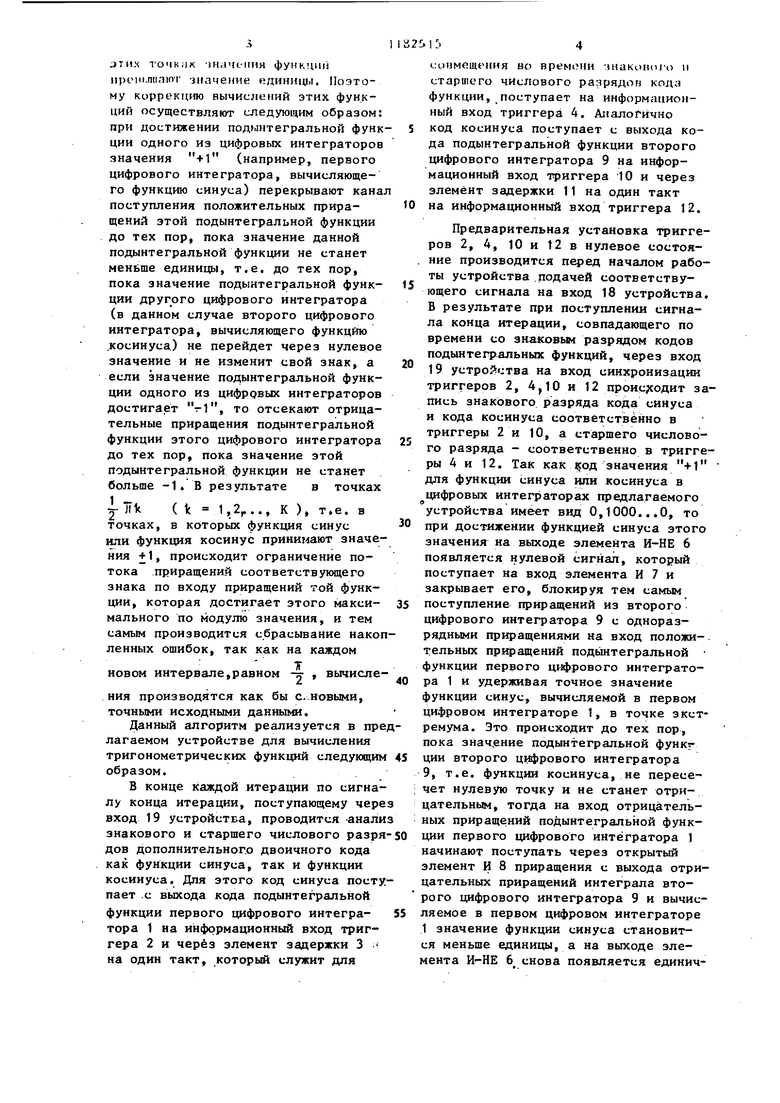

Изобретение относится к вычис.штельной технике и предназначено для использования а спецнализирова ных вычислительных устройствах и машинах, в особенности в навигацио ных системах и системах автоматического регулирования для реализаци синусно-косйнусных зависимостей. Целью изобретения является повышение точности. Блок-схема устройства представл на на чертеже. Устройство содержит цифровой интегратор 1, триггер 2, элемент задержки 3, триггер 4, элементы И5 и 6, элементы И 7 и 8, цифровой интегратор 9, триггер 10, элемент задержки 11, триггер 12, элементы К-НЕ 13 и 14, элементы И 15 и 16, входы устройства 17-19, выходы устройства 20 и 21, Интеграторы 1 и 9 представляют собой цифровые интеграторы с /одноразрядными прира щениями. Устройство для вычисления триго нометрических функций реализует синусно-косинусные зависимости у « sinx и у COSX на основе системы уравнений Шеннона следующе го вида: У2 dx ; dy ; . где X - значение аргумента. Устройство для вычисления тригонометрических функций работает следующим образом. Приращения аргумента dx поступают с входа 17 устройства на такто вые входы интеграторов 1 и 9 и воз буждают их работу. В конце каждой итерации на выходах положительных и отрицательных приращений интегра ла цифровых интеграторов 1 и 9 начинают формироваться .одноразрядные приращения интеграла: dy на выход первого интегратора 1, реализующег уравнение dy « , и dy на выходе второго цифрового интегратора 9, реализующего уравнение dX| y2dx. При этом одноразрядные приращения интегралов dy и dy представляются в троичной системе кодирования, т.е. принимают значения +1, О и -1 и поэтому пе редаются по двум каналам (положительному и отрицательному) в виде постоянных сигналов,соответствующи +1 или -1,причем одноразрядные приращения интеграла dy поступают : выходии положительных и отрицательных приращений интеграла второго цифрового интегратора 9 через элементы И 7 и 8, служащие для организации коррекции результатов вычисления и управляемые состоянием триггеров 2 и 4, на входы приращений подынтегральной функции первого цифрового интегратора 1, а одноразрядные приращения интеграла dy. с выходов положительных и отрицатШьных приращений интеграла пер§Ьго цифрового интегратора 1 поступают через элементы И 15 и 16, также служащие для организации коррекции результатов вычислений и управляемые состоянием триггеров 10 и 12,на входы прираще НИИ подынтегральной функции второго цифрового интегратора 9. Дпя исключения накопления ошибок в цифровых интеграторах определим алгоритм коррекции из анализа погрешности вычислений синусно-косинусиых зависимостей на большом интервале решения. Аналитическая зависимость погрешности вычисления функ1;ии синуса и косинуса для схемы реализации синусно-косйнусных зависимостей с помощью системы уравнений Шеннона на двух цифровых интеграторах с одноразрядными приращениями имеет следующий вид: 1 xh s inx sinx 2 cosx 2 где h - шаг интегрирования; g . -погрешность функции синус;- погрешность функции косинус. Анализируя выражения (1) и (2), можно заметить, что погрешность возрастает с ростом значения переменной и накопление ее происходит по закону синуса при воспроизве енин функции синуса и по закону косинуса при воспроизведении функции косинуса. Так как максимальная по модулю погрешность вычисления этих функций образуется тогда, когда данные функции принимают значения 1, и совпадает по знаку с воспроизводимой функцией, то накопление погрешности приводит к тому, что в

этих точкмл чн.дчемия прсиьпчпют -значение динн1у.1. Поэтому ксфрскц 1Ю вычислекий этих функций осуществляют следукицим образом: при достижении подынтегральной функ ции одного из цифровых интеграторов значения +1 (например, первого цифрового интегратора, вычисляющего функцию синуса) перекрывают кана поступления положительных приращений этой подынтегральной функции до тех пор, пока значение данной подынтегральной функции не станет меньше единицы, т.е. до тех пор, пока значение подынтегральной функции другого цифрового интегратора (в данном случае второго цифрового интегратора, вычисляющего функцию .косинуса.) не перейдет через нулевое значение и не изменит свой знак, а если значение подынтегральной функции одного из ЦИФРОВЫХ интеграторов достигает т1, то отсекают отрицательные приращения подынтегральной функции этого цифрового интегратора до тех пор, пока значение этой подынтегральной функции не станет больше -1. В результате в точках

(1с 1,2.., К ), т.е. в

т

точках, в которых функция синус или функция косинус принимают значения +1, происходит ограничение потока приращений соответствующего знака по входу приращений той функции, которая достигает этого максимального по модулю значения, и тем самым производится сбрасывание накопленных ощибок, так как на каждом

новом интервале,равном - вычисления производятся как бы с..новыми, точными исходными данньпда.

Данный алгоритм реализуется в предлагаемом устройстве для вычисления тригонометрических функций следующим образом.

В конце каждой итерации по сигналу конца итерации, поступающему через вход 19 устройства, проводится анализ знакового и старшего числового разрядов дополнительного двоичного кода как функции синуса, так и функции косинуса. Для этого код синуса поступает .с выхода кода подынтегральной функции первого цифрового интегратора 1 на информационный вход триггера 2 и через элемент задержки 3 на один такт, который служит для

синмощепия во времени и старшего числового разрядоп код;) функции, поступает на информационный вход триггера 4. Аналогично код косинуса поступает с выхода кода подынтегральной функции второго цифрового интегратора 9 на информационный вход триггера 10 и через элемент задержки 11 на один такт на информационный вход триггера 12.

Предварительная установка триггеров 2, 4, 10 и 12 в нулевое состояние производится перед началом работы устройства .подачей соответствующего сигнала на вход 18 устройства. В результате при поступлении сигнала конца итерации, совпадающего по времени со знаковым разрядом кодов подынтегральных функций, через вход 19 устройства на вход синхронизации триггеров 2, 4,10 и 12 проис содит запись знакового разряда кода синуса и кода косинуса соответственно в триггеры 2 и 10, а старшего числового разряда - соответственно в триггеры 4 и 12. Так как {СОД значения +1 для функции синуса или косинуса в цифровых интеграторах предлагаемого устройства имеет вид О,1000...О, то при достижении функцией синуса этого значения на выходе элемента И-НЕ 6 появляется нулевой сигнал, который поступает на вход элемента И 7 и закрывает его, блокируя тем самым поступление приращений из второго цифрового интегратора 9 с одноразрядными приращениями на вход положительных приращений подынтегральной функции Первого цифрового интегратора 1 и удерживая точное значение функции синус, вычисляемой в п ервом цифровом интеграторе 1, в точке экстремума. Это происходит до тех пор, пока знач..ение подынтегральной функг ции второго цифрового интегратора 9, т.е. функции косинуса, не пересечет нулевую точку и не станет отрицательньад, тогда на вход отрицательных приращений подынтегральной функции первого цифрового интегратора 1 начинают поступать через открытый элемент И 8 приращения с выхода отрицательных приращений интеграла второго цифрового интегратора 9 и вычисляемое в первом цифровом интеграторе 1 значение функции синуса становится меньше единицы, а на выходе элемента И-НЕ 6 снова появляется единичный сигнал. Аналогично и для функции косинус: при достижении функцией косинус, вьмисляемой вторым цифровьм интегратором 9, значения +1 на выходе элемента И-НЕ 1А появляется нулевой сигнал, поступающий на вход элемента И 15 и блокирующий поступление приращений из первого цифрового интегратора 1 с одноразрядными приращениями на вход.положительных приращений подынтегральной функции второго цифрового .интегратора 9 до тех пор, пока значение функции синус, вычисляемой в первом цифровом интеграторе 1, не пересечет нулевую точку, и тогда вычисляемое во втором цифровом интеграторе 9 значение функции косинус становится меньше единицы, а на выходе элемента И-НЕ 14 снова появляется единичный сигнал. Если же код функции синус или косинус будет равен 1,0111...1, т.е. функция синус или косинус достигнет значения -Г, то нулевой сигнал с выхода элемента И-НЕ 5 для функции синус поступает на вход элемента И 8 или соответственно нулевой сигнал с выхода элемента И-НЕ 13 для функции косинус поступает на вход элемента И 16, блокируя прохождение приращений на вход отрицательных приращений подынтегральной функции соответственно первого цифрового интегратора Гили второго цифрового интегратора 9 до тех пор, пока значения противоположных функций, т.е. функции косинус в случае, если значения -1 достигла функция, синус или функции синус в случае, если значения -1 достигла функция косинус, не пересекут нулевую точку,и тогда значение соответственно функции синус, если нулевую точку пересечет функция косинус, или функции косинус, если нулевую точку пересечет функция

5 синус, станет меньше единицы, а на выходе соответственно элемента И-НЕ 5 или И-НЕ 13 снова появится единичный сигнал. Вследствие этого сброс накопленнных погрещностей вычисле0 НИИ в предлагаемом устройстве осуществляется за счет удержания точных значений функций в точках экстремума.

При всех остальных значениях знакового и старшего числового разрядов кодов функций синус и косинус на выходах элементов И-НЕ 5, 6,13 и 14 и, Следовательно, на вторых входах элементов И 8, 7, 16 и 15 соответственно находится единичный сигнал, разре шающий поступление как положительных так и отрицательных приращений вычисляемых функций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Цифровой интегратор | 1985 |

|

SU1365081A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1064280A1 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| НЕПРЕРЫВНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1969 |

|

SU241121A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ, содержащее два цифровых интегратора, три эль мента И и два триггера, причем тактовые входы первого и второго интеграторов соединены с вхоДом аргумента устройства,выходы кода первого и второго цифровых интеграторов. соединены соответственно с выходом синуса и выходом косинуса устройства, отличающе еся тем, что, с целью повышения точности, в него введены третий и четвертый триггеры, четвертый элемент И, два элемента задержки и четыре элемента И-ЬЕ, причем выходы положительного и отрицательного приращений первого цифрового интегратора соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых соединены с выходами соответственно первого и второго элементов И-НЕ, первые входы которых соединены с .прямыми выходами соответственно первого и второго триггеров, инверсные выходы которых соединены с вторыми входами соответственно второго и первого элементов И-НЕ, выходы первого и второгб элементов И соединены соответственно с входом положительного приращения и отрицательного приращения второго цифрового интегратора, выходы положительного и отрицательного приращений которого соединены с первыми входами соответственно третьего и-четвертого элементов И, вторые входы которых соединены с выходами соответственно третьего и-четвертого I элементов И-НЕ, первые входы которых соединены с прямыми выходами соот(Л ветственно третьего и четвертого триггеров, инверсные выходы которых соединены с вторыми входами соответственно четвертого и третьего элементов И-НЕ, выходы третьего и четвертого элементов И соединены соответственно с входом положительСХ5 ного приращения и входом отрицателью ел ного приращения первого цифрового интегратора, выход кода которого соединен с информационным входом ел четвертого триггера и через первый элемент задержки - с информационным входом третьего триггера, выход кода второго цифрового интегратора соединен с информационным входом второго триггера и через второй элемент задержки- с информационньм входом первого триггера, тактовые входы триггеров соединены с входом окончания итерации устройства, вход сброса которого соединен с входами установки в ноль триггеров.

| Иеслуховский К.С | |||

| Цифровые дифференциальные анализаторы | |||

| - М.: Машиностроение, 1968, с.85, рис 17 | |||

| Устройство для вычисления тригонометрических функций | 1980 |

|

SU978145A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-30—Публикация

1984-04-06—Подача