дом второго распределителя импульсо четвертьп вход - с шестым выходом первого блока управления, пятый вход - с первым выходом второго реверсивного счетчика, вторые выходы которого соединены с вторыми входами регистра и с входами цифроаналого- вого преобразователя, выход которого соединен с вторым входом блока сравнения, причем вторые входы второго распределители импульсов соединены с четвертыми входами второго реверсивного счетчика, пятые входы которого соединены с первыми выходами первого реверсивного счетчика, при этом третьи входы второго распределителя импульсов соединены с выходами первого распределителя и пульсов.

2. Преобразователь по п. 1 , о т-личающийся тем, что первый блок управления выполнен .1л .двух элементах,2И-ИЛИ, двух RS-триггерах, пяти элементах И, двух элементах задержки, элементе ИЛИ, выход которого является шестым выходом первого блока управления, а первый вход соединен с выходом первого элемента задержки, вход которого объединен с 5 -входами первого и второго R5 -триггеров и является четвертым входом и пятым выходом первого блока управления, К вход первого R5 -триггера является пятым входом первого блока управления, а выход соединен с первым входом первого элемента И, второй вход которого является вторым входом первого блока управления, а выход соединен.с первыми входами третьего, четвертого и пятого элементов И, выходы которых являются

соответственно первым, третьим и четвертым выходами первого блока управления, вторые входы четвертого и пятого элементов И объединены и подключены к выходу второго элемента 2И-ИЛИ, первый и второй входы которого объединены . и подключены между собой и к D -входу второго

R5 -триггера, второму входу третьего элемента Инк выходу первого элемента 2И-ИЛИ, третий и четвертый входы второго элемента 2И-ИЛИ объединены и подключены к выходу второго R5 -триггера, С -вход которого через второй элемент задержки подключен к выходу первого элемента И

и является вторым выходом первого

блока управления, второй вход элемента ИЛИ соединен с выходом второго элемента И,первый вход которого соединен с выходом второго элемента задержки, а второй вход является шестым выходом первого блока управления, первый и второй, третий и четвертый входы первого элемента 2И-ИЛИ попарно объединены и являются соответственно первым и третьим входами первого блока управления.

3. Преобразователь по п.1, отличающийся тем, что второй блок управления выполнен n.i двух элементах 2И-ИЛИ, пяти RSтриггерах, трех элементах задержки, четырех элементах ИЛИ, семи элементах И, R -входы первого, второго, третьего, 6 -вход четвертого R5 -триггеров и первый вход второго элемента ИЛИ объединены и являются четвертым входом и первым выходом второго блока управления, R -вход четвертого R5 -триггера соединен с выходом первого элемента ИЛИ, первый вход которого объединен с вторым входом второго элемента ИЛИ, входом второго эле1мента задержки и первым входом четвертого элемента И и подключен к выходу шестого элемента И, второй вход четвертого элемента И и первый вход пятого элемента И, J) -вход первого R5 -триггера, первый вход первого элемента И, первый и второй входы второго элемента 2И-ИЛИ объединены и подключены к выходу первого элемента 2И-ИЛИ, третий и четвертый входы второго элемента 2И-ИЛИ объедин(;ны и подключены к выходу первого RS -триггера, а пятый и шестой входы объединены и подключены к выходу третьего RS -триггера, Ь вход которого объединен с С -входом первого R5 -триггера и первым входом четвертого элемента ИЛИ и подключен к выходу первого элемента задержки, второй вход четвертого

элемента ИЛИ и 5 -вход второго элемента задержки объединены и подключены к выходу второго элемента задерж.ки и является шестым выходом второго блока управления, третий вход четвертого элемента ИЛИ и первый вход треть. элемента ИЛИ объединены и подключены к выходу пятого элемента И, а выход четвертого элемента ИЛИ является третьим вы :одом второго блока управления, второй вход третьего

элемента ИЛИ соединен с выходом первого элемента И, третий вход - с выходом четвертого элемента И, а выход является вторым выходом второго блока управления, первьй и второй, третий и четвертый входы элемента 2И-ИЛИ попарно объединены и являются соответственно первым и пятым входами второго блока управления, выход второго R5 -триггера является пятым выходом второго блока управления, второй вход первого элемента ИЛИ соединен с выходом третьего элемента И, первый вход которого и первый вход второго элемента И объединены и подключены к выходу четвертого R5 -триггера, второй вход третьего элемента И, первы входы шестого и седьмого элементов И и второй вход второго элемента

И объединены и являются вторым вХодом второго элемента блока управления, а третьи входы третьего и второго элементов И объединены и соединены с вьоходом второго элемента 2И-ИЛИ, выход второго и второй вход первого элемента И объединены и подключены к входу первого элемента за,цержки, а выход второго элемента ИЛИ соединен с R -входом пятого RS -триггера, выход которого соединен с вторыми входами шестого и седьмого элементов И, третьи входы которых объединены и являются третьим входом второго блока управления, выход седьмого элеметхта И подключен к второму входу пятого элемента И и является четвертым выходом второго блока управле НИН .

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1179538A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1594691A1 |

| Датчик угловых перемещений | 1989 |

|

SU1725069A1 |

| Устройство для формирования символов на экране электронно-лучевой трубки | 1984 |

|

SU1251061A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Вибрационный источник сейсмических сигналов | 1983 |

|

SU1138772A1 |

| Преобразователь перемещения в код | 1988 |

|

SU1654973A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

| Устройство для управления асинхронным электроприводом | 1987 |

|

SU1522373A1 |

1. СЛЕДЯЩИ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий первый блок сравнения, первый вход которого соединен с входной шиной, а второй вход - с выходом первого цифроаналогового преобразователя, входы которого соединены с первыми выходами первого реверсивного счетчика, выход блока сравнения соединен с первым входом первого блока управления, второй вход которого соединен с выходом генератора тактовых импульсов, третий вход - с вторым выходом первого реверсивного счетчика, четвертый вход - с шиной Запуск, а пятый вход - с шиной Стоп, первый выход - с первыми входами первого реверсивного счетчика, второй выход - с вторыми входами первого реверсивного счетчика, третьи входы которого соеданены с выходами первого распределителя импульсов, третий выход первого блока управления соединен с первым входом первого распределителя импульсов, четвертый выход - с первым входом логического блока, а пятый выход - с четвертым входом первого -реверсивного счетчика и вторым входом первого распределителя импульсов, третий вход которого соединен с выходом логического блока, вторые входы которого соединены с первыми выходами первого реверсивного счетчика, а третьи входы - с выходами первого распределителя импульсов, отличающийся тем, что, с целью уменьшения погрешности преобразования, в него введены регистр и поразрядный аналого-цифровой преобразователь, выполненный на аналоговом запоминающем устройстве, втором цифроаналоговом образователе, втором реверсивном (Л счетчике, втором распределителе импульсов, втором блоке управления и втором блоке сравнения, первый вход которого соединен с выходом аналогового запоминающего устройства, первый вход которого соединен с входной шиной, второй вход объединен с первыми входами второго распределителя импульсов и второго ревер QD J О СО сивного счетчика и подключен к первому выходу второго блока управления, второй выход которого соединен с вторыми входами второго per версивного Счетчика, третий выход с третьими входами-второго реверcjHBHoro счетчика, четвертый вы- .. ход - с вторым входом второго распределителя импульсов, пятый выход - с шиной Готовность и шестым входом первого блока управления, шестой выход - с первым входом регистра, первый вход - с выходом второго блока сравнения, второй вход - с выходом генератора импульсов, третий вход - с первым выхо

Предлагаемое устройство относится к вычислительной и измерительной технике, а также может быть использовано в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

Целью изобретения является уменьшение погрешности преобразования.

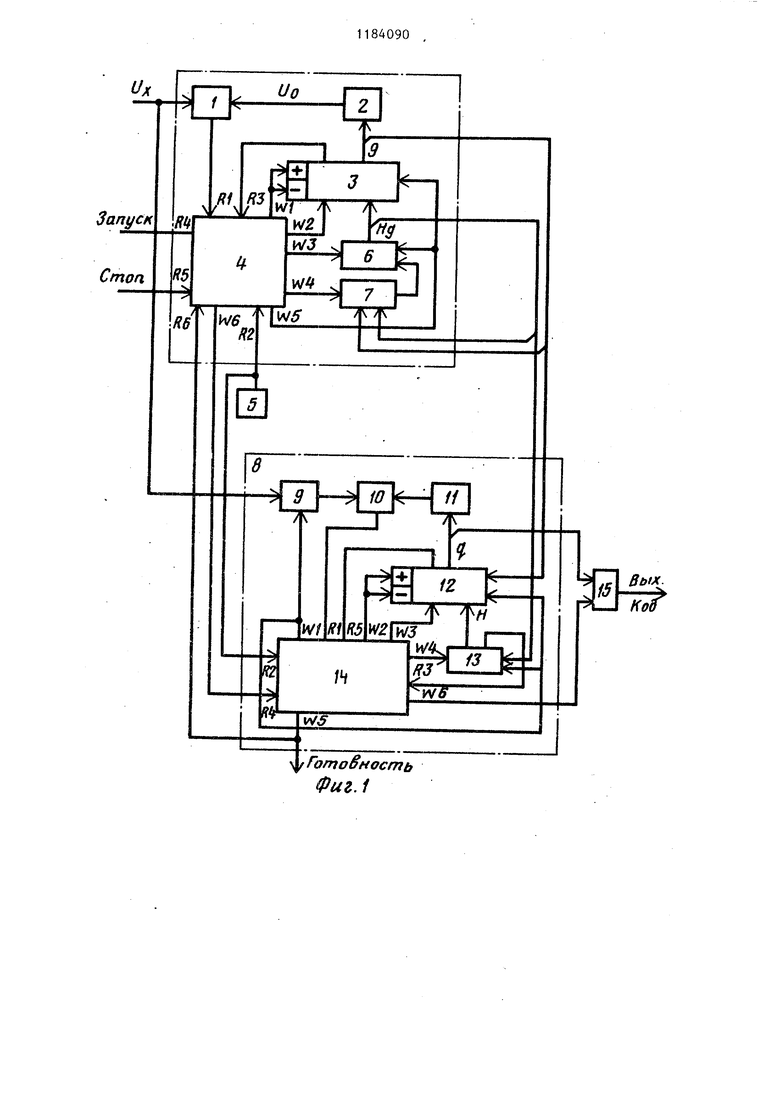

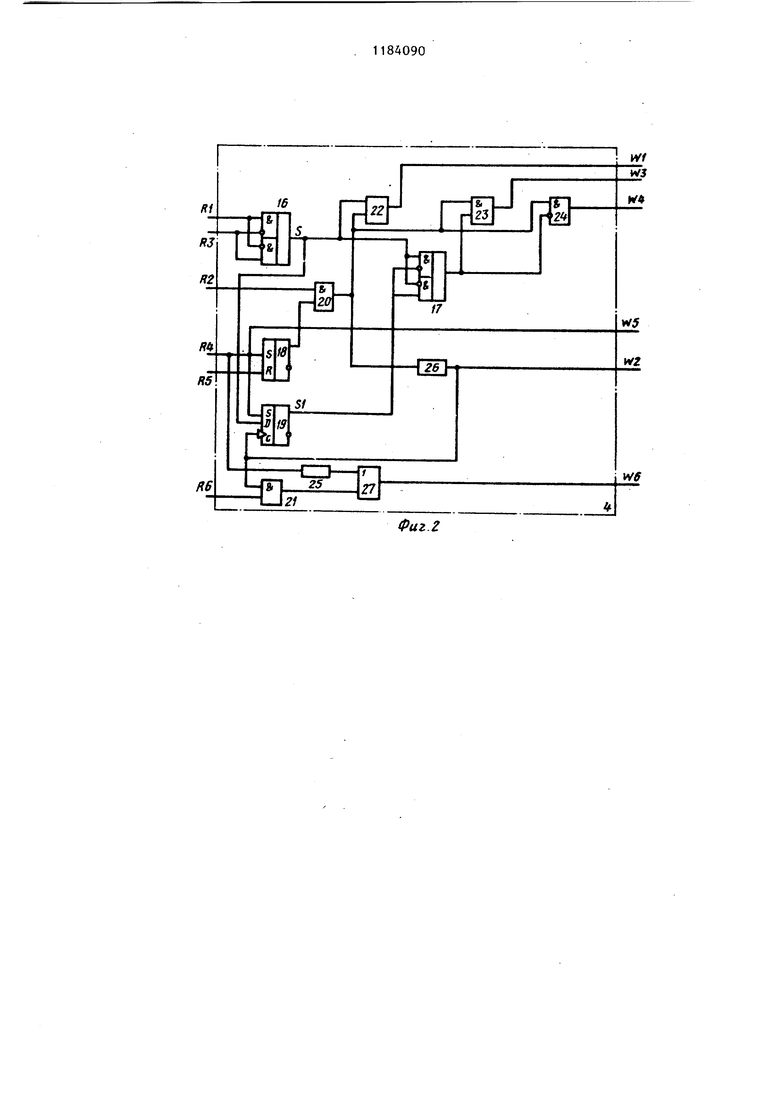

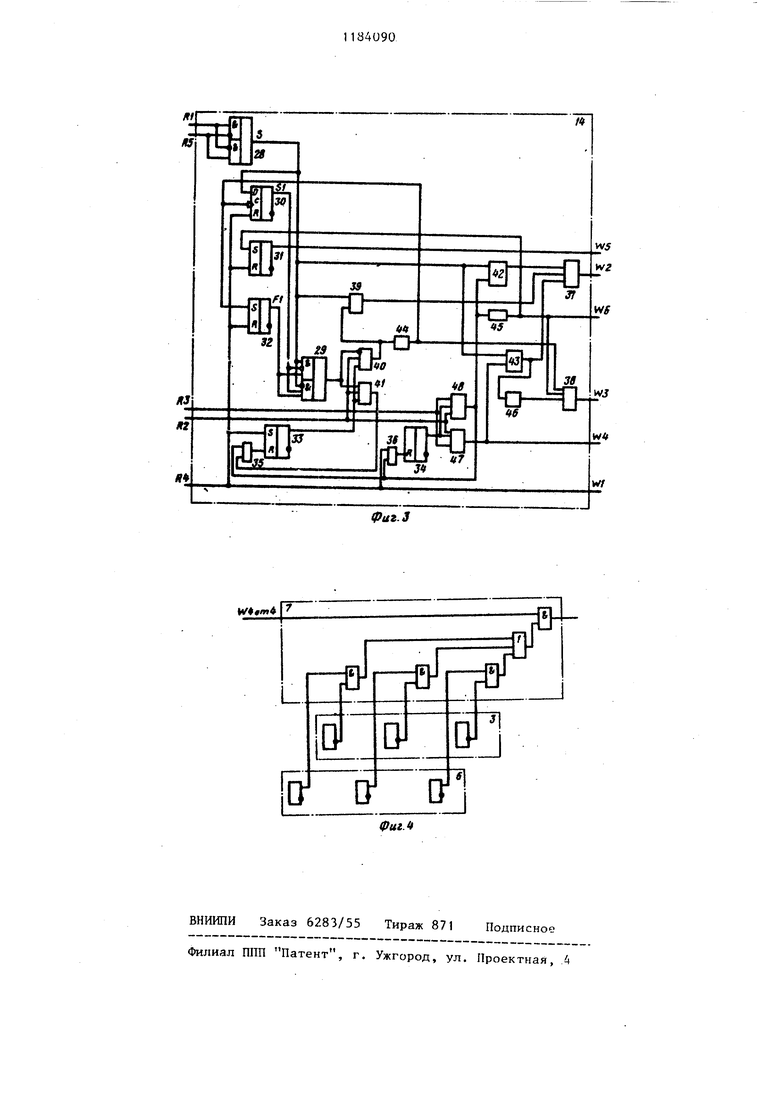

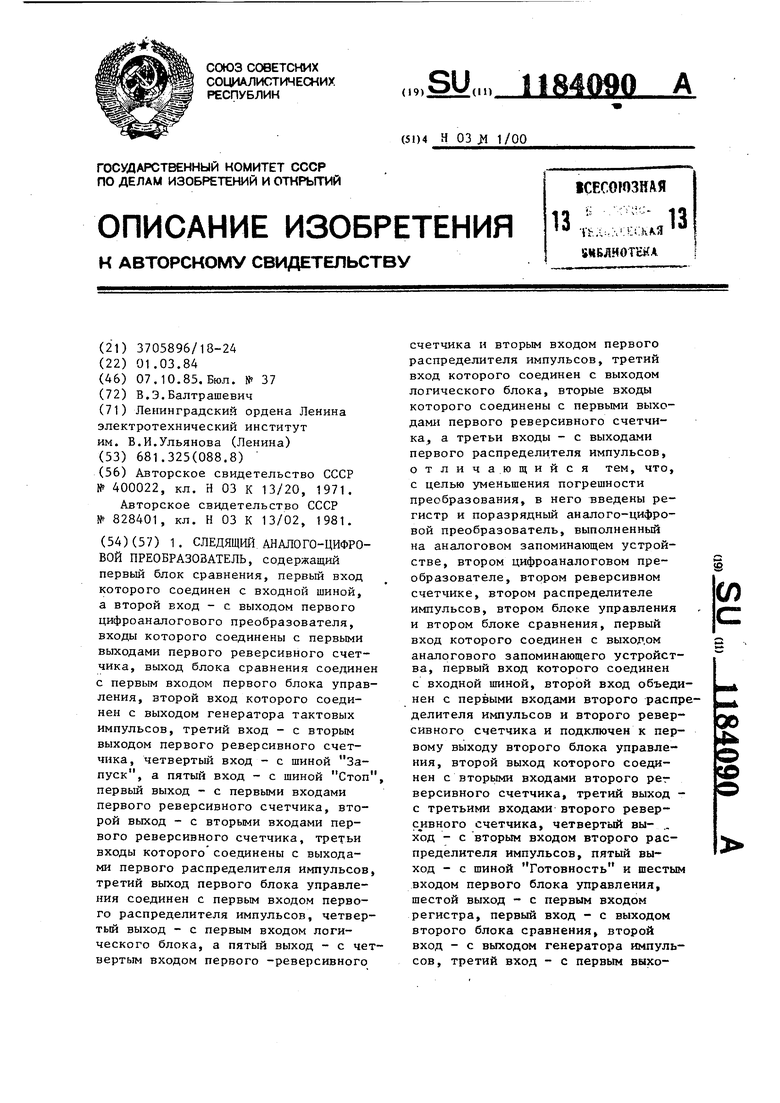

На фиг. 1 представлена функциональная схема предлагаемого следящего аналого-цифрового преобразователя; на фиг. 2 - первый блок управления; на фиг, 3 - второй блок управления; на фиг. 4 - логический блок.

Аналого-цифровой преобразовател (АЦП) содержит первый блок 1 сравнения, первый вход которого соединен с выходом первого цифроаналогового преобразователя 2, цифровые входы которого ,соединены с выходами соответствующих триггеров (кроме триггера переполнения) первого реверсивного счетчика 3, выход блока 1 сравнения соединен с первым входом первого блока 4 управления, второй вход которого соединен с выходом генератора 5 тактовых импульсов, третий вход

соединен с триггером переполнения реверсивного счетчика 3, четвертьш вход соединен с шиной Запуск, а пятый вход соединен с шиной Стоп, первый выход первого блока 4 управления соединен с входом установки режима работы первого реверсивного счетчика 3, второй выход соединен с управляющими входами разрядов первого реверсивнсго

счетчика 3, установочные входы разрядов которого соединены с выходами соответствуюЕХИх разрядов первого распределителя 6 импульсов,

третий выход первого блока 4 управления соединен с входом сдвига вправо первого распределителя 6 импульсов, четвертый выход соединен с входом логического блока 7

а пятый выход соединен с входами начальной установки первого реверсивного счетчика 3 и первого распределителя 6 импульсов, выход логического блока 7 соединен с

входом сдвига влево первого распределителя 6 импульсов, первая группа входов логического блока 7 соединена с выходами соответствующих разрядов реверсивного счетчика 3,

а вторая группа входов соединена с выходами соответствующих разрядо распределителя 6 импульсов, первый вход первого блока 1 сравнения соединен с входом поразрядного аналого-цифрового преобразователя 8 (АЦП), содержащего аналоговое запо минающее устройство 9, второй блок 10 сравнения, второй циф- циф роаналоговый преобразователь 11, второй реверсивный счетчик 12, вто рой распределитель 13 импульсов и второй блок 14 управления, регистр 15. Первый блок 4 управления содержит два элемента 2И-ИЛИ , 16-17, два R5 -триггера 18,19,,пять элементов 20-24 И, два элемента 25-26 задержки элемент ИЛИ 27,второй блок 14 управления содержит два элемента управления содержит два элемейта 2И-ИЛИ 28-29, пять RS -триггеров 30-34, четыре элемента ИЛИ 35-38, пять элементов И 39-43, три элемента 44-46 задержки, два элемента И 47-48. Устройство работает следующим образом. Работа первого АЦП (фиг.1) почти полностью совпадает с работой известного (за исключением выдачи сигнала W 6 при условиии появления сигнала R 6). В работе устройства используются следующие внутренние логические переменные: S - текуп1Ий результат сравнения; S1 - результат сравнения на предьщущем такте. Вначале первый блок 4 управления устанавливает начальное значение результата сравнения на предьдущем такте S1: - TRUE и вьщает сигнал на пятом выходе, который производит начальную установку, т.е. устанавливает в первом реверсивном счетчик 3 код 10....О и в первом распредели теле 6 импульсов код 10....0. Под действием тактовых импульсов, поступающих на второй вход, первый блок 4 управления работает до появл ч ния сигнала Стоп на пятом входе. Текущий результат сравнения S формируется по формуле S; R1 R V R1 по этому же правилу формируется и сигнал на первом выходе первого бло ка 4 управления, причем на первый вход поступает сигнал с первого блока 1 сравнения, а на третий вход - сигнал с триггера переполнения реверсивного счетчика 3. Сигнал с первого выхода устанавливает режим работы реверсивного счетчика 3 по правилу if W1 then + else - . Затем осуществляется формирование величины шага квантования, для этого в зависимости от результата сравнения на текущем и предыдущем такте формируется сигнал на третьем или четвертом выходах первого блока 4 управления по формулам . W3: S S1 V S ; W4: S-S1VS.S1. В случае чередования результатов сравнения по сигналу с третьего выхода осуществляется сдвиг вправо распределителя 6 импульсов, т.е. шаг квантования уменьшается вдвое (в предлагаемом устройстве так же как и в известном предполагается запрещенным сдвиг вправо при коде О01). Если результаты сравнения на текущем и предыдущем такте совпадаюту то сигналом с четвертого выхода опрашивается логический блок 7, на выходе которого появляется сигнал только при условии нулевого состояния разряда первого реверсивного счетчика 3, на который указывает единичный разряд распределителя 6 импульсов. Этот сигнал осуществляет сдвиг влево содержимого распределителя импульсов, т.е. увеличивает вдвое значение шага квантования. После формирования величины шага квантования проводится формирование величины числового эквивалента. ,Чля этого первьй блок 4 управления выдает сигнал с второго выхода, который формирует величину текущего числового эквивалента, т.е. g: g jf Н q , где V- - сложение или вычитание в зависимости от режима работы реверсивного счетчика, установленного сигналом с первого выхода первого блока 4 управления. Кроме того, блок управления обеспечивает запоминание текущего результата сравнения, т.е. S1: S. После этого первый блок 4 управления проверяет готовность поразрядного АЦП 8, т.е. он выдает сигнал

с шестого выхода при условии появления сигнала на шестом входе, этот сигнал от первого блока 4 управления запускает второй блок 14 управления. С приходом очередного тактового импульса описанные действия первого блока 4 управления повторяются.

После прихода сигнала на четвертьш вход второго блока 14 управления это устройство выдает сигнал с первого выхода, который включает аналоговое запоминающее устройство 9, переписывает содержимое первого реверсивного счетчика 3 и первого распределителя 6 импульсов соответственно во второй реверсивный счетчик 12 и во второй распределитель 13 импульсов, кроме того блок управления сбрасывает сигнал готовности и вспомогательный признак F , который предназначен для организации полноценной проверки чередования ответов блока сравнения (начиная с второго такта).

Вначале второй блок 14 управления, не меняя величины шага квантования, проводит уточнение поддиапазпна расположения входного сигнала, до смены ответа блока сравнения Необходимость этого уточнения вызвана тем, что следящий АЦП может отстать от входного сигнала.

Текущий результат сравнения S формируется по формуле

S: R1 R5 V RT . R5,

причем на первый вход поступает сигнал с второго блока 10 сравнения, а на пятый вход - сигнал с триггера переполнения второго реверсивного счетчика 12.

Уточнение поддиапазона расположения сигнала производится до тех пор, пока не станет верным условие ( S . Ь V s S1-) -Fl R2. В процессе уточнения второй блок 14 управления сигналом с второго выхода устанавливает режим работы ВТОРОГО реверсивного счетчика 12 в соответствии с ответом блока 10 сравнения. Затем сигнал с третьего выхода формирует величину текущего числового эквивалента л т.е. q: , где if-- сложение или вычитание в зависимости от режима работы второго реверсивного счетчика 12, установленного сигналом с второго выхода блока 14 управления. Кроме того, блок 14 управления обеспечивает запоминание щего результата сравнения, т .е. S1: S и устанавливает признак F1. После уточнения поддиапазона второй блок 14 управления обеспечивает поразрядный поиск сигнала, отличающийся от классического только тем, что результат сравнения формируетс я

(как указывалось) по формуле R1 R5 V R1 R5,T.e, до тех пор, пока не появится единица в младшем разряде .

I

второго распределителя 13 и myльcoв, второй блок 14 управления поочередно выдает сигналы с четвертого выхода (уменьшает шаг квантования вдвое, т.е. осуществляет сдвиг вправо второго распределителя 13 импульсов), с второго выхода (устанавливает режим работы второго реверсивного счетчика 12 в зависимости от результатов сравнения) и третьего выхода (формирует величину текущего числового эквивалента, т.е. q: ,

где ( - сложение или вычитание в зависимости от значения сигнала на втором выходе). После появления единицы в младшем разряде распределителя импульсов 13, т.е. при достижении минимального шага квантования, второй блок 14 управления в случае необходимости (т.е. q ; Vj )с помощью сигналов с второго и третьего выходов осуществляет коррек1Ц1ю числового эквиалента; выдает сигнал на шес.том выходе, осуществляющий переписывание числового эквивалента с второго реверсивного счетчика 12 в регистр 15 данных и еьщает сигнал готовности. Запуск Стоп ф Готовност Фиг. 1 ь

rW гтга-f

16

a

51

13

Ьрь

25

/7

-Lj2f

JVJ K4

I- r г5

17

IV/

W6

Фиг. г

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 0 |

|

SU400022A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-10-07—Публикация

1984-03-01—Подача