так 2И-ИЛИ, девяти элементах И, пяти элементах ИЛИ, четьфех элементах задержки, пяти RS-триггерак, R-входы первого, второго и третьего RS-триггеров, первый вход второго элемента И и первый вход четвертого элемента И объединены, подключены к выходу первого элемента И и являются первым, восьмым и девя-тым выходами блока управления, D-вход первого RS-триггера объединен с вторым входом второго элемента И и первыми входами седьмого, восьмого и девятого элементов И и подключен к выходу первого элемента 2И-ИЛИ, выход девятого элемен-. та И соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом седьмог элемента И, третий вход соединен с выходом второго элемента И, а выход является вторым выходом блока управления, С-вход первого КЗ-триггера объединен с первым входом пятого элемента ИЛИ и подключен к выходу первого элемента задержки, вход которого объединен с входом третьего RS-триггера, подключен к выходу третьего элемента И и является пятьтм выходом блока управления, выход третьего RS-триггера соединен с первым и вторым входами второго элемента 2И-ИЛИ, третий и четвертый входы которого объединены и подключены к выходу первого RS-триггера, пятый и шестой входы объединены и подключены к выходу первого элемента 2ИИПИ, первый и второй входы которого объединены и являются первым входом блока управления, третий и четвертый входы также объединены и являются вторым входом блока управления, S-вход второго RS-триггера соединен с выходом второго элемента задержки и является одиннадцатым выходом блока управления, вход второго элемента задержки объединен с вторым восьмого элемента И, подключен к выходу третьего элемента задержки и является десятым выходом блока управления, вход третьего элемента задержки объединен с вторым входом седьмого элемента И, первым входом третьего элемента ИЛИ, первым входо второго элемента ИЛИ и подключен к выходу пятого элемента И, второй вход второго элемента ИЛИ объединен с вторым входом третьего элемен9538

та ИЛИ и является пятым входом, шее-тым выходом блока управления, выход третьего элемента ИЛИ соединен с Е-входом пятого RS- триггера, З-вход которого объединен с первым входом первого элемента ИЛИ и подключен к выходу четвертого элемента И, второй вход первого элемента ИЛИ является шестым входом блока управления, а выход соединен с R-входом четвертого КЗ-триггера, З-вход которого соединен с выходом второго элемента ИЛИ, а вькод - с первым входом первого элемента И, второй вход которого объединен с первьми входами пятого и шестого элементов И и . является четвертым входом блока управления, вторые входы пятого и шестого элементов И объединены и подключены к выходу пятого КЗ-триггера, третьи входы пятого и шестого элементов И объединены и подключены к третьему входу блока управления, выход шестого элемента И соединен с вторым входом девятого элемента И, входом четвертого элемента задержки и является четвертым выходом блока управления, йыход четвертого элемента задержки соединен с вторым входом пятого элемента ИЛИ, третий вход которого соединен с выходом восьмого элемента И, а выход является третьим выходом блока управления, выход второго RS-триггера является седьмым выходом блока управления.

3.Устройство по п. 1, отличающееся тем, что первый логический блок выполнен на п-элементах И по числу разрядов счетчика, элементе ИЛИ, дополнительном элементе И, выход которого является выходом первого логического блока, первый вход является третьим входом первого логического блока, а второй , вход соединен с выходом элемента ИЛИ, входы которого соединены с выходами соответствующих элементов И, первый входы которых являются первыми входами первого логического блока, а вторые входы - вторыми входами первого логического блока.

4.Устройство по п. 1, отличающееся тем, что второй логический блок выполнен на двух группах элементов ИЛИ, каждая из которых содержит (п-1)-элементов, двух группах элементов И, каждая из которых содержит (п-1) и (п-2)-элементов

соответственно, первые входы элементов И первой группы элементов И являются соответствующими первыми входами второго логического блока, вторые входы, кроме первого и последнего элементов, подключены к выходам предыдущих элементов И второй группы элементов И и объединены с первыми входами соответствующих элементов И второй группы элементов И, второй вход первого элемента И первой группы элементов И объединен с первым входом первого элемента И второй группы элементов И и является вторым входом второго блока, а второй вход последнего элемента Н второго логического блока соединен с выходом последнего элемента И второй группы элементов И, выходы элементов И первой группы элементов И подключены к первым входам соответствующих последовательно соединенных элемен- -ов ИЛИ первой и второй групп элементов ИЛИ,выходы элементов ШМ первой группы элементов ИЛИ являются первыми выходами второго логического блока, выходы элементов ИЛИ второй группы элементов ИЛИ являются вторыми выходами второго логического блока, а вторые входы элементов И второй группы элементов И являются первыми входами второго логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1184090A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2140098C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Итерационный преобразовательчАСТОТА-КОд | 1979 |

|

SU842617A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

1. СЛЕДЯП1ИЙ АНАЛОГО-ЦИФРО.ВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок сравнения, первый вход которого соединен с выходом аналогового запоминающего устройства, первый вход которого соединен с входной шиной, второй вход блока сравнения соединен с выходом цифроанапогового преобразователя, входы которого соединены ; с первьшш выходами реверсивного счетчика, первые входы которого соединены с первыми выходами сумматора, первые выходы реверсивного счётчика соединены с первыми входами первого логического блока, вторые входы которого соединены с первыми выходами сумматора, а выход - с первым входом сумматора, выход блока сравнения соединен с первым входом блока управления, второй вход которого соединен с вторым выходом реверсивного счетчика, третий вход - с вторым выходом сумматора, четвертый вход - с вькодом генератора тактовых импульсов, пятый вход - с шиной Запуск, шестой вход с шиной Стоп, первый выход - с вторым входом аналогового запоминающего устройства, второй выход - с вторыми входами реверсивного счетчика, третий выход - с третьими входами реверсивного счетчика, четвертый выход с вторым входом сумматора, пятый выход - с третьим входом первого логического блока, шестой выход - с четвертым входом реверсивного счетчика и третьим входом сумматора, седьмой выход - с щиной Готовность, отличающийся тем, что, с целью уменьшения времени преобразования, в устройство введены второй логический блок и выходной регистр, причем (Л третьи выходы сумматора соединены с первыми входами второго логического блока, первые выходы которого соединены с четвертыми входами сумматора, а вторые выходы - с пятыми входами реверсивного счетчика, при этом второй вход второго логического блока соединен с восьмым выходом блока ч управления, девятый выход которого соединен с пятым входом сумматора, СП .десятый выход - с шестым входом сумСА9 матора, одиннадцатый выход - с пер00 вым входом выходного регистра, второй вход которого соединен с шестым выходом блока управления, -третьи входы - с первыми выходами реверсивного счетчика, а выходы - с выходной шиной устройства и седьмыми входами сумматора, восьмые входы которого соединены с первыми выходами реверсивного счетчика.. 2. Устройство по п. 1, отличающееся тем, что блок управления вьтолнен на двух элемен

Изобретение относится к аналогоЩ1ФРОВЫМ преобразователям и может быть использовано в связи, вычислительной и измерительной технике, а также в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

Целью изобретения является уменьшение времени преобразования.

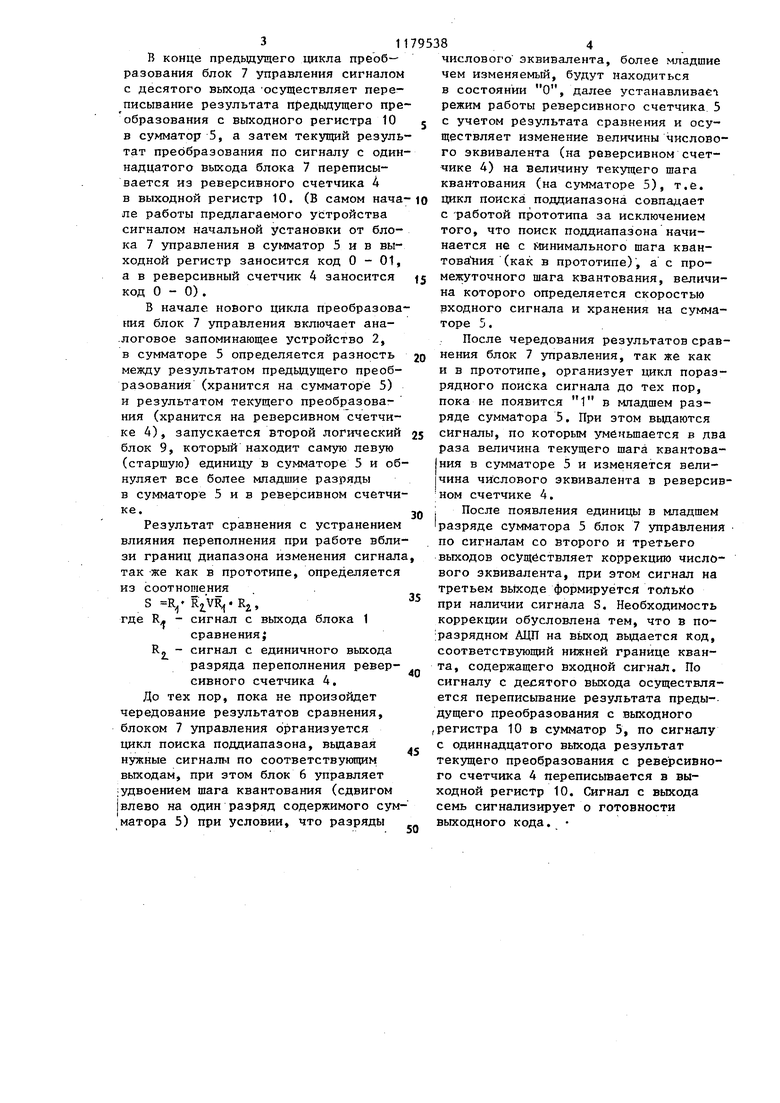

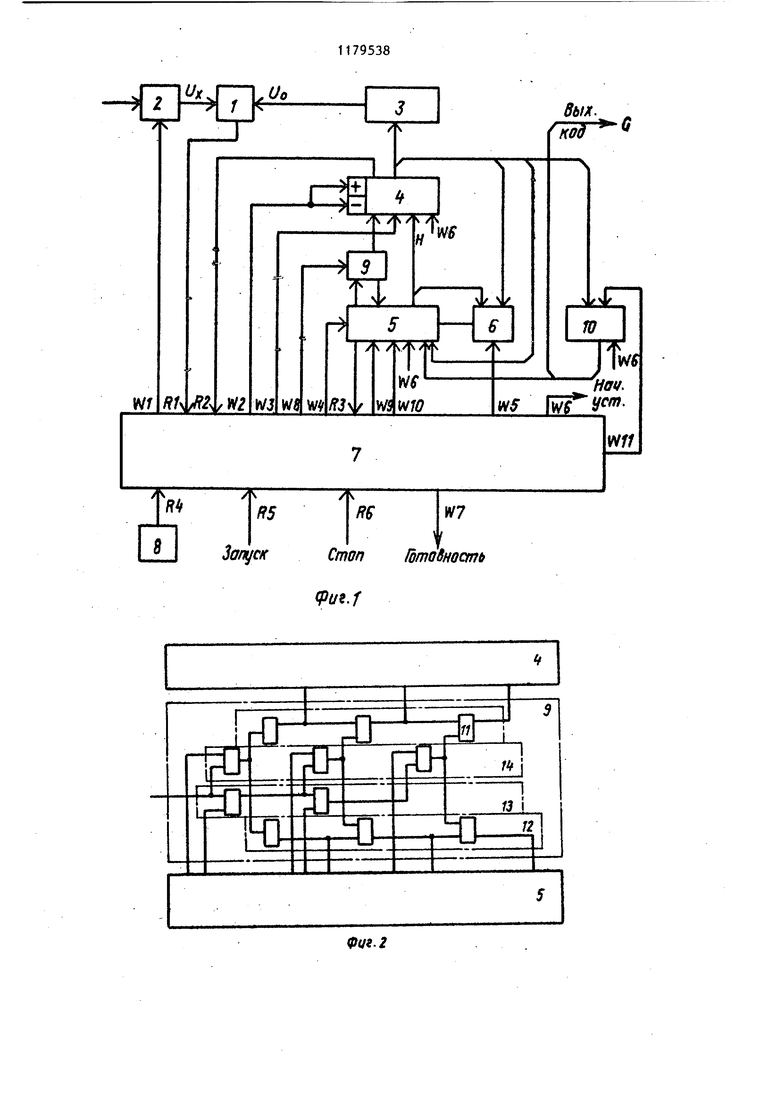

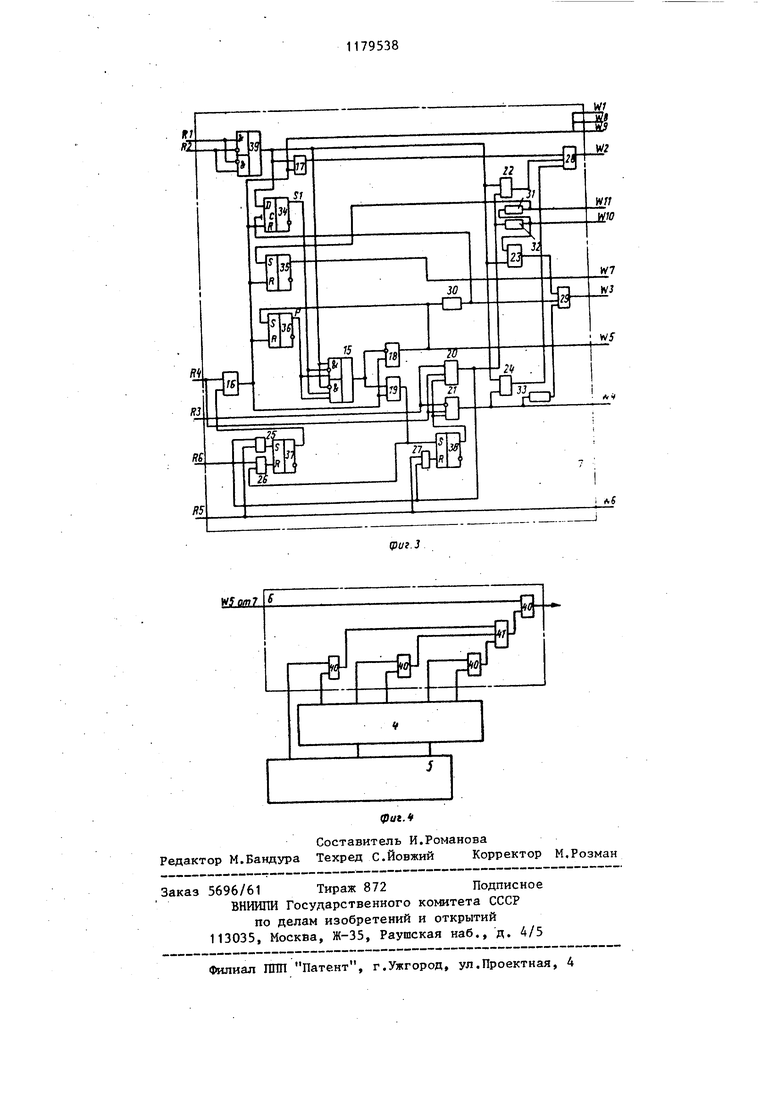

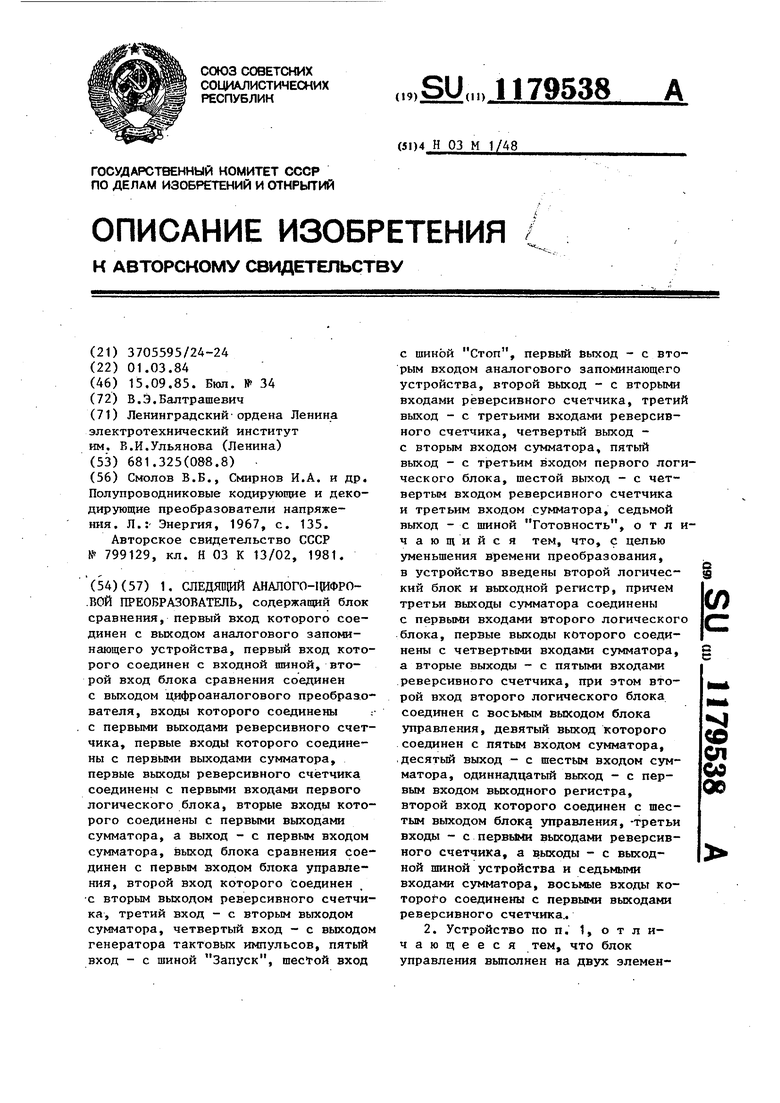

На фиг. 1 представлена функциональная схема следящего аналого-цифрового преобразователя; на фиг. 2 пример реализации второго логического блока; на фиг. 3 - то же, блока управления; на фиг. 4 - то же, первого логического блока,

Предлагаемый следящий аналого-цифровой преобразователь содержит блок 1 сравнения, первый вход которого соединен с вь1ходом аналогового запоминающего устройства 2, вход которого соединен с источником входного сигнала, второй вход блока 1 сравнения соединен с выходом цифроаналогового преобразователя 3, входы которого соединены с первыми вькодами реверсивного счетчика 4, первые входы реверсивного счетчика 4 соединены с первыми выходами сумматора 5, первые выходы реверсивного счетчика 4 соединены с первыми входами первого логического блока 6, вторые входы которого соединены с первыми выходами

сумматора 5, а выход - с входом сдвига влево сумматора 5, выход блока 1 сравнения соединен с первым входом блока 7 управления, четвертый вход блока 7 управления соединен с выходом генератора 8 тактовых импульсов, второй логический блок 9, седьмые входы сумматора 5 соединены с выходами выходного регистра 10, первые входы которого соединены с первыми выходами реверсивного счетчика 4.

Второй логический блок содержит две группы элементов 11-12 ИЛИ, две группы элементов 13-14 И.

Блок управления содержит первый элемент 15 2И-ИЛИ, девять элементов (16-24) И, пять элементов (25-29) ИЛИ четыре .элемента (30-33) задержки, пять RS- (34-38) триггеров, второй элемент 39 2И-ИПИ.

Первый логический блок содержит элементы 40 И и 41 ИЛИ.

Устройство работает следующим образом.

В начале нового цикла преобразования оценивается скорость изменения входного сигнала с помощью определения разницы между.текущим и предыдущим результатами преобразования. Текущий результат преобразования получается на реверсивном счетчи-; ке 4, а предыдущий результат преобразования хранится на выходном регистре 10. В конце предьвдущего цикла преоб- разования блок 7 управления сигналом с десятого выхода осуществляет переписывание результата п едыдущего пре образования с выходного регистра 10 в сумматор 5, а затем текущий резуль тат преобразования по сигналу с один надцатого выхода блока 7 переписывается из реверсивного счетчика 4 в выходной регистр 10, (В самом нача ле работы предлагаемого устройства сигналом начальной установки от блока 7 управления в сумматор 5 и в выходной регистр заносится код 0-01, а в реверсивный счетчик 4 заносится код О - 0) . В начале нового цикла преобразова ния блок 7 управления включает ана.логовое запоминающее устройство 2, в сумматоре 5 определяется разность между результатом предьщущего преобразования (хранится на сумматоре 5) и результатом текущего преобр азования (хранится на реверсивном счетчике 4), запускается второй логический блок 9, который находит самую левую (старшую) единицу в сумматоре 5 и об нуляет все более младшие разряды в сумматоре 5 и в реверсивном счетчи ке. Результат сравнения с устранением влияния переполнения при работе вбли зи границ диапазона изменения сигнал так -же как в прототипе, определяется из соотношения S Rj, где R. - сигнал с выхода блока 1 сравнения; R. - сигнал с единичного выхода разряда переполнения реверсивного счетчика 4, До тех пор, пока не произойдет чередование результатов сравнения, блоком 7 управления организуется цикл поиска поддиапазона, выдавая нужные сигналы по соответствующим выходам, при этом блок 6 управляет ;удвоением шага квантования (сдвигом Гвлево на один разряд содержимого сум матора 5) при условии, что разряды числового эквивалента, более младшие чем изменяемый, будут находиться в состоянии О, далее устанавливаем режим работы реверсивного счетчика 5 с учетом результата сравнения и осуществляет изменение величины числового эквивалента (на реверсивном счетчике 4) на величину текущего шага квантования (на сумматоре 5), т.е. цикл поиска поддиапазона совпадает с работой прототипа за исключением того, что поиск поддиапазона начинается не с Минимального шага квантоваиия (как в прототипе), а с промежуточного шага квантования, величина которого определяется скоростью входного сигнала и хранения на сумматоре 5. После чередования результатов сравнения блок 7 управления, так же как и в прототипе, организует цикл поразрядного поиска сигнала до тех пор, пока не появится 1 в младшем разряде сумматора 5. При этом выдаются сигналы, по которым уменьшается в два раза величина текущего шага квантования в сумматоре 5 и изменяется величина числового эквивалента в реверсивном счетчике 4. После появления единицы в мпадшем разряде сумматора 5 блок 7 управления по сигналам со второго и третьего выходов осуществляет коррекцию числового эквивалента, при этом сигнал на третьем вь1ходе формируется при наличии сигнала S. Необходимость коррекции обусловлена тем, что в поразрядном АЦП на вькод выдается Код, соответствующий нижней границе кванта, содержащего входной сигнал. По сигналу с десятого выхода осуществляется переписывание результата предыдущего преобразования с выходного регистра 10 в сумматор 5, по сигналу с одиннадцатого выхода результат текущего преобразования с реверсивного счетчика 4 переписывается в выходной регистр 10. Сигнал с выхода семь сигнализирует о готовности выходного кода.

UK.

Uo

r-

r

wajw

Ш

WJ

ff«

a

JoyycrГя / / Готовность

fpu.r

Вых.

w

m

//w. v5

фуг. 2

| Смолов В.В., Смирнов И.А | |||

| и др | |||

| Полупроводниковые кодирующие и декодирующие преобразователи напряжения | |||

| Л.: Энергия, 1967, с | |||

| Способ обделки поверхностей приборов отопления с целью увеличения теплоотдачи | 1919 |

|

SU135A1 |

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-09-15—Публикация

1984-03-01—Подача