25

35

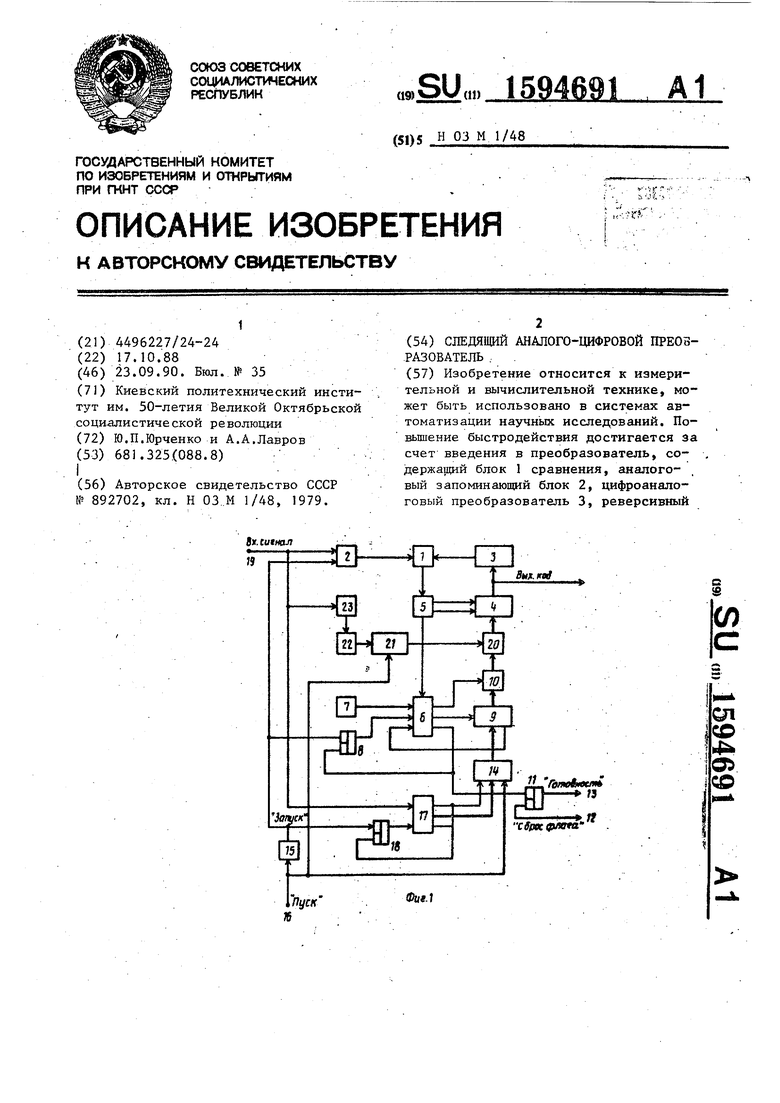

Изобретение относится к анапого-.. Цифровым преобразователям (АЦП) и моет быть использовано в измерительной И вычислительной технике, в системах автоматизации научных исследований.

Целью изобретения является повьте- ние быстродействия.

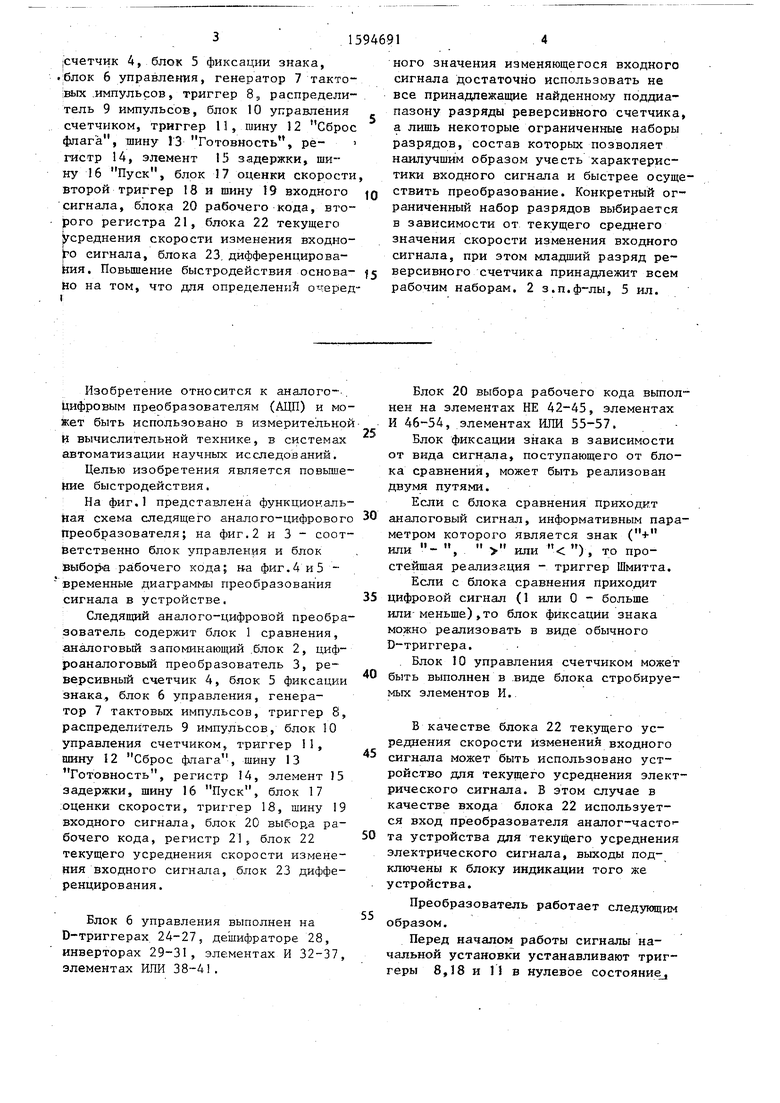

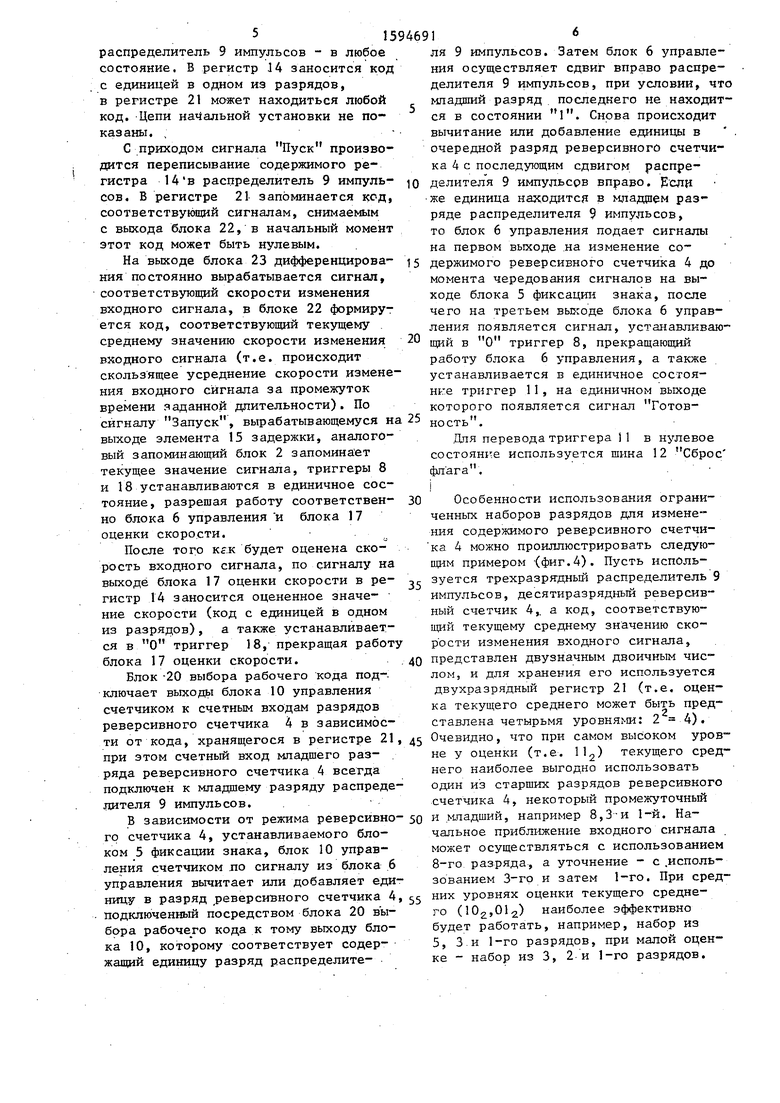

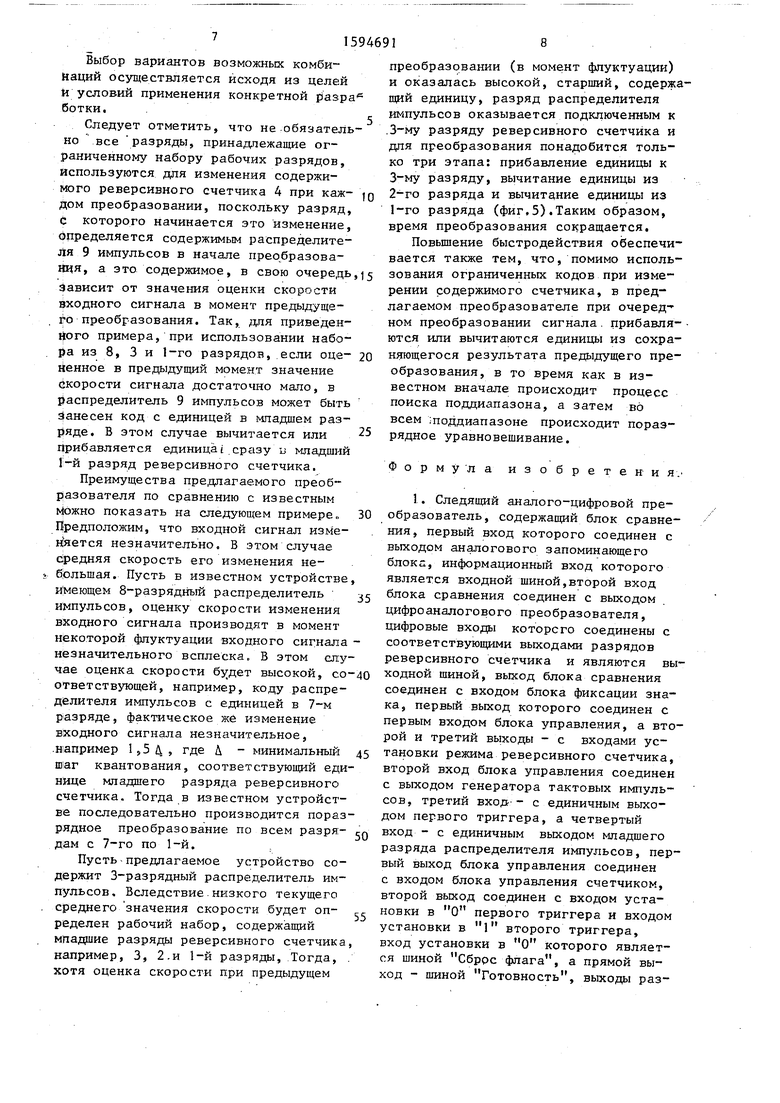

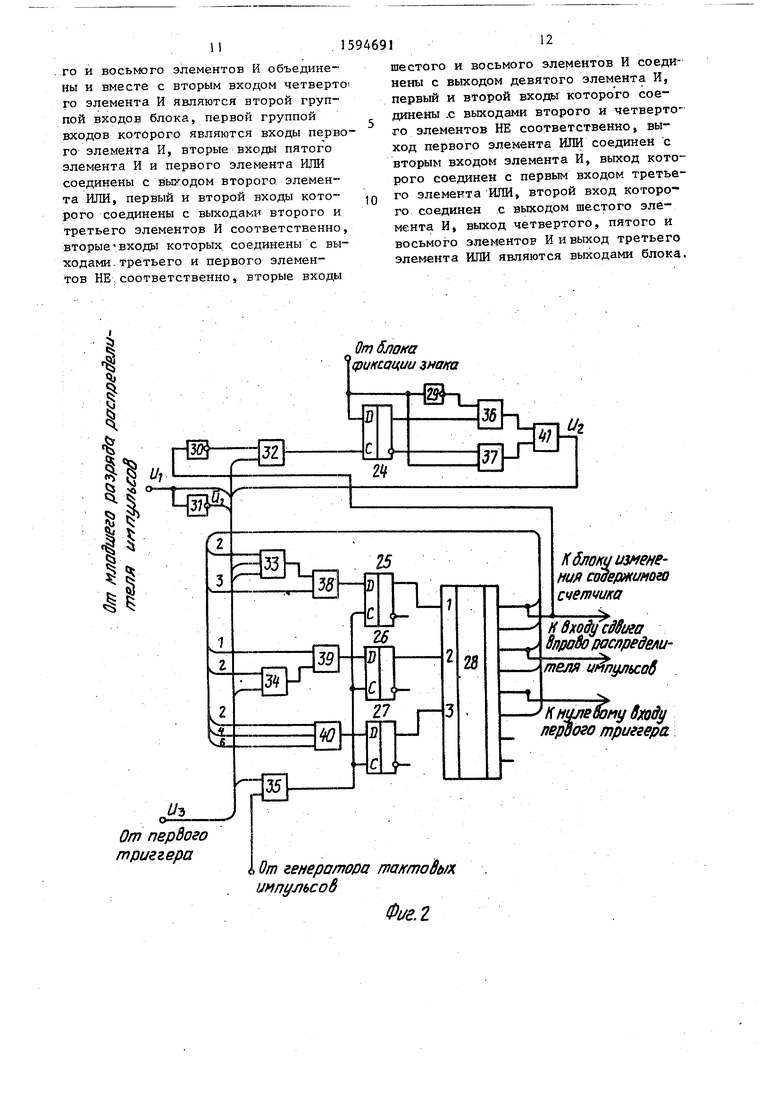

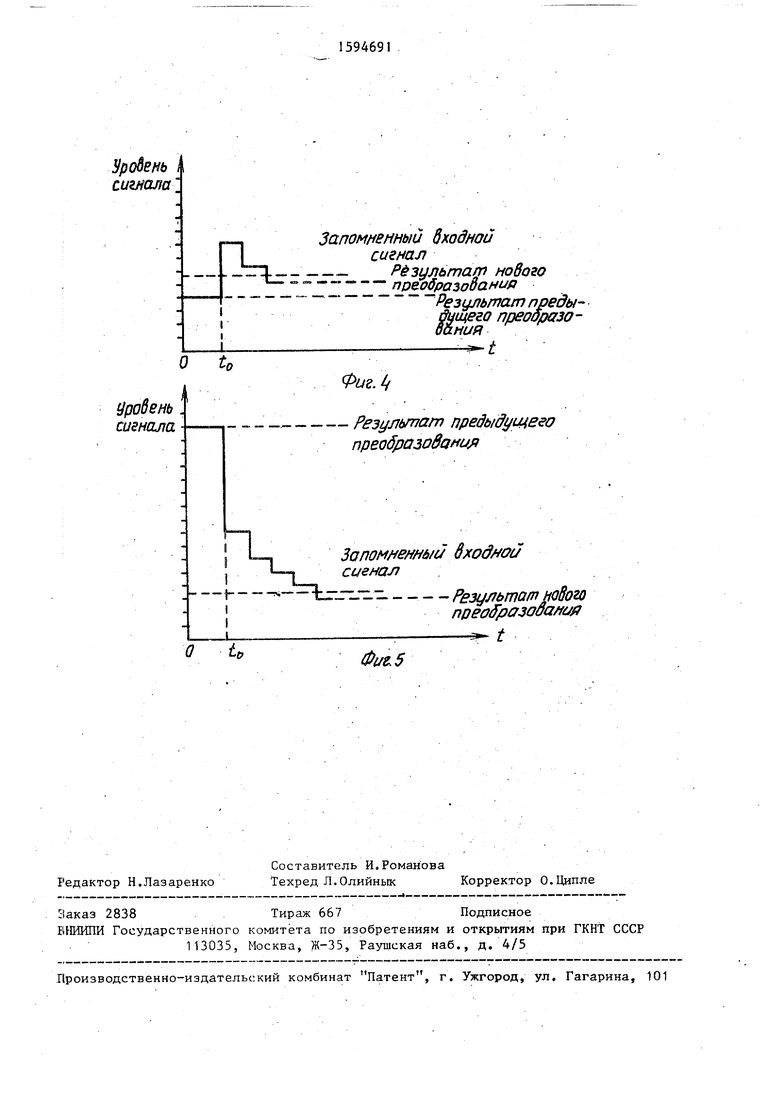

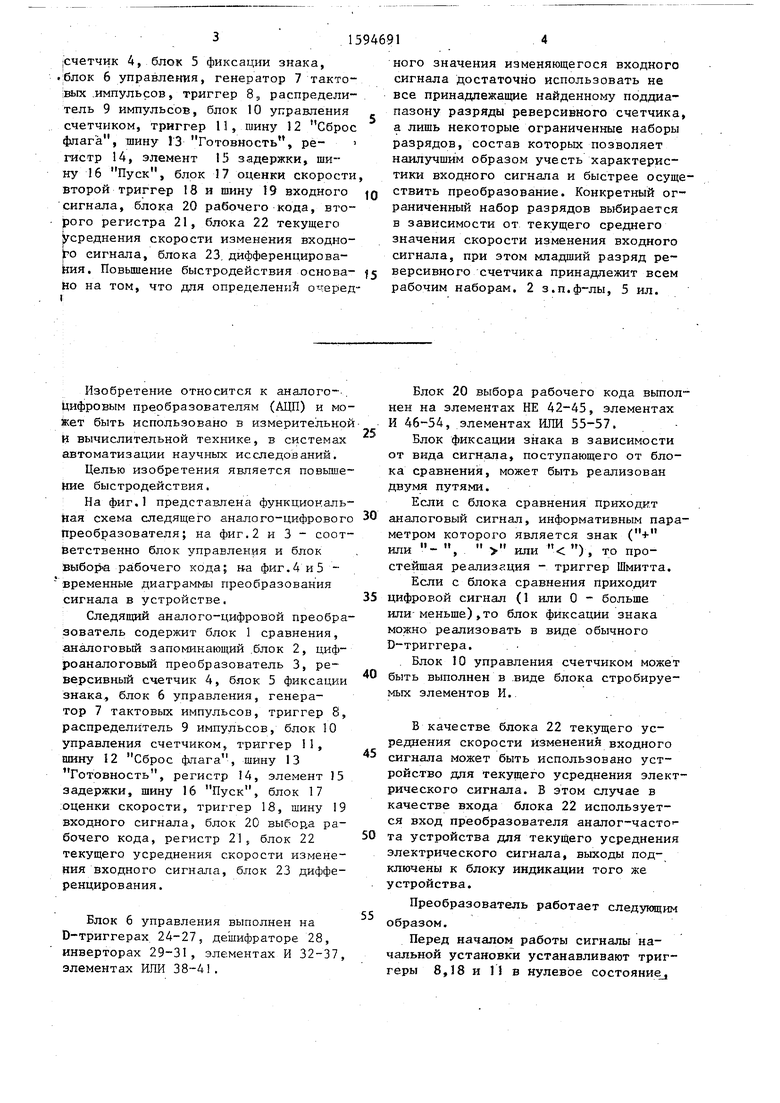

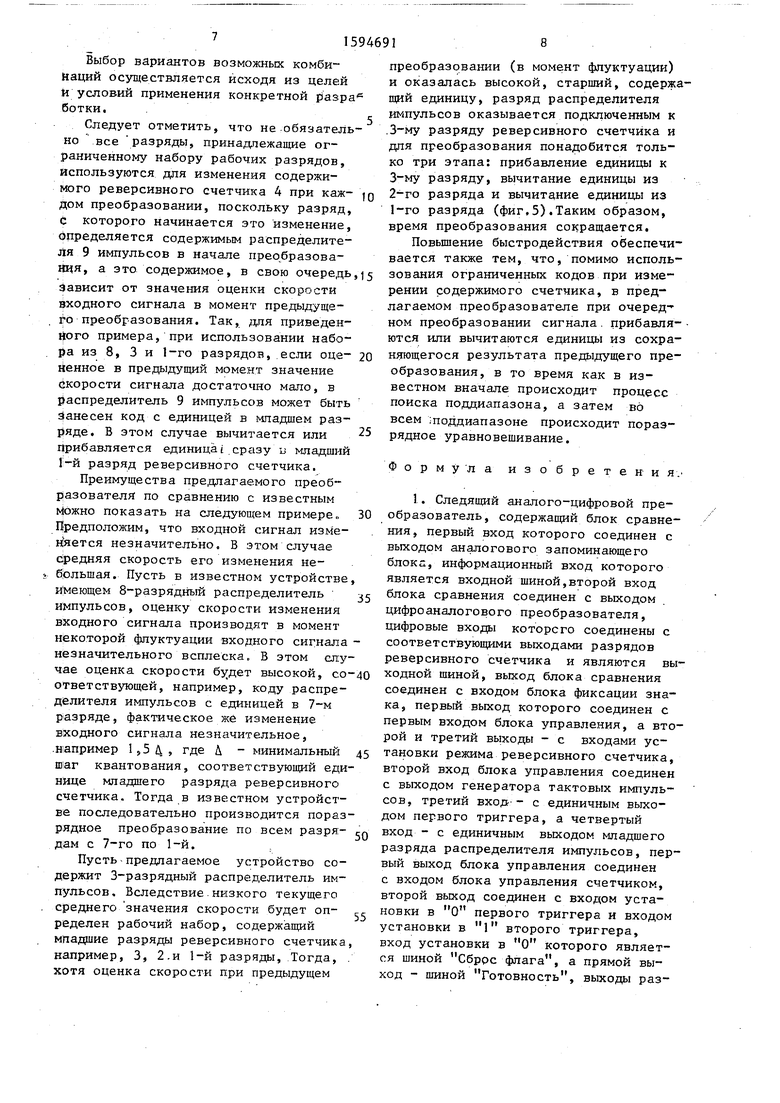

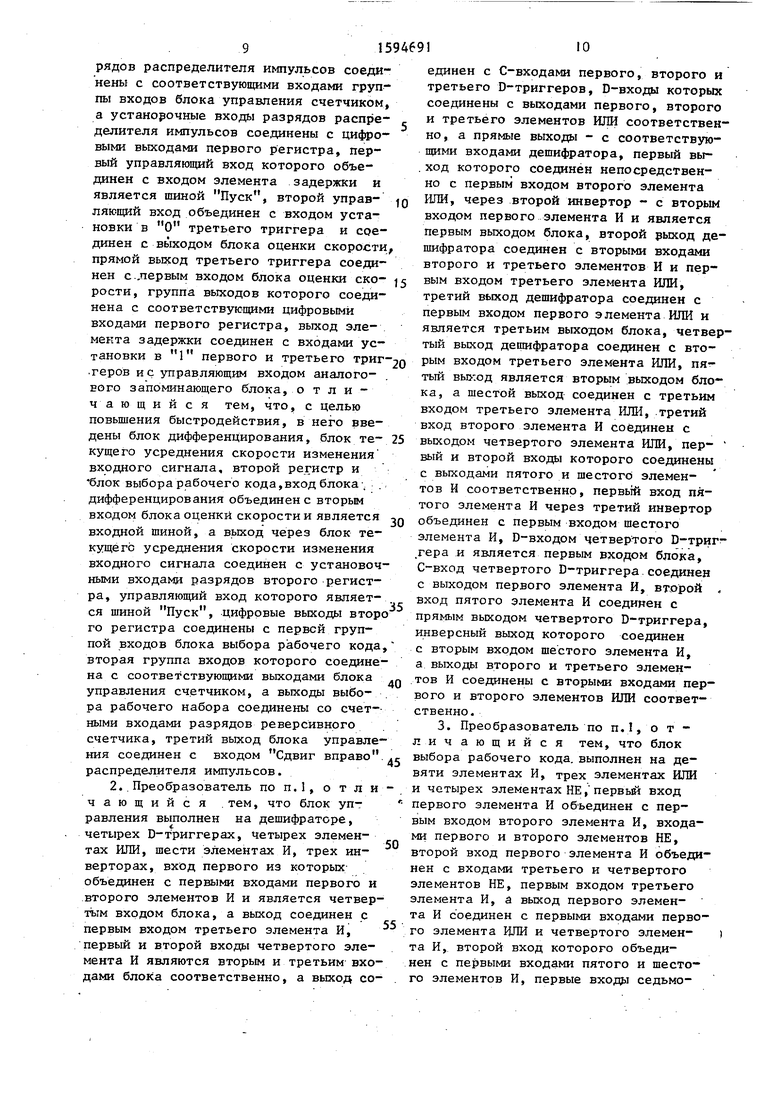

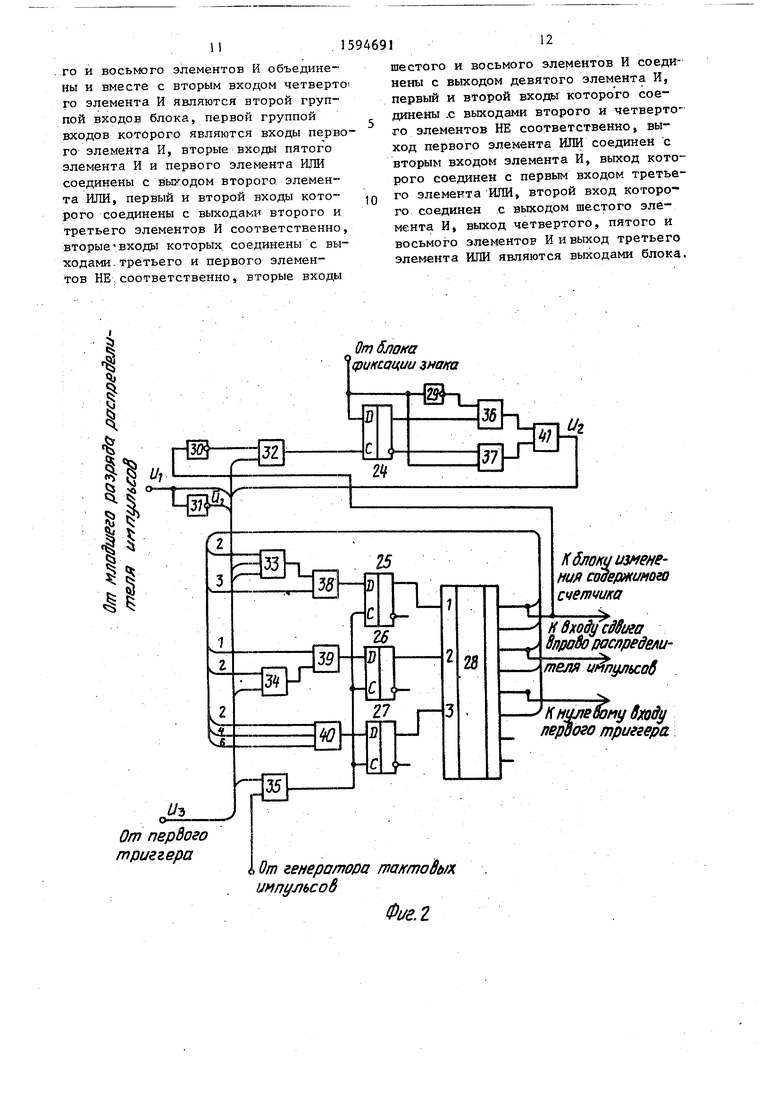

На фиг.1 представлена функциональая схема следящего аналого-цифрового 30 Преобразователя; на фиг.2 и 3 - соответственно блок управления и блок выборе рабочего кода; ка фиг.4и5 - временные диаграммы преобразования сигнала в устройстве.

Следящий аналого-цифровой преобразователь содержит блок 1 сравнения, аналоговый запоминающий .блок 2, циф- роаналоговьш преобразователь 3, реверсивный счетчик 4, блок 5 фиксации знака., блок 6 управления, генератор 7 тактовых импульсов, триггер 8, распределитель 9 импульсов, блок 10 управления счетчиком, триггер 1, шину 12 Сброс флага, шину 13 Готовность, регистр 14, элемент 15 задержки, шину 16 Пуск, блок 17 оценки скорости, триггер 18, шину 19 входного сигнала, ешок 20 выбор.а рабочего кода, регистр 21, блок 22 текущего усреднения скорости изменения входного сигнала, блок 23 дифференцирования.

40

45

50

Блок 6 управления выполнен на D-триггерах 24-27, дешифраторе 28, инверторах 29-31, элементах И 32-37, элементах ИЛИ 38-41.

5

5

0

0

5

0

5

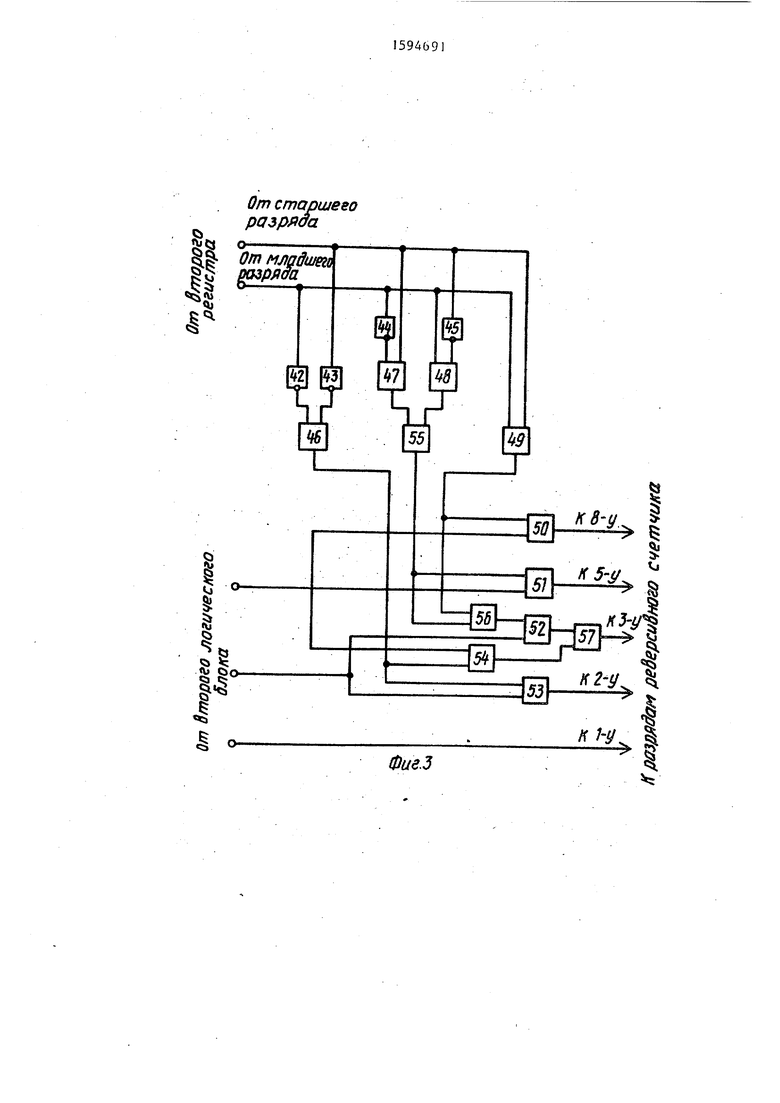

Блок 20 выбора рабочего кода вьтол- нен на элементах НЕ 42-45, элементах И 46-54, элементах ИЛИ 55-57,

Блок фиксации знака в зависимости от вида сигнала, поступающего от блока сравнения, может быть реализован двумя путями.

Если с блока сравнения приходит аналоговый сигнал, информативным параметром которого является знак (+ или - , или ) , то про- стейшая реализация - триггер Шмитта.

Если с блока сравнения приходит цифровой сигнал (1 или О - больше или-меньше),то блок фиксации знака можно реализовать в виде обычного D-триггера.

. Блок 10 управления счетчиком может быть выполнен в .виде блока стробируе- мых элементов И.

В качестве блока 22 текущего усреднения скорости изменения входного сигнала может быть использовано устройство для текущего усреднения электрического сигнала. В этом случае в качестве входа блока 22 используется вход преобразователя аналог-часто - та устройства для текущего усреднения электрического сигнала, выходы подключены к блоку индикации того же устройства.

Преобразователь работает следующим образом.

Перед началом работы сигналы начальной установки устанавливают триггеры 8,18 и II в нулевое состояние.

51

распределитель 9 импульсов - в любое состояние. В регистр 14 заносится код с единицей в одном из разрядов, в регистре 21 может находиться любой код. Цепи начальной установки не показаны. ,

С приходом сигнала Пуск производится переписывание содержимого регистра 14 в распределитель 9 импуль- сов. В регистре 21 запоминается код соответствующий сигналам, снимаемым с выхода блока 22, в начальный момент этот код может быть нулевым.

На выходе блока 23 дифференцирова- ния постоянно вырабатывается сигнал, соответствующий скорости изменения входного сигнала, в блоке 22 формируется код, соответствующий текущему . среднему значению скорости изменения входного сигнала (т.е. происходит скользящее усреднение скорости изменения входного сигнала за промежуток времени заданной длительности). По

сигналу Запуск, вырабатывающемуся н

ность.

ля 9 импульсов. Затем блок 6 управления осуществляет сдвиг вправо распределителя 9 импульсов, при условии, что младший разряд последнего не находится в состоянии 1. Снова происходит вычитание или добавление единицы в очередной разряд реверсивного счетчика 4 с последующим сдвигом, распределителя 9 импульсрв вправо. Рслц же единица находится в младщем разряде распределителя 9 импульсов, то блок 6 управления подает сигналы на первом выходе на изменение содержимого реверсивного счетчика 4 до момента чередования сигналов на выходе блока 5 фикcaцшi знака, после чего на третьем вь0:оде блока 6 управления появляется сигнал, устанавливающий в О триггер 8, прекращающий работу блока 6 управления, а также устанавливается в единичное состояние триггер 11, на единичном выходе которого появляется сигнал Готов

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900438A2 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Устройство аналого-цифрового преобразования | 1981 |

|

SU1012435A1 |

| Устройство для допускового контроля | 1980 |

|

SU898390A2 |

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1184090A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

Изобретение относится к измерительной и вычислительной технике, может быть использовано в системах автоматизации научных исследований. Повышение быстродействия достигается за счет введения в преобразователь, содержащий блок 1 сравнения, аналоговый запоминающий блок 2, цифроаналоговый преобразователь 3, реверсивный счетчик 4, блок 5 фиксации знака, блок 6 управления, генератор 7 тактовых импульсов, триггер 8, распределитель 9 импульсов, блок 10 управления счетчиком, триггер 11, шину 12 "Сброс флага", шину 13 "Готовность", регистр 14, элемент 15 задержки, шину 16 "Пуск", блок 17 оценки скорости, второй триггер 18 и шину 19 входного сигнала, блока 20 рабочего кода, второго регистра 21, блока 22 текущего усреднения скорости изменения входного сигнала, блока 23 дифференцирования. Повышение быстродействия основано на том, что для определения очередного значения изменяющегося входного сигнала достаточно использовать не все принадлежащие найденному поддиапазону разряды реверсивного счетчика, а лишь некоторые ограниченные наборы разрядов, состав которых позволяет наилучшим образом учесть характеристики входного сигнала и быстрее осуществить преобразование. Конкретный ограниченный набор разрядов выбирается в зависимости от текущего среднего значения скорости изменения входного сигнала, при этом младший разряд реверсивного счетчика принадлежит всем рабочим наборам. 2 з.п.ф-лы, 5 ил.

30

выходе элемента 15 задержки, аналоговый запоминающий блок 2 запомина ет текущее значение сигнала, триггеры 8 и 18 устанавливаются в единичное состояние, разрешая работу соответственно блока 6 управления и блока 17 оценки скоро.сти. После того кгк будет оценена скорость входного сигнала, по сигналу на выходе блока 17 оценки скорости в ре- гистр 14 заносится оцененное значение скорости (код с единицей в одном из разрядов), а также устанавливаетДпя перевода триггера j 1 в нулевое состояние используется шина 12 Сброс флага.

ся в о триггер 18, прекращая работу блока 17 оценки скорости.

Блок -20 выбора рабочего кода под-- ключает выходь блока 10 управления счетчиком к счетным входам разрядов реверсивного счетчика 4 в зависимосОсобенности использования ограниченных наборов разрядов для изменения содержимого реверсивного счетчика 4 можно проиллюстрировать следующим примером -(фиг.4). Пусть используется трехразрядный распределитель 9 импульсов, десятиразрядный реверсивный счетчик 4,, а код, соответствую- дий текущему среднему значению скорости изменения входного сигнала, 40 представлен двузначным двоичным числом, и для хранения его используется двухразрядный регистр 21 (т.е. оценка текущего среднего может быть представлена четырьмя уровнями: 2 4).

ти от кода, хранящегося в регистре 21, дз Очевидно, что при самом высоком уров- при этом счетный вход мпадшего раз- . не у оценки (т.е. 11) текущего сред- ряда реверсивного счетчика 4 всегда него наиболее выгодно использовать подключен к младшему разряду распреде- один из старших разрядов реверсивного дителя 9 импульсов. . счетчика 4, некоторый промежуточньй

В зависимости от режима реверсивно- 50 и .младший, например 8,3-и 1-й. Наго счетчика 4, устанавливаемого блоком 5 фиксации знака, блок 10 управления счетчиком ло сигналу из блока .6 управления вычитает или добавляет едичапьное приближение входного сигнала . может осуществляться с использованием 8-го разряда, а уточнение - с .использованием 3-го и затем 1-го. При средницу в разряд реверсивного счетчика 4, 55 них уровнях оценки текущего средне- . подключенный посредством блока 20 вы- го (102,012) наиболее эффективно бора рабочего кода к тому выходу бло- будет работать, например, набор из

5, З-и 1-го разрядов, при малой оценка 10, которому соответствует содержащий единицу разряд распределитеке - набор из 3, 2 и 1-го разрядов.

Дпя перевода триггера j 1 в нулевое состояние используется шина 12 Сброс флага.

Особенности использования ограниченных наборов разрядов для изменения содержимого реверсивного счетчика 4 можно проиллюстрировать следующим примером -(фиг.4). Пусть используется трехразрядный распределитель 9 импульсов, десятиразрядный реверсивный счетчик 4,, а код, соответствую- дий текущему среднему значению скорости изменения входного сигнала, представлен двузначным двоичным числом, и для хранения его используется двухразрядный регистр 21 (т.е. оценка текущего среднего может быть представлена четырьмя уровнями: 2 4).

и .младший, например 8,3-и 1-й. Начапьное приближение входного сигнала . может осуществляться с использованием 8-го разряда, а уточнение - с .использованием 3-го и затем 1-го. При сред5, З-и 1-го разрядов, при малой оцен

ке - набор из 3, 2 и 1-го разрядов.

10

Выбор вариантов возмоясных комби- Наций осуществляется исходя из целей и условий применения конкретной разра ботки.

Следует отметить, что не-обязательно все разряды, принадлежащие ограниченному набору рабочих разрядов, используются для изменения содержимого реверсивного счетчика 4 при каждом преобразовании, поскольку разряд, С которого начинается это изменение, определяется содержимым распределителя 9 импульсов в начале преобразования, а это содержимое, в свою очередь,t5 Зависит от значения оценки скорости входного сигнала в момент предыдуще- , ifo преобразования. Так, дпя приведен- Його примера, при использовании набора из 8, 3 и 1-го разрядов, если оце- 20 йенное в предыдущий момент значение скорости сигнала достаточно мало, в распределитель 9 импульсов может быть Занесен код с единицей в lvlлaдшeм разряде. В этом случае вычитается или Прибавляется единица сразу D младший 1-й разряд реверсивного счетчика.

Преимущества пре,цлагаемого преобразователя по сравнению с известным Можно показать на следующем примере., Предположим, что входной сигнал измеряется незначительно. В этом случае Ьредняя скорость его изменения не- ; больщая. Пусть в известном устройстве, иЪ1еющем 8-разрядный распределитель импульсов, оценку скорости изменения входного сигнала производят в момент некоторой флуктуации входного сигнахЕа - незначительного всплеска, В этом сл:у- чае оценка скорости будет высокой, с.о-40 ответствующей, например, коду распределителя импульсов с единицей в 7-м разряде, фактическое же изменение входного сигнала незначительное, .например IjSi, где Д - минимальный 45 ffiiar квантования, соответствующий единице младшего разряда реверсивного счетчика. Тогда в известном устройстве последовательно производится пораз25

30

35

преобразовании (в момент флуктуации и оказалась высокой, старший, содер шрй единицу, разряд распределителя импульсов оказывается подключенным .З-МУ разряду реверсивного счетчика для преобразования понадобится толь ко три этапа: прибавление единицы к З-МУ разряду, вычитание единицы из 2-го разряда и вычитание единицы из 1-го разряда (фиг.5).Таким образом, время преобразования сокращается.

Повышение быстродействия обеспеч вается также тем, что, помимо испол зования ограниченных кодов при изме рении содержимого счетчика, в предлагаемом преобразователе при очеред ном преобразовании сигнала. прибавл ются или вычитаются единицы из сохр няющегося результата предыдущего пр образования, в то время как в известном вначале происходит процесс поиска поддиапазона, а затем во всем поддиапазоне происходит пораз рядное уравновешивание.

Форму Л а изобрете

н и

f- ы, -ц 1 пс: 1 Dlrl

рядное преобразование по всем разря- JQ вход - с единичным выходом младшего

дам с 7-го по 1-й.

Пусть предлагаемое устройство содержит 3-разрядный распределитель импульсов. Вследствие.низкого текущего среднего значения скорости будет определен рабочий набор, содержащий младшие разряды реверсивного счетчика, например, 3, 2.и 1-й разряды. Тогда, . хотя оценка скорости при предыдущем

разряда распределителя импульсов, пе вый выход блока управления соединен с входом блока управления счетчиком, второй выход соединен с входом уста- 55 новки в О первого триггера и входом установки в 1 второго триггера, вход установки в О которого является шиной Сброс флага, а прямой выход - шиной Готовность, выходы раз

преобразовании (в момент флуктуации) и оказалась высокой, старший, содержа- шрй единицу, разряд распределителя импульсов оказывается подключенным к .З-МУ разряду реверсивного счетчика и для преобразования понадобится только три этапа: прибавление единицы к З-МУ разряду, вычитание единицы из 2-го разряда и вычитание единицы из 1-го разряда (фиг.5).Таким образом, время преобразования сокращается.

Повышение быстродействия обеспечивается также тем, что, помимо использования ограниченных кодов при измерении содержимого счетчика, в предлагаемом преобразователе при очеред ном преобразовании сигнала. прибавля- ются или вычитаются единицы из сохраняющегося результата предыдущего преобразования, в то время как в известном вначале происходит процесс поиска поддиапазона, а затем во всем поддиапазоне происходит поразрядное уравновешивание.

Форму Л а изобрете

н и я.

f- ы, -ц 1 пс: 1 Dlrl

вход - с единичным выходом младшего

разряда распределителя импульсов, первый выход блока управления соединен с входом блока управления счетчиком, второй выход соединен с входом уста- новки в О первого триггера и входом установки в 1 второго триггера, вход установки в О которого является шиной Сброс флага, а прямой выход - шиной Готовность, выходы раз

рядов распределителя импульсов соединены с соответствующими входами группы входов блока управления счетчиком а установочные входы разрядов распределителя импульсов соединены с цифровыми выходами первого регистра, первый управляющий вход которого объединен с входом элемента задержки и является шиной Пуск, второй управляющий вход объединен с входом установки в О третьего триггера и соединен с выходом блока оценки скорости прямой выход третьего триггера соединен с-.первым входом блока оценки ско- рости, группа выходов которого соединена с соответствующими цифровыми входами первого регистра, выход элемента задержки соединен с входами установки в 1 первого и третьего триг геров и с управляющим входом аналогового запоминающего блока, о т л и - чающийся тем, что, с целью повьшения быстродействия, в него введены блок дифференцирования, блок те- кущего усреднения скорости изменения входного сигнала, второй регистр и блок выбора рабочего кода,вход блока-. . дифференцирования объединен с вторым входом блока оценки скорости и является входной шиной, а выход через блок текущего усреднения скорости изменения входного сигнала соединен с установочными входами разрядов второго регистра, управляющий вход которого являет- ся шиной Пуск, цифровые выходы второ го регистра соединены с первой группой входов блока выбора рабочего кода вторая группа входов которого соединена с соответствующими выходами блока управления счетчиком, а выходы выбора рабочего набора соединены со счет-- ными входами разрядов реверсивного счетчика, третий выход блока управления соединен с входом Сдвиг вправо распределителя импульсов.

я .тем, что блок упг на дешифраторе.

ч а ю щ и и с равления выполнен

четырех П-триггерах, четырех элементах ИЛИ, шести элементах И, трех инверторах, вход первого из которых объединен с первыми входами первого и второго элементов И и является четвер- тьтм входом блока, а выход соединен с первым входом третьего элемента И, первый и второй входы четвертого элемента И являются вторым и третьим входами блока соответственно, а выход со10

, с п 25 .

30

0

5

0

единен с С-входами первого, второго и третьего D-триггеров, D-входы которых соединены с выходами первого, второго и третьего элементов ИЛИ соответственно, а прямые выходы - с соответствзто- щими входами дешифратора, первый выход которого соединен непосредственно с первым входом второго элемента ИЛИ, через второй инвертор - с вторым входом первого элемента И и является первым выходом блока, второй рыход дешифратора соединен с вторыми входами второго и третьего элементов И и первым входом третьего элемента ШШ, третий выход дешифратора соединен с первым входом первого элемента ШШ и является третьим выходом блока, четвертый выход дешифратора соединен с вторым входом третьего элемента ШШ, пятый является вторым выходом блока, а шестой выход соединен с третьим входом третьего элемента ИЛИ, .третий вход второго элемента И соединен с выходом четвертого элемента ИЛИ, пер- вый и второй входы которого соединены с выходами пятого и шестого элементов И соответственно, первь1й вход пятого элемента И через третий инвертор объединен с первым входом шестого элемента И, D-входом четвертого D-триг- .гера и является первым входом блока, четвертого D-триггера-соединен с выходом первого элемента И, второй . вход пятого элемента И соединен с прямым выходом четвертого D-триггера, инверсный выход которого соединен с вторым входом шестого элемента И, а выходы второго и третьего элементов И соединены с вторыми входами первого и второго элементов ИЛИ соответственно.

|| |1

II

От генератора maifmoBb/x. импульсоб

Фиг.2

шестого и восьмого элементов И соединены с выходом девятого элемента И, первый и второй входы которого соединены .с выходами второго и четвертого элементов НЕ соответственно, выход первого элемента ИЛИ соединен с вторым входом элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, выход четвертого, пятого и восьмого элементов И и выход третьего элемента ИЛИ являются выходами блока.

От 5лока сриксации знака

иг

WMySxoffy

От старшеео pci3pflaa

Продень cuwana .

Запомненный бмдной сигнал

Результат нового

- - - поеобраъооанир

Результат пре &4щего преойра вания

I

Фиг. li

Результат предыдущеео

преобразовамил

3onoMffeH A/u в)( одной сиенал

раъооанир

Результат преды- &4щего преойразо- вания

- - Результагл HoSow nDeofpG3oda c/fl

t

Фиг. 5

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-09-23—Публикация

1988-10-17—Подача