вход блока исключения импульса являются саответственно вторым входом

и входом опорной частоты умножителя частоты сле/товаиия импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1985 |

|

SU1279046A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

| Цифровой умножитель частоты | 1978 |

|

SU803100A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Умножитель частоты следования им-пульСОВ | 1979 |

|

SU839031A1 |

| Цифровой умножитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU824440A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Умножитель частоты следования импульсов (его варианты) | 1983 |

|

SU1120483A1 |

| Цифровой умножитель частоты | 1978 |

|

SU790181A1 |

1. УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий управляемый делитель частоты, последовательно соединенные первый делитель частоты и счетчик, а также формирователь импульсов, первый выход которого соединен с установочным входом счетчика, при этом первый вход формирователя импульсов объединен с входом первого делителя частоты и является входом опорной частоты умножителя частоты следования импульсов, второй вход формирователя импульсов является входом сигнала умножаемой частоты умножителя частоты следования импульсов, о т л ичающийся тем, что, с целью повьшения точности умножения, в него введены блок коррекции опорной частоты, блок памяти,второй делитель частоты и элемент совпадения, входы которого соединены с соответствующими выходами второго делителя частоты, первый вход блока коррекции опорной частоты соединен с входом первого делителя частоты, синхронизируюпщй вход элемента совпадения соединен с входом второго делителя частоты, вторым входом блока коррекции опорной частоты и с выходом управляемого делителя частоты, а выход элемента совпадения соединен с счетным входом блока памяти, выход второго делителя частоты соединен с входом записи блока коррекции опорной частоты, информационный вход которого соединен с первой группой информационных выходов блока памяти, а выход - с входом управляемого делителя частоты, первый выход формирователя импульсов соединен с установочным входом первого делителя частоты, второй выход формирователя импульсов соединен с входом записи с блока памяти, первая группа информа ционных входов которого соединена ел с информационным выходом первого делителя частоты, вторая группа информационных входов которого соединена с выходом счетчика, вторая группа информационных выходов блока памяти соединена с информационным входом управляемого делителя частоты. 2. Умножитель по п, 1, отличающийся тем, что.блок кор-. эо рекции опорной частоты выполнен в D1 виде последовательно соединенных вычитающего счетчика импульсов, CD элемента ИЛИ, элемента совпадения и блока исключения импульса, при этом группа информационных входов вычитающего счетчика импульсов является информационным входом блока коррекции, опорной частоты, счетный вход вычитающего счетчика импульсов соединен с выходом элемента совпадения, вход записи вычитающего счетчика импульсов является входом записи блока коррекции опорной частоты, второй вход элемента совпадения и опорный

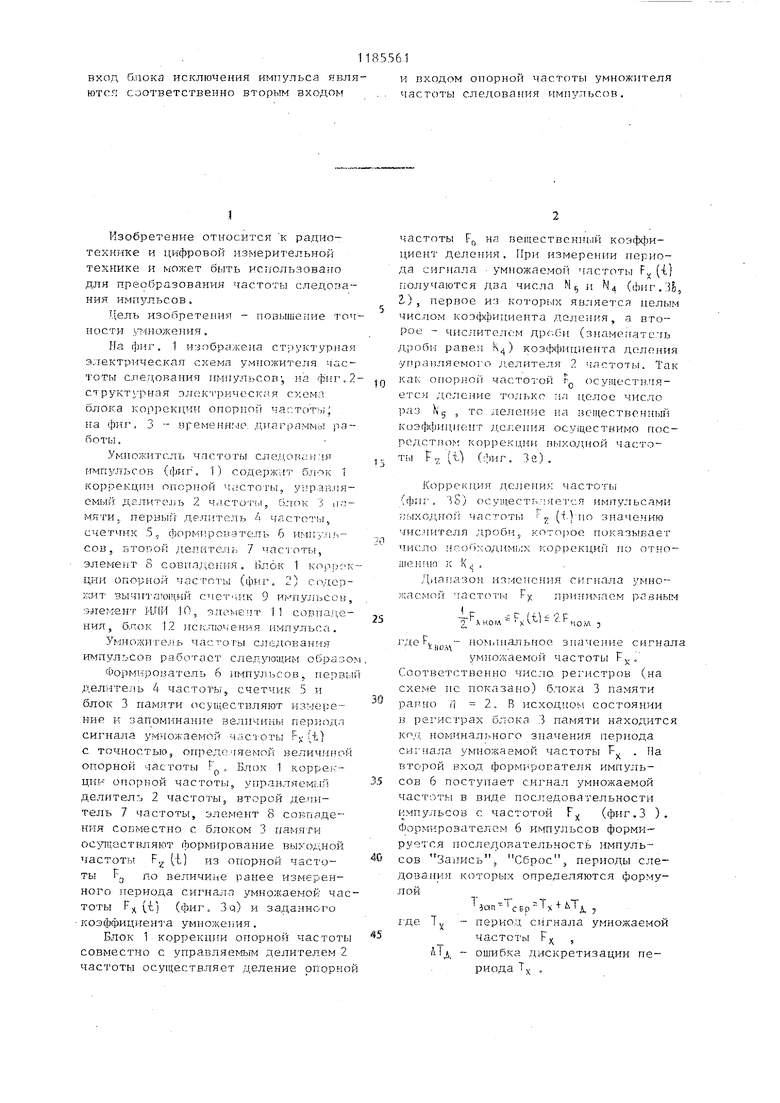

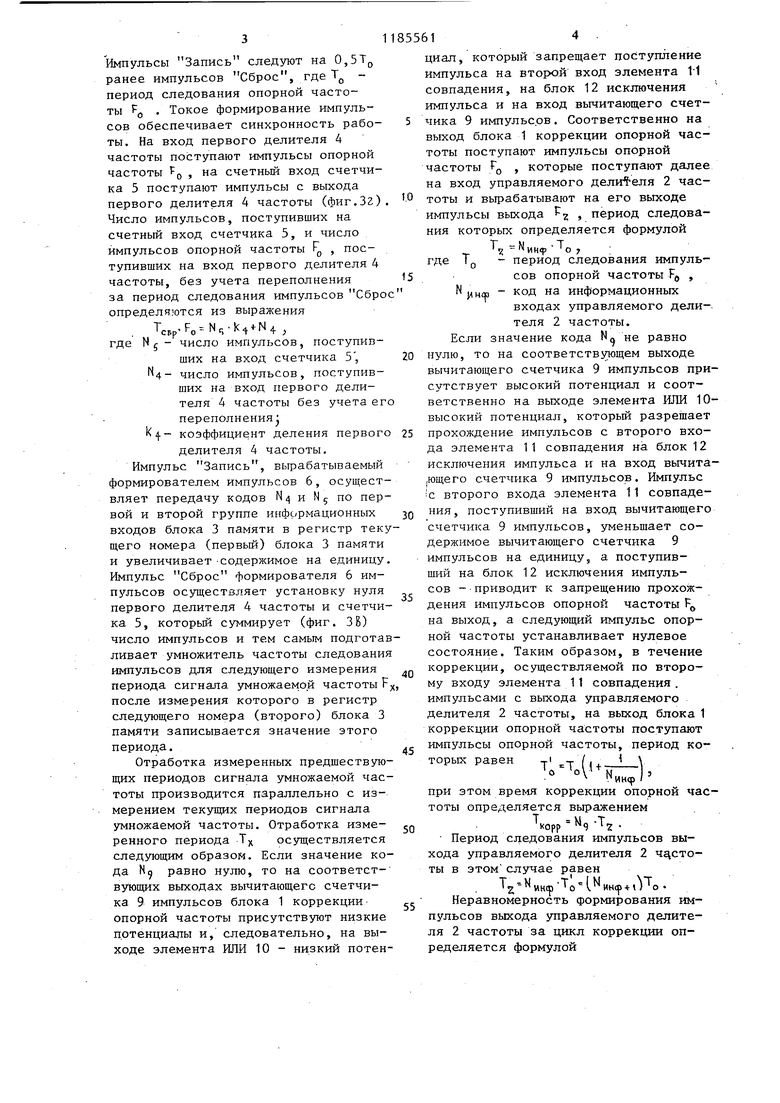

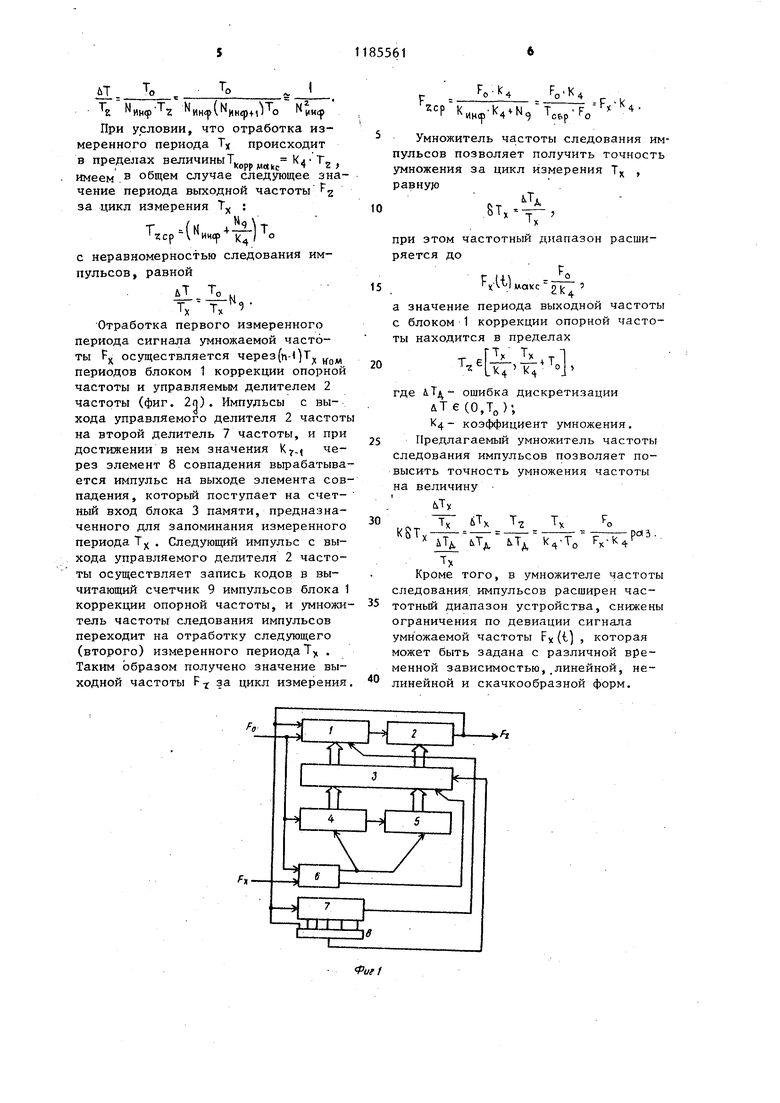

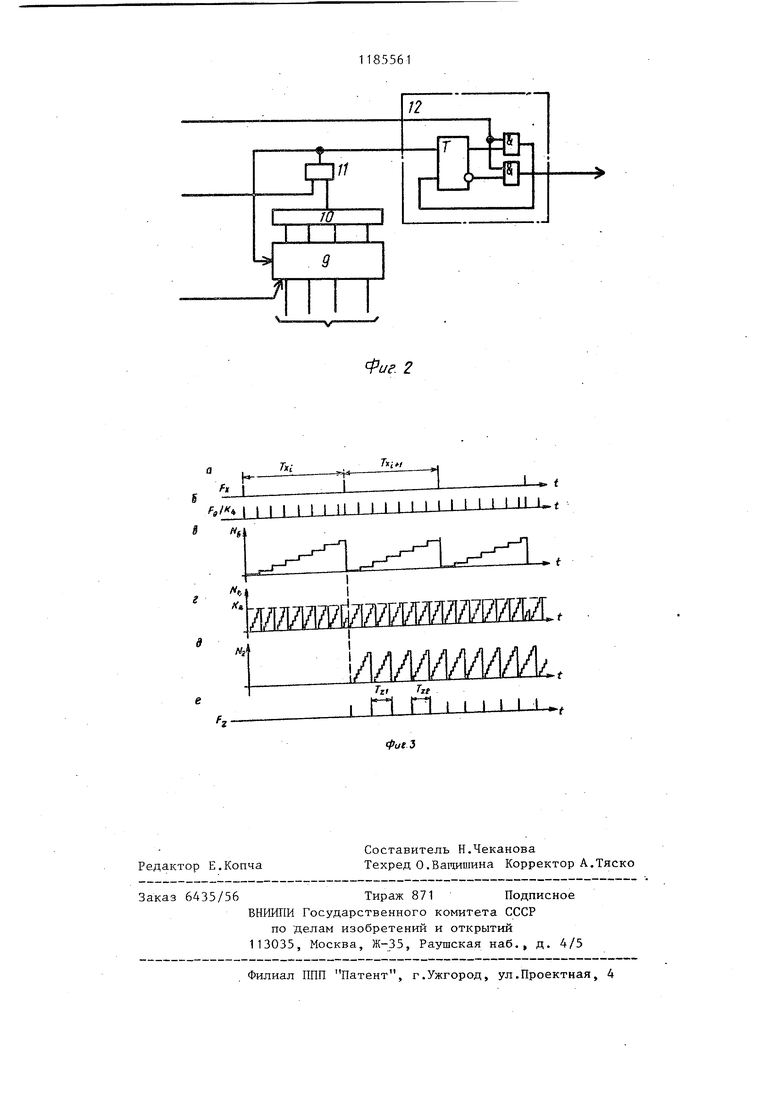

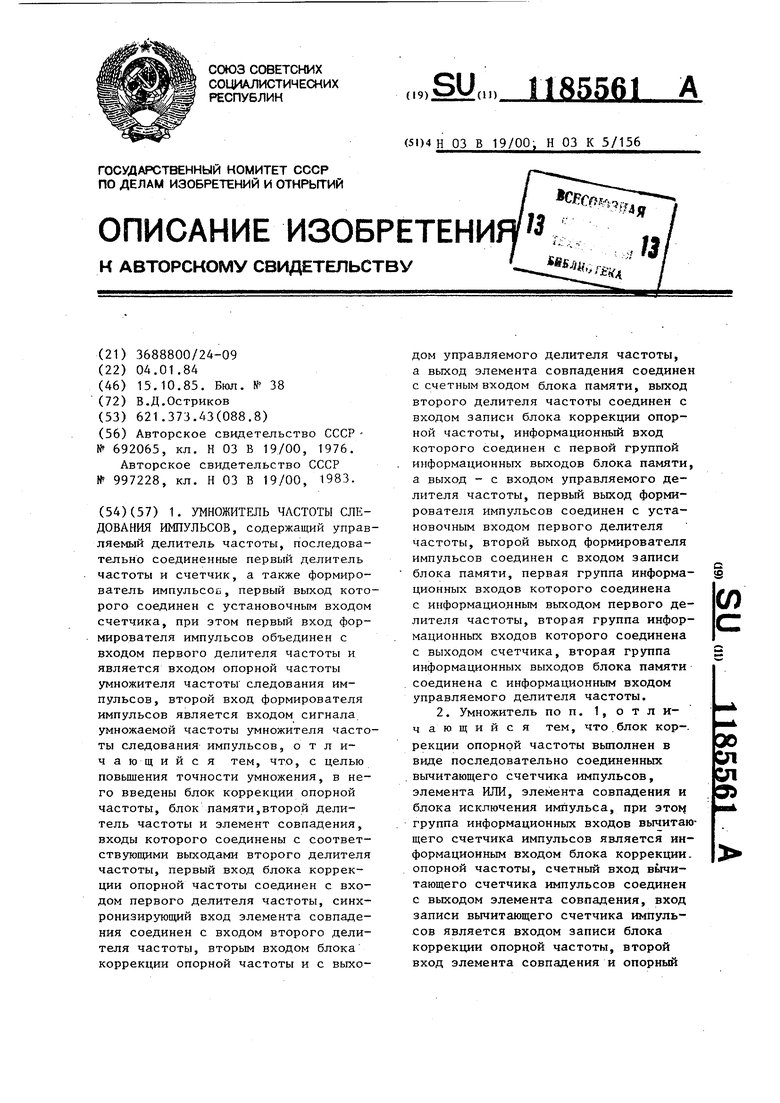

Изобретение относится к радиотехнике и цифровой измерительной технике и может быть использовано для преобразован 1Я частоты следозания импзшьсов. Цель изобретения - повышение точ ности .утлножения. На фиг. 1 изпбр;)жеиа структурная э..тектрнческая схема умножителя частоты следования импульсов.. на фиг.2 структурная злектрическ.чя схема блока корректти - onopHoii частотьц на фиг. 3 - вгеменнг.1е. Д1таграмма работы. Умножитель частоты следог-и; i-j :JH г-рчпульсов (фиг, 1) содержит б, 1 коррекции опорной частоты. у;грав.1 яемый дглитй.1)ь 2 частоты, блок j ii.;мяти.. иервьпг делитель А частоты счетчик 5„ формирователь 6 импульсов. ВТОРОЙ делителг 7 частоты, элемент 8 совпадения. Нлок 1 KopirvK ции опорной частоты (. 2) со,церл;ит вычитпчщяй счет;ик 9 импульсон, элемент И.Г(И 10, злемеит 11 совнат ениуЧ, блок 12 иcI лю ieния импульса. Умножитель ч ас о ты Сичедовання импульсов работает следуюатим образо Формирователь 6 импульсов. перзы делитель 4 частоты , счетчик 5 и блок 3 памяти осуществляют иЗ:-;ерение и запоминание зeли гинь сигнала умножаемой частоть Р.; ft) с точностью, oпpeдeляe oй величиной опорной частоты Блок 1 коррекции опорной частоты, управляемый делитель 2 частоты, второй делитель 7 частоты, элемент 8 совпадения coBivsecTBO с блоком 3 цамят1-1 ос Т1 ествляют формирование выходной частоты F, (i) из опорной частоты Fg по величине ранее измеренного периода сигнала умно;каемой час тоты 1х (t) (фиг. 3q) и заданного коэффициента умноже1шя. Блок 1 коррекции опорной частоты совместно с управляемым де:тителем 2 частоты осуществляет деление опорно частоты Г-д ня веществен ый коэффициe т деления. измерении периода сигнала умножаемой частоты Р„ (i) получаются два числа М и N4 (Фиг.ЗЬ, 2,) , первое из ко1opt-.ix является целым числом коэффициента деле(И1Я, а второе числтителсьм дрг.би (знамеггате:гь дроби равем К) коэффициегтта деления упраиляемогО л,елите;ля 2 частоты. Так как огизрной частотой t- осуществдшется деление только на целое число раз hiij , то деление на вещественный Коэффициент деления осуществимо поередст1зом корреки,ии выход,иой частоты F.- (i (фиг. Зе) . Коррекция деления частоты (фиг. iS) осущесть-яется импульсами ;ыход го11 частоты j. (1.)ч1о значе}1Ига -{ис.чителя дроби,. Ko-rcipoe по сазывает число нeof)..:x )-:ор|)екций по отноiiieHHin )С К | . 1.Р ...; с (+1 F 2 X Н01Л X - но ,vi 3 гдеР,| - номлнаттьное значение сигнала ул ножаемой частоты Г,,. Соответственно числа рег1.1стров (на схеме не показано) блока 3 памяти ратию П 2., В исходноь состоя1и-1и . регртстрах блока .3 памяти находится ко.а, ном.инального значения периода сигнала умножаемой частоты F, . На второй вход формирователя импульсов 6 поступает сигнал умножаемой частоты в виде последовательности импульсов с частотой Р, (фиг.З ). Формирователем 6 импульсов формируется последовательность импульсов Запись, Сброс, периоды следования которых определяются формулой. , где TV - период сигнала умнолсаемой частоты Fy . ( ошиб.ка дискретизации периода Tj, . Импульсы Запись следуют на 0,57 ранее импульсов Сброс, где Т период следования опорной частоты РО . Токое формирование импульсов обеспечивает синхронность работы. На вход первого делителя 4 частоты поступают и тульсы опорной частоты РО , на счетный вход счетчика 5 поступают импульсы с выхода первого делителя 4 частоты (фиг.Зг) Число импульсов, поступивших на счетный вход счетчика 5, и число импульсов опорной частоты 1- , поступивших на вход первого делителя 4 частоты, без учета переполнения за период следования импульсов Сбро определя;отся из выражения где N5 - число импульсов, поступивших на вход счетчика 5, число импульсов, поступивших на вход первого делителя 4 частоты без учета ег переполнения коэффициент деления первого делителя 4 частоты. Импульс Запись, вырабатываемый формирователем импульсов 6, осуществляет передачу кодов N и N по первой и второй группе информационных входов блока 3 памяти в регистр теку щего номера (первый) блока 3 памяти и увеличивает -содержимое на единицу Импульс Сброс формирователя 6 импульсов осуществляет установку нуля первого делителя 4 частоты и счетчика 5, который суммирует (фиг. ЗВ) число импульсов и тем самым подготав ливает умножитель частоты следования импульсов для следующего измерения периода сигнала умножаемой частоты F после измерения которого в регистр следующего номера (второго) блока 3 памяти записывается значение этого периода. Отработка измеренных предшествующих периодов сигнала умножаемой частоты производится параллельно с измерением текущих периодов сигнала умножаемой частоты. Отработка измеречного периода Т осуществляется следующим образом. Если значение кода Kg равно нулю, то на соответствующих выходах вычитающего счетчика 9 импульсов блока 1 коррекции опорной частоты присутствуют низкие потенциалы и, следовательно, на выходе элемента ИЛИ 10 - низкий потенциал, который запрещает поступление импульса на второй вход элемента 11 совпадения, на блок 12 исключения импульса и на вход вычитающего счетчика 9 импульсов. Соответственно на выход блока 1 коррекции опорной частоты поступают импульсы опорной частоты FQ которые поступают далее на вход управляемого делителя 2 частоты и вырабатывают на его выходе импульсы выхода f , период следования которых определяется формулой - о 7 - период следования импульсов опорной частоты F , j/tHO) код на информационных входах управляемого делителя 2 частоты. Если значение кода N(j не равно нулю, то на соответствующем выходе вычитающего счетчика 9 импульсов присутствует высокий потенциал и соответственно на выходе элемента ИЛИ 10высокий потенциал, которьй разрешает прохождение импульсов с второго входа элемента 11 совпадения на блок 12 исключения импульса и на вход вычита,ющего счетчика 9 импульсов. Импульс с второго входа элемента 11 совпадения, поступивший на вход вычитающего счетчика 9 импульсов, уменьшает содержимое вычитающего счетчика 9 импульсов на единицу, а поступивший на блок 12 исключения импульсов - приводит к запрещению прохождения импульсов опорной частоты F на выход, а следующий импульс опорной частоты устанавливает нулевое состояние. Таким образом, в течение коррекции, осуществляемой по второму входу элемента 11 совпадения . импульсами с выхода управляемого делителя 2 частоты, на выход блока 1 коррекции опорной частоты поступают импульсы опорной частоты, период которых равен 1 -, у °(.., при этом время коррекции опорной частоты определяется выражением корр 9 -Т Период следования импульсов выхода управляемого делителя 2 ты в этомслучае равен Т инср TO Ч инср 4 . Неравномерность формирования импульсов выхода управляемого делителя 2 частоты за цикл коррекции определяется формулой ( Mwai+i o ИНф г MHf х инфц) При условии, что отработка измеренного периода Т, происходит в пределах величиныТ рр ,1,, К4- Г , имеем в общем случае следующее значение периода выходной частоты z за цикл измерения Т : г Гм Ут гсрП иис 1 7) о с неравномерностью следования импульсов, равной дТ То Отработка первого измеренного периода сигнала умножаемой частоты FV осуществляется через(п-ОТд периодов блоком 1 коррекции опорной частоты и управляемым делителем 2 частоты (фиг. 2п). Импульсы с выхода управляемого делителя 2 частот на второй делитель 7 частоты, и при достижении в нем значения ерез элемент 8 совпадения вырабатыва ется импульс на выходе элемента сов падения, который поступает на счетный вход блока 3 памяти, предназначенного для запоминания измеренного периода Т , Следующий импульс с выхода управляемого делителя 2 частоты осуществляет запись кодов в вычитающий счетчик 9 импульсов блока коррекции опорной частоты, и умнож тель частоты следования импульсов переходит на отработку следующего (второго) измеренного периода Т, . Таким образом получено значение вы ходной частоты F за цикл измерени .-i K, сьр Умножитель частоты следования имльсов позволяет получить точность ножения за цикл измерения Т , внук) }. gT -:f- J и этом частотный диапазон расшияется до г |1 - x Va c-2k4значение периода выходной частоты блоком 1 коррекции опорной частоы находится в пределах -4v де лТд- ошибка дискретизации лТе(0,Т,); К4- коэффициент умножения. Предлагаемый умножитель частоты ледования импульсов позволяет поысить точность умножения частоты на величину JjL. iLi -II Il - f -poi3 .Чт,k.T/г, TX Кроме того, в умножителе частоты следования, импульсов расширен частотный диапазон устройства, снижены ограничения по девиации сигнала умножаемой частоты Fy(t), которая может быть задана с различной временной зависимостью,.линейной, нелинейной и скачкообразной форм.

ue. 2

| Дискретный умножитель частоты повторения импульсов | 1977 |

|

SU692065A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой умножитель частоты следования периодических импульсов | 1981 |

|

SU997228A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-10-15—Публикация

1984-01-04—Подача