( 5) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU920716A2 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU926666A2 |

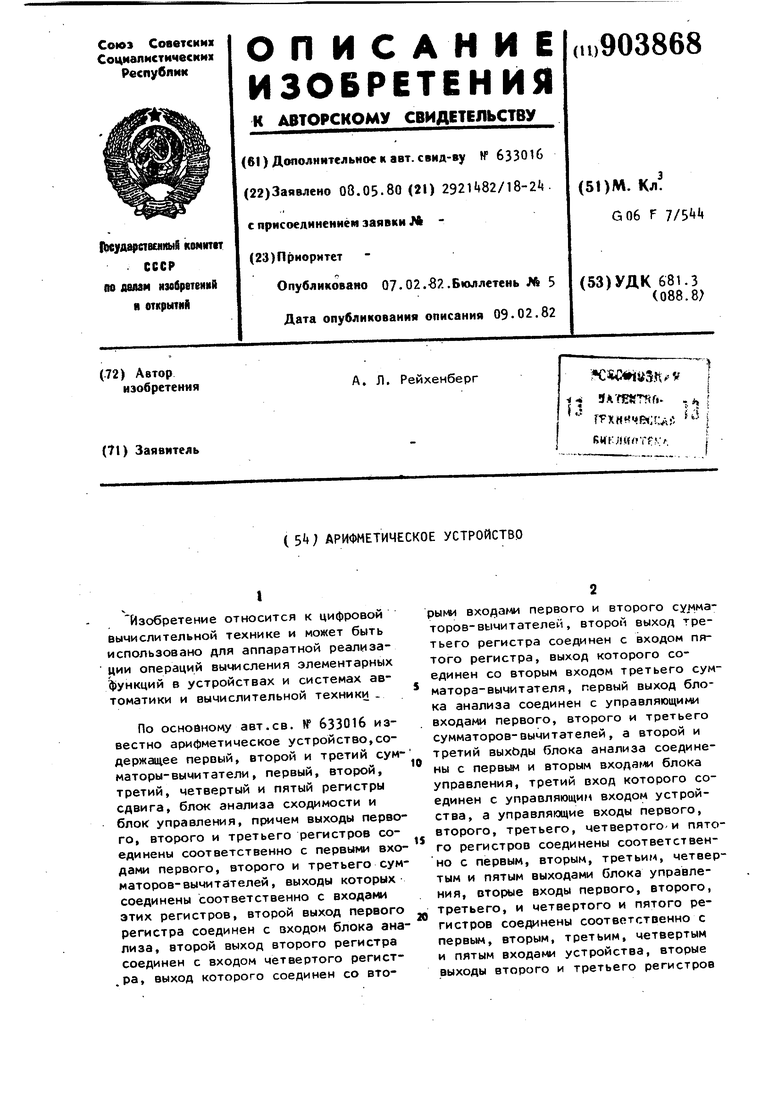

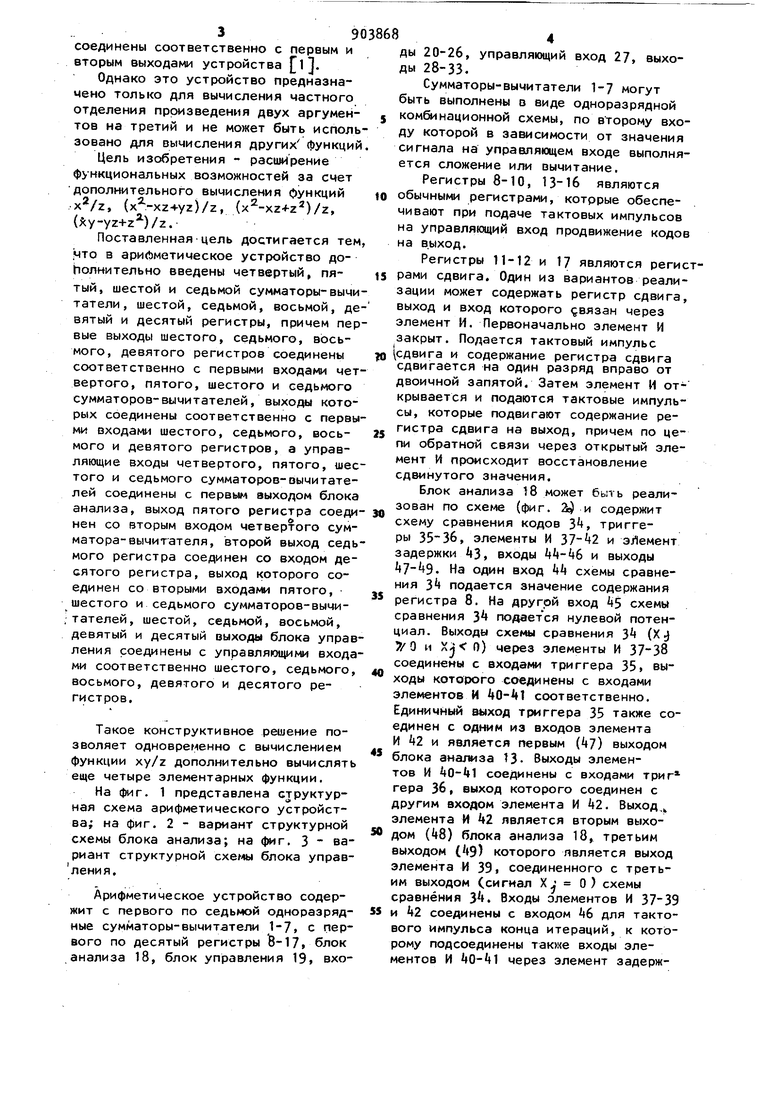

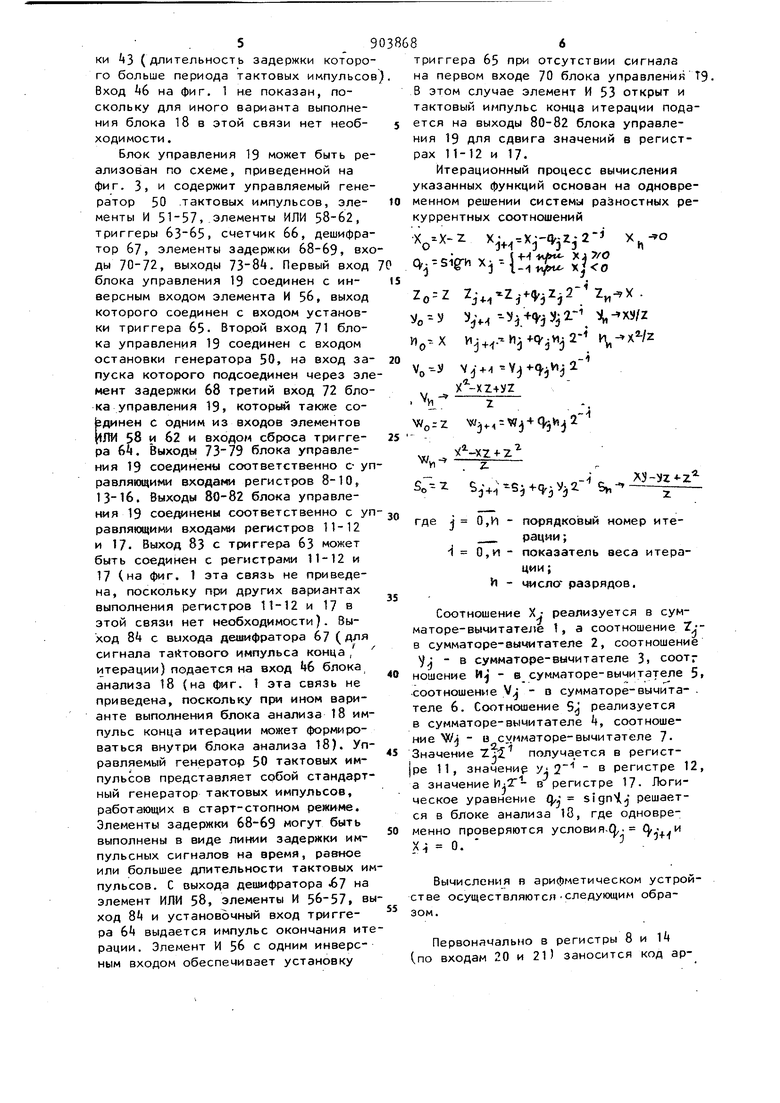

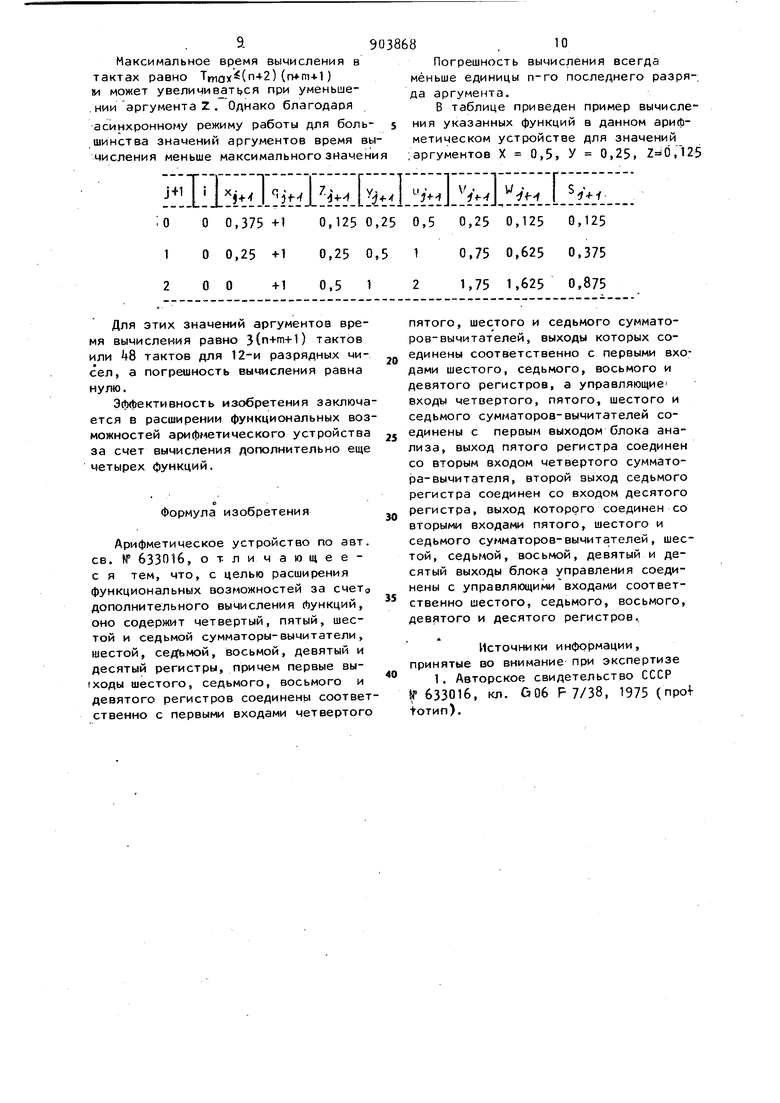

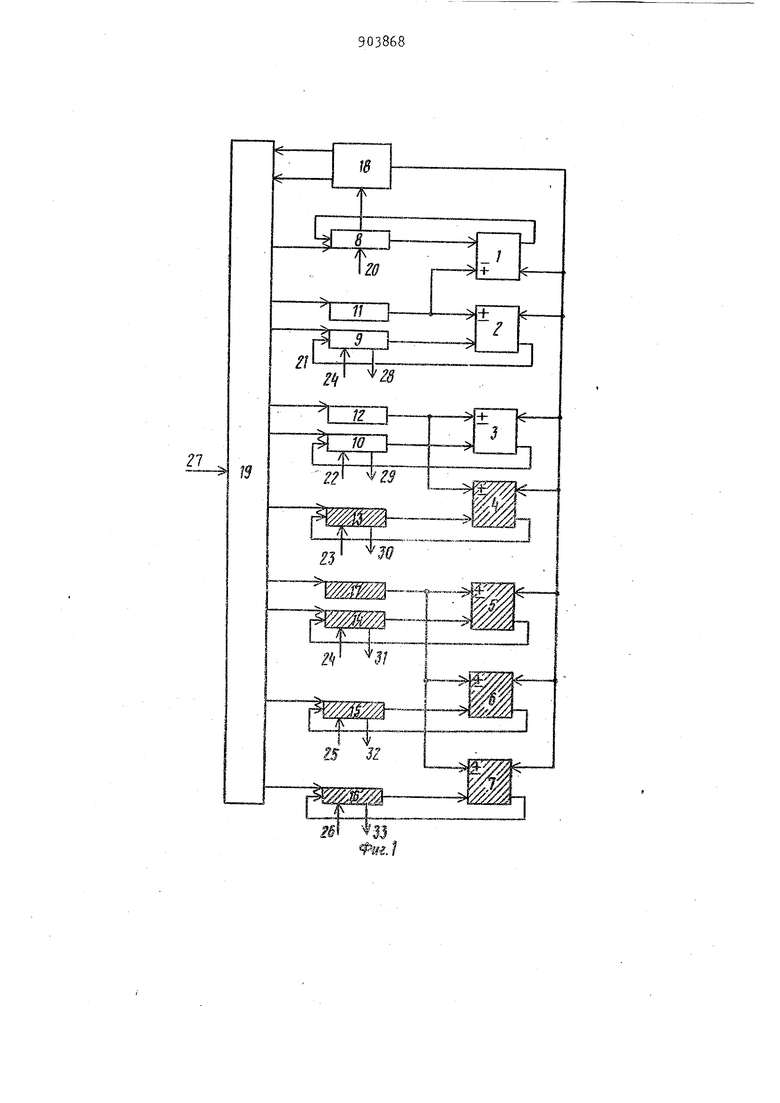

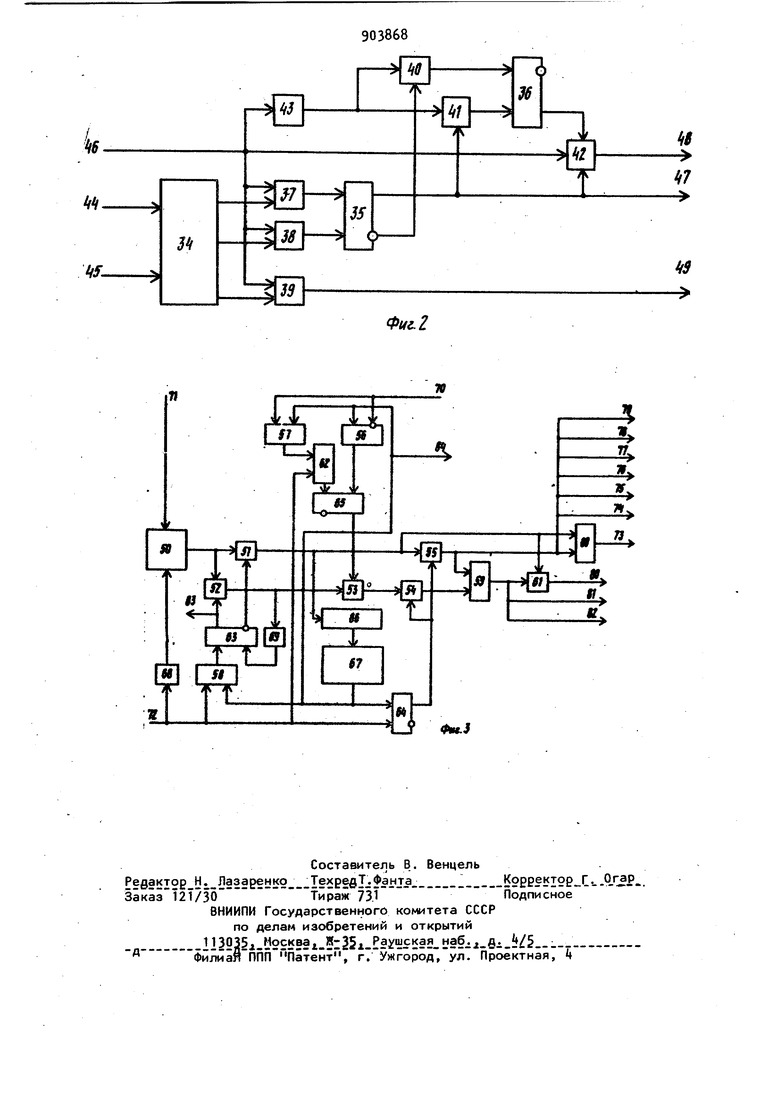

Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной реализации операций вычисления элементарных /функций в устройствах и системах автоматики и вычислительной техники . По основному авт.св. № 633016 известно арифметическое устроиство,содержащее первый, второй и третий сум маторы-вычитатели, первый, второй, третий, четвертый и пятый регистры сдвига, блок анализа сходимости и блок управления, причем выходы перво го, второго и третьего регистров соединены соответственно с первыми вхо дами первого, второго и третьего сум маторов- вычитателей, выходы которых соединены соответственно с входами этих регистров, второй выход первого регистра соединен с входом блока ана лиза, второй выход второго регистра соединен с входом четвертого регист ра, выход которого соединен со вторыг входа 1 первого и второго сумматоров-вычитателей, второй выход третьего регистра соединен с входом пятого регистра, выход которого соединен со вторым входом третьего сумматора- вычитателя, первый выход блока анализа соединен с управляющими входами первого, второго и третьего сумматоров-вычитателей, а второй и третий выходы блока анализа соединены с первым и вторым входаг«1 блока управления, третий вход которого соединен с управляющим входом устройства, а управляющие входы первого, второго, третьего, четвертого-и пятого регистров соединены соответственно с первым, вторым, третьим, четвертым и пятым выходами блока управления, вторые входы первого, второго, третьего, и четвертого и пятого регистров соединены соответственно с первым, вторым, третьим, четвертым и пятым входами устройства, вторые выходы второго и третьего регистров . .390 соединены соответственно с первым и вторым выходами устройства fl. Однако это устройство предназнамено только для вычисления частного отделения произведения двух аргументов на третий и не может быть использовано для вычисления других функций Цель изобретения - расширение функциональных возможностей за счет дополнительного вычисления функций , (x -xz-«-yz)/z, {x -xz-fz)/z, (f y-yz+z }/z. Поставленная цель достигается тем мто в арийметическое устройство доЬолнительно введены четвертый, пятый, шестой и седьмой сумматоры-вычи татели, шестой, седьмой, восьмой, де вятый и десятый регистры, причем пер вые выходы шестого, седьмого, восьмого, девятого регистров соединены соответственно с первыми входами чет вертого, пятого, шестого и седьмого сумматоров-вычитателей, выходы которых соединены соответственно с первы ми входами шестого, седьмого, восьмого и девятого регистров, а управляющие входы четвертого, пятого, шес того и седьмого сумматоров-вычитателей соединены с первьм выходом блока анализа, выход пятого регистра соеди нен со вторым входом четвертого сумматора- вычитателя, второй выход седь мого регистра соединен со входом десятого регистра, выход которого соединен со вторыми входами пятого, шестого и седьмого сумматоров-вычи.тателей, шестой, седьмой, восьмой, девятый и десятый выходы блока управ ления соединены с управляющими входа ми соответственно шестого, седьмого, восьмого, девятого и десятого регистров. Такое конструктивное решение позволяет одновременно с вычислением функции xy/z дополнительно вычислять еще четыре элементарных функции. На фиг. 1 представлена структурная схема арифметического устройства; на фиг. 2 - вариант структурной схемы блока анализа; на фиг. 3 вариант структурной схемы блока управления. Арифметическое устройство содержит с первого по седьмой одноразрядные сумматоры-вычитатели 1-7, с первого по десятый регистры 8-17, блок анализа 18, блок управления 19, входы 20-26, управляющий вход 27, выходы 28-33. Сумматоры-вычитатели 1-7 могут быть выполнены в виде одноразрядной комбинационной схемы, по второму входу которой в зависимости от значения сигнала на управляющем входе выполняется сложение или вычитание. Регистры 8-10, 13-16 являются обычными регистрами, которые обеспечивают при подаче тактовых импульсов на управляющий вход продвижение кодов на вь1ход. Регистры 11-12 и 17 являются регистрами сдвига/Один из вариантов реализации может содержать регистр сдвига, выход и вход которого (увязан через элемент И. Первоначально элемент И закрыт. Подается тактовый импульс сдвига и содержание регистра сдвига сдвигается на один разряд вправо от двоичной запятой. Затем элемент И открывается и подаются тактовые импульсы, которые подвигают содержание регистра сдвига на выход, причем по цепи обратной связи через открытый элемент И происходит восстановление сдвинутого значения. Блок анализа 18 может быть реализован по схеме (фиг. 2е) и содержит схему сравнения кодов 3, триггеры 35-36, элементы И и ЭJ1eмeнт задержки 3, входы kk-k6 и выходы . На один вход k схемы сравнения Jk подается значение содержания регистра В. На другой вход 5 схемы сравнения 3 подается нулевой потенциал. Выходы схемы сравнения 3 (X 7/0 и ) через элементы И 37-38 соединены с входами триггера 35 выходы которого соединены с входами элементов И 40-41 соответственно. Единичный выход триггера 35 также соединен с одним из входов элемента И 42 и является первым (47) выходом блока анализа 13- Выходы элементов И 40-41 соединены с входами триг гера 36, выход которого соединен с другим входом элемента И 42. Выход.,, элемента И 42 является вторым выходом (48) блока анализа 18, третьим выходом (49) которого является выход элемента И 39i соединенного с третьим выходом (сигнал X ; 0) схемы сравнения 34. Входы элементов И 37-39 и 42 соединены с входом 46 для тактового импульса конца итераций, к которому подсоединены также входы элементов И 40-41 через элемент задержки k3 (длительность задержки которо го больше периода тактовых импульсо Вход 6 на фиг. 1 не показан, поскольку для иного варианта выполнения блока 18 в этой связи нет необходимости. Блок управления 19 может быть ре ализован по схеме, приведенной на фиг. 3, и содержит управляемый гене ратор 50 .тактовых импульсов, элементы И 51-57,.элементы ИЛИ 38-62, триггеры 63-65, счетчик 66, дешифра тор б7, элементы задержки 68-69, вх ды 70-72, выходы 73-8. Первый вход блока управления 19 соединен с инверсным входом элемента И 5б, выход которого соединен с входом установки триггера б5. Второй вход 71 блока управления 19 соединен с входом остановки генератора 50, на вход за пуска которого подсоединен через эл мент задержки 68 третий вход 72 бло ка управления 19, который также соединен с одним из входов элементов ИЛИ 58 и 62 и входом сброса триггера 6. Выходы 73-79 блока управления 19 соединены соответственно с- у равлякйдими входаг«1 регистров 8-10, 13-16. Выходы 80-82 блока управления 19 соответственно с уп равляющими входами регистров 11-12 и 17. Выход 83 с триггера 63 может быть соединен с регистрами 11-12 и 17 (на фиг. 1 эта связь не приведена, поскольку при других вариантах выполнения регистров 11-12 и 17 в этой связи нет необходимости). Выход 84 с выхода дешифратора 67 (для сигнала тактового импульса конца , итерации) подается на вход Н6 блока анализа 18 (на фиг. 1 эта связь не приведена, поскольку при ином варианте выполнения блока анализа 18 импульс конца итерации может формироваться внутри блока анализа 18). Управляемый генератор 50 тактовых импульсов представляет собой стандартный генератор тактовых импульсов, работающих в старт-стопном режиме. Элементы задержки 68-69 могут быть выполнены в виде линии задержки импульсных сигналов на время, равное или большее длительности тактовых им пульсов. С выхода дешифратора -67 на элемент ИЛИ 58, элементы И 56-57, вы ход 8 и установочный вход триггера 6 выдается импульс окончания ите рации. Элемент И 5б с одним инверсным входом обеспечивает установку триггера 65 при отсутствии сигнала на первом входе 70 блока управления Т9. В этом случае элемент И 53 открыт и тактовый импульс конца итерации подается на выходы 80-82 блока управления 19 для сдвига значений в регистрах 11-12 и 17. Итерационный процесс вычисления указанных функций основан на одновременном решении систему разностных рекуррентных соотношений Х -Х-21 C,j--Sign Z..,(V32j2- . Vo -- У .,м Щ 2. Ч, Hj+.-h Vo--J у.,-+и--У.) Х -ХХ4У2 . V/o:2 + z . z. s,,4;--sa+q3V32 j ОТЙ порядковый номер ите рации; Н О,и - показатель веса итерации;ЧИСЛО разрядов. Соотношение X: реализуется в сумматоре- вычитатеяе 1, а соотношение 7,в сумматоре-аычитателе 2, соотношение VJ - в сумматоре-вычитателе 3) соотг ношение Ил - в сумматоре-вычитателе 5t -.л.,соотношение V - в сумматоре-вычита- . теле 6. Соотношение Sj реализуется в сумматоре-вычитателе k, соотношение W.J - 13 сумматоре-вычитателе 7Значение получается в регистpe 11, значение Уа в регистре 12, а значение ИхЗ- в регистре 17- Логическое уравнение q,j sign45 Решается в блоке анализа 18, где одновременно проверяются условия.(. X-i 0. Вычисления в арифметическом устройтве осуществляютсяСледунхцим обраом. Первоначально в регистры 8 и И по входам 20 и 21) заносится код аргумента X, в регистры 10 и 15 (по вхо дам 22 и 23 - код аргумента У, в регистры 9 13 и 16 (по входам 2, 25 и 26 - код аргумента 2-. По входу 27 на блок управления 19 подается стартовый импульс, который устанавливает в единицу триггер 63 и в нулевое состояние триггеры и б5 и через задержку в элементе задержки 68 включа ет генератор 50 тактовых импульсов. Через открытый элемент И 52 первый тактовый импульс через элемент задер ки б9 устанавливает триггер 63 в нулевое состояние. На выходы 80-82 пер Гвый актовый импульс в нулевой итера :ции не проходит, так как элементы И 53 и 5 закрыты. Элемент И 52 закр вается, а элемент И 5 открывается и на выходы 73 и 80 через элементы ИЛИ 60-б1 начинает поступать серия тактовых импульсов, которые одновременно подсчитываются в счетчике 66 и при дости чении их числа величины n+m где m 3,1од2иС число дополнительных Защитных разрядов регистров .8-17. Дешифратор 67 выдает сигнал окончания нулевой итерации. В нулевой итерации работает только сумматор- вычитатель 1, в котором производится вычитание из аргумента X аргумента Z . Результат операций Х- Zзаписывается в регистр 8, причем значе ние аргумента 2. восстанавливается в регистре 11. Сигнал окончания нулевой итерации устанавливает в единичное состояние триггеры 63 и . Элементы И 52, и 55 открываются. Затем процесс продолжается и на выходах 71-82 появляется последовательность тактовых импульсов для итерации. В любой j-ой итерации результаты с выходов сумматоров-вычитателей 1-7 последовательн(Ь записываются младшими разрядами вперед в освобождающиеся при продвижении старшие разряды регистров 8-10, 13-16 и продвигаются к их началу ( в сторону младших разрядов). При присутствии сигнала q, ф: триггер 65 в блоке управления 1 находится в нулевом состоянии, элемент И 53 закрыт, тактовый импульс конца итерации на выходы 80-82 (т.е. на оегистры 11, 12 и 17) не поступае и содержание регистров 11, 12 и 17 н сдвигается. При неравенстве предыдущей и .последующей цифры J/ (т.е. г; 9 {}/)сигнлл q/ -q/j отсутствует.триггер б5 переходит в единичное состояние, элемент И 53 открывается, тактовый импульс конца итерации появляется на выходах 80-82, и содержание регистров 11, 12 и 17 сдвигается на один разряд и т.д. При появлении сигнала (Jr- (.- триггер б5 устанавливается Б нулевое состояние (по цепочке из элемента И 57 и элемента ИЛИ 62) и элемент И 53 закрывается до момента изменения цифры CJ,. 8 конце каждой итерации по такто ° импульсу окончания итерации, например, снимаемому с выхода 8 блока управления 19 и подаваемому на вход А6 блока анализа 18, в последнем открывается один из элементов И 37-39 в зависимости от результатов сравнения кода Хи (содержания регистра 8) с нулем в схеме сравнения X.- 7 О триггер 36 устанавливается в единичное состояние ( с +1), при - в нулевое состояние (q, -1). При X ; О сигнал с третьего выхода блока анализа 18 останавливает генератор 50 тактовых импульсов в блоке управления 19 (по второму входу 71). В элементе И 2 проверяется условие .V-fИ при выполнении этого условия на втором выходе 8 блока анализа 18 появляется сигнал, передающийся на первый вход 70 блока управления 19. При этом происходит переход к следующей величине сдвига , т.е. вес следующей итерации увеличивается на единицу. При значении +1 сумматор-вычитатель 1 работает в-режиме вычитания, а сумматоры-вычитатели 2-7 работают в режиме сложения. При значении фл -1 их режим работы меняется на обратный. После выполнения определенного числа итераций содержание регист.ра 8 становится равным нулю и процесс вычисления закончен. При этом в регистре Э (выход 28) содержится значение аргумента X, а в регистре 10 (выход 29) значение функции ХУ/2, в регистре 13 {выход 30) - значение функции (ХУ - yZ +Z)/Z, в регист- И ре 14 - значение функции X /Z, в регистре 15 - значение функции (X -XZ+yZ)/Z, в регистре 16 - значение функции (X -XZ+Z)/Z.:

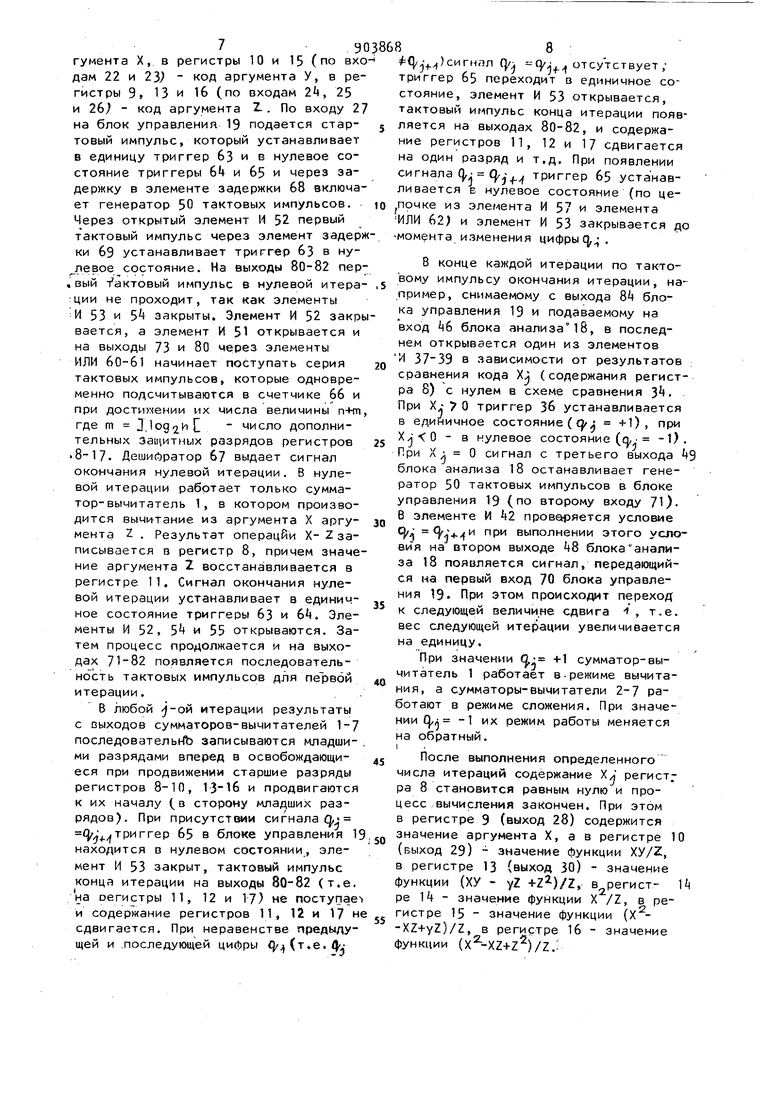

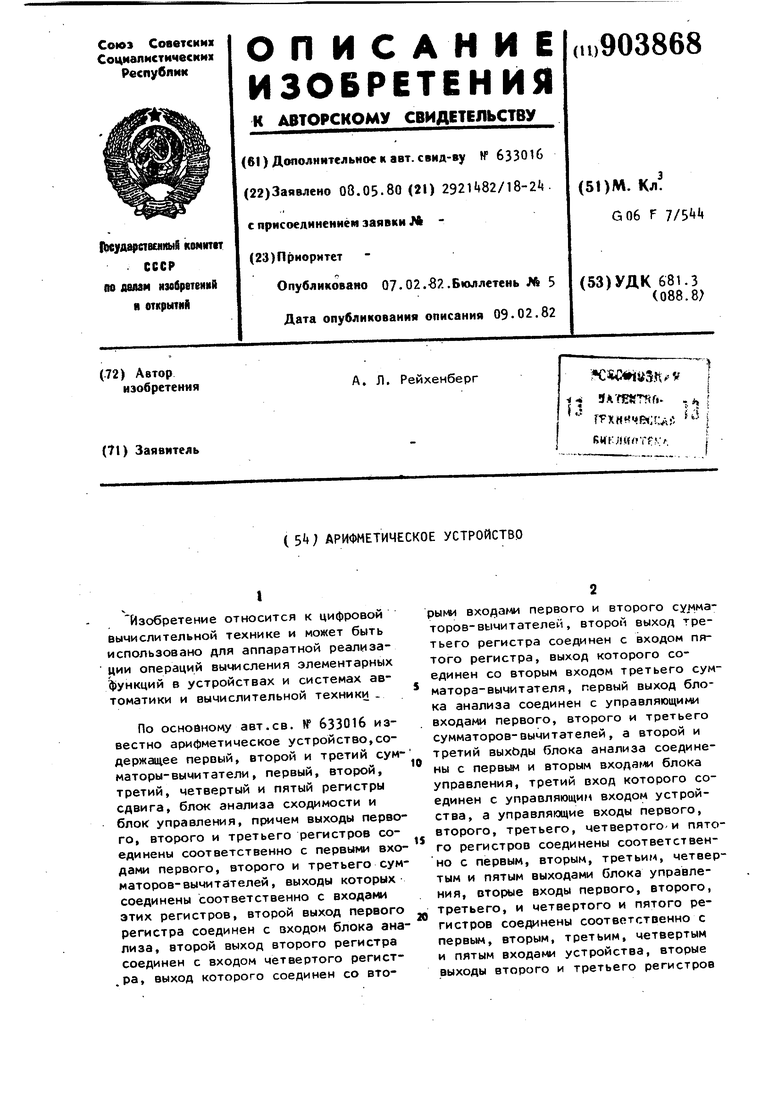

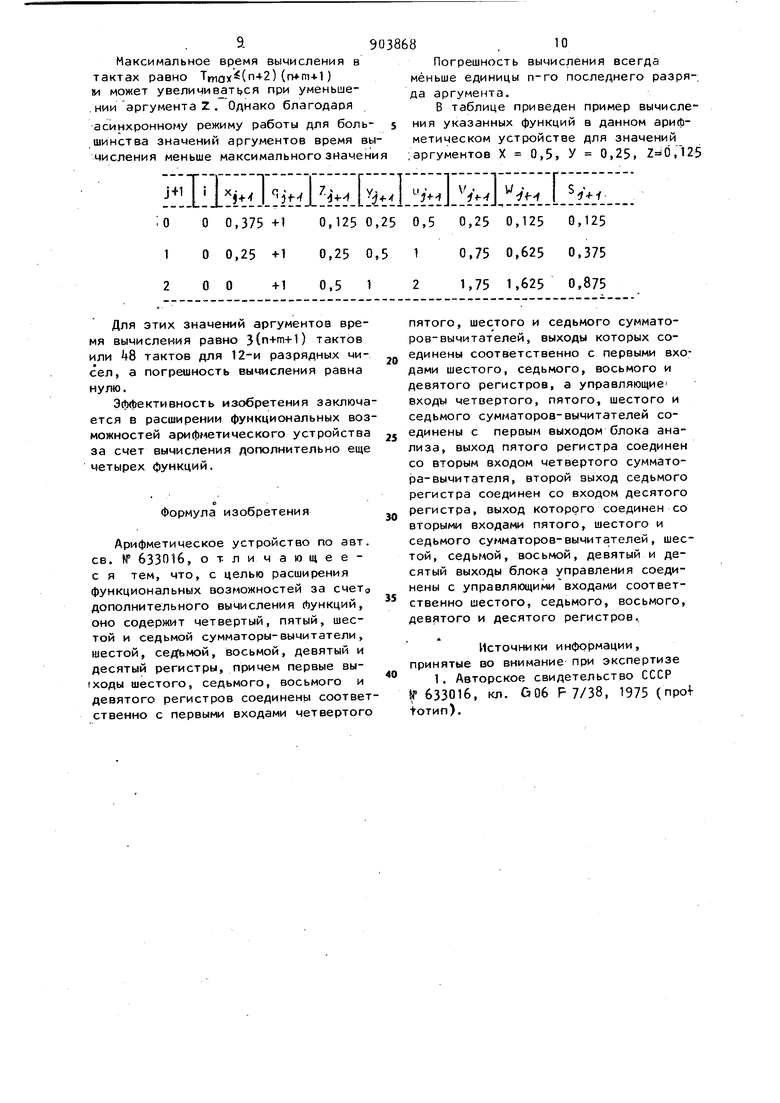

Максимальное время вычисления вПогрешность вычисления всегда

тактах равно T|7iQy(n42) (rv m-t-l)меньше единицы п-го последнего разря1И может увеличиваться при уменьше-дд аргумента.

/НИИаргумента Z. Однако благодаряв таблице приведен пример вычислеасинхронному режиму работы для боль- sния указанных функций в данном арифшинства значений аргументов время вы-метическом устройстве для значений

числения меньше максимального значения; аргументов X 0,5, У 0,25, ,125

Для этих значений аргументов время вычисления равно 3(n+m+l) тактов или 48 тактов для 12-и разрядных чисел, а погрешность вычисления равна нулю.

Эффективность изобретения заключается в расширении функциональных возможностей арифметического устройства за счет вычисления дополнительно еще четырех функций.

Формула изобретения

Арифметическое устройство по авт. св. № 633016, отличающеес я тем, что, с целью расширения функциональных возможностей за счето дополнительного вычисления функций, оно содержит четвертый, пятый, шестой и седьмой сумматоры-вычитатели, шестой, седьмой, восьмой, девятый и десятый регистры, причем первые вы1ХОДЫ шестого, седьмого, восьмого и девятого регистров соединены соответственно с первыми входами четвертого

ПЯТОГО, шестого и седьмого сумматоров- вычитателей, выходы которых соединены соответственно с первыми входами шестого, седьмого, восьмого и девятого регистров, а управляющие входы четвертого, пятого, шестого и седьмого сумматоров-вычитателей соединены с первым выходом блока анализа, выход пятого регистра соединен со вторым входом четвертого сумматора- вычитателя, второй выход седьмого регистра соединен со входом десятого регистра, выход которого соединен со вторыми входами пятого, шестого и седьмого сумматоров-вычитателей, шестой, седьмой, восьмой, девятый и десятый выходы блока управления соединены с управляющими входами соответственно шестого, седьмого, восьмого, девятого и десятого регистров.

Источники информации, принятые во внимание при экспертизе

Фиг. 2

Авторы

Даты

1982-02-07—Публикация

1980-05-08—Подача