1

Изобретение относится к области цифровой вычислительной техники и может иснользоваться при аппаратном вычислении элементарных функций, в частности в специализированных двоичных цифровых вычислительных машинах с фиксированной запятой.

Известно устройство для вычисления математических функций, содержащее блок управления, выходы которого соединены с накопительными и сдвигающими регистрами и блоком памяти, а выходы накопительных регистров- с первыми входами одноразрядных сумматоров-вычитателей, выходами подключенных к входам накопительных регистров, блок определения цифры псевдочастного, блок анализа сходимости и блок сброса, выход которого подключен к блоку управления.

Цель изобретения - расширение класса рещаемых задач путем вычисления функции тригонометрического тангенса.

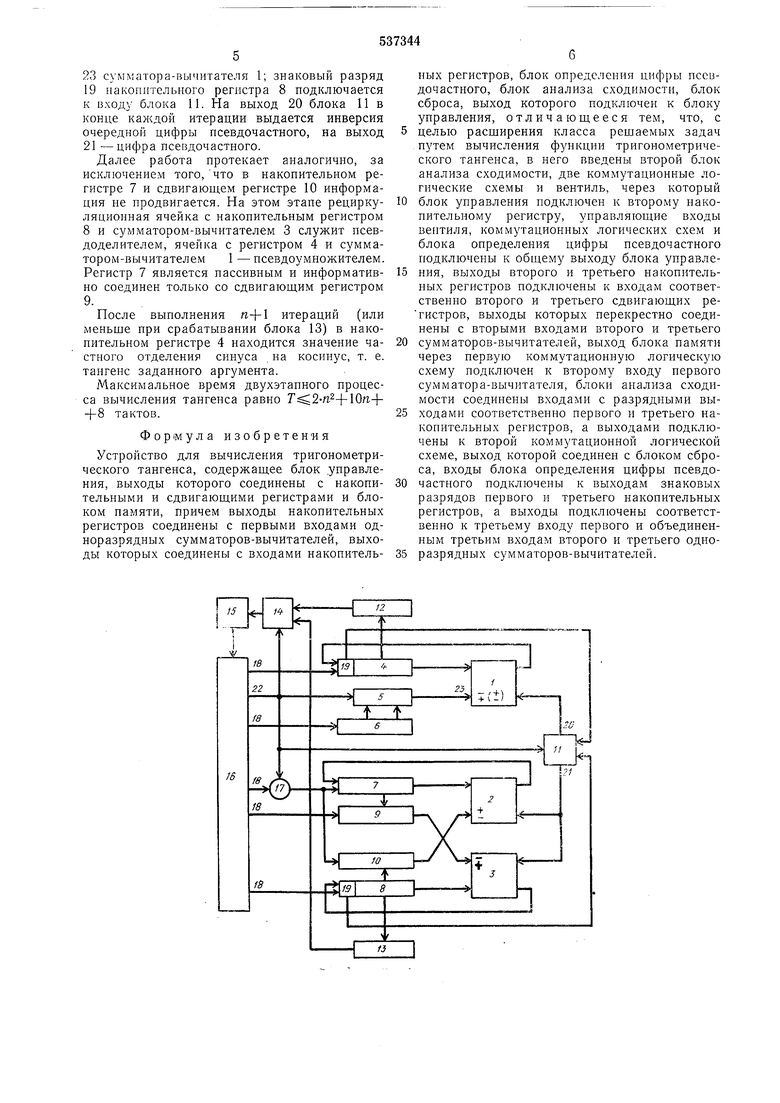

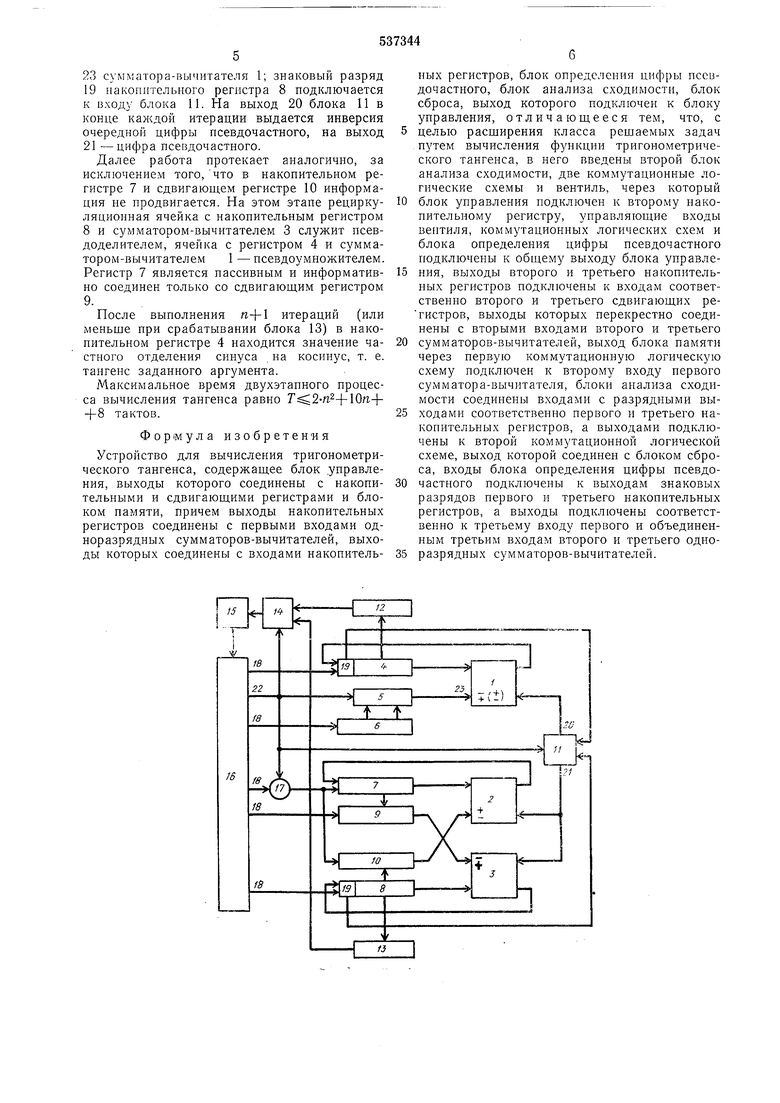

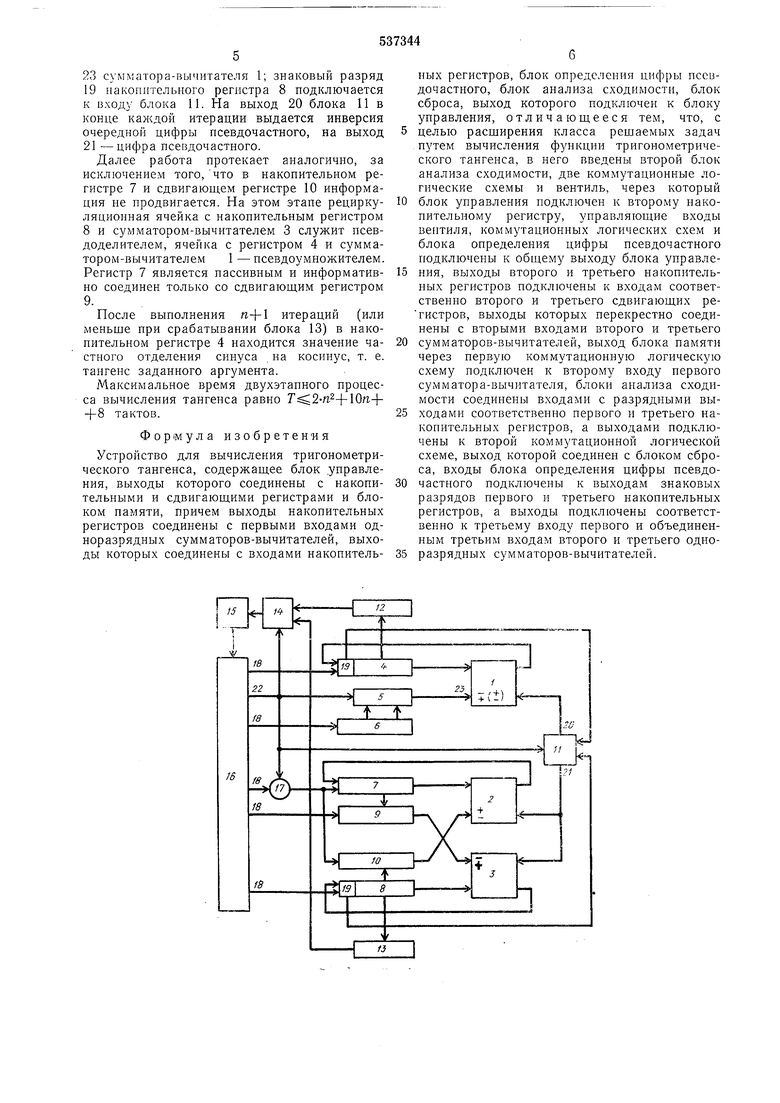

Для этого в устройство введены второй блок анализа сходимости, две коммутационные логические схемы и вентиль, через который блок управления подключен к второму накопительному регистру. Управляющие входы вентиля, коммутационных логических схем и блока определения цифры псевдочастного подсоединены к общему выходу блока управления, выходы второго и третьего накопительных регистров - к входам соответственно второго и третьего сдвигающих регистров, выходы которых перекрестно соединены с вторыми входами второго и третьего сумматороввычитателей. Выход блока памяти через первую коммутационную логическую схему подключен к второму входу первого сумматоравычитателя, блоки анализа сходимости входами- к разрядным выходам соответственно первого и третьего накопительных регистров, а выходами - к второй коммутационной логической схеме, выход которой соединен с блоком сброса. Входы блока определения цифры псевдочастного подсоединены к выходам знаковых разрядов первого и третьего наконительных регистров, а выходы - соответственно к третьему входу первого и объединенным третьим входам второго и третьего одноразрядных сумматоров-вычитателей. Блок-схема устройства представлена на

чертеже.

Устройство включает в себя одноразрядные сумматоры-вычитатели 1-3 комбинационного типа, накопительный регистр 4, коммутационную логическую схему 5, блок 6 памяти, вынолненный в виде односторонней памяти с поразрядной выборкой двух слов одновременно, накопительные регистры 7, 8, сдвигающие регистры 9, 10, блок И определения цифры псевдочастного, блоки 12, 13 анализа

сходимости (схемы сравнения), коммутационную логическую схему 14, блок 15 сброса (остановки процесса), блок 16 управления, вентиль 17.

Устройство содержит три рециркуляционные ячейки, состоящие из соединенных в кольцо сумматоров-вычитателей и накопительных регистров. Блок 6 памяти хранит константы вида arctg2(+i и 2-(J+i), которые выбираются одновременно по одному адресу каждым тактовым импульсом с выхода

18блока 16 управления. Знаковые разряды

19накопительных регистров 4 и 8 соединены с входами блока 11 определения цифры псевдочастного. С выхода 20 блока 11 выдается либо цифра псевдочастного, либо ее инверсия, с выхода 21-цифра псевдочастного. Значение очередной цифры псевдочастного определяет режим сложения - вычитания одноразрядных сумматоров-вычитателей 1-3.

Вентиль 17, коммутационная логическая схема 5, блоки 11 и 14 управляются сигналом управления для перестройки связей в структуре устройства.

Цикл вычисления тригонометрического тангенса состоит из двух этапов. На первом этапе вычисляются значения тригонометрических синуса и косинуса. Интервал изменения аргумента, определяемый современными практическими требования, следующий: . Принцип вычисления основан на операциях псевдоделения и псевдоумножения с параллельным решением разностных рекуррентных соотношений в итерационном процессе:

2о в Zy+i в - QJ+I Zj -.arctg2- +)

+ 1 при

qj sign Zj 1 при

J Q,,...,n

X, X,,Xj-qjY,2-Cf

л

. созв

Y, 0 У;+1 Yf- qjXj2- J Г„ - Г„, sinQ

j

(1+2-2(/-1)Л J 0

В начальном состоянии в регистр 4 заносится значение аргумента Э, в регистр 7 - нулевое значение, в регистр 8 - значение обратной величины коэффициента удлинения вектора. Каждое рекуррентное соотношение вычисляется последовательно за () тактов, где п - количество разрядов аргумента, т - число дополнительных разрядов для компенсации погрешности округления при сдвиге. На первом этапе вычислений импульс управления с выхода 22 блока 16 управления открывает вентиль 17, коммутирует выход блока 12 на вход блока 15 и знаковый разряд 19 накопительного регистра первой рециркуляционной ячейки, содержимое которой является в этом этапе псевдоделителем, на вход блока 11. При этом на выходах 20 и 21 блока 11 после каждой итерации появляется очередное значение цифры (разряда) псевдочастного для следующей итерации. Схема 5 пропускает на вход 23 сумматора-вычитателя значение констант arctg ). В любой итерации с выходов 18 блока 16 управления в

0 регистры и на вход блока 6 памяти поступает серия тактовых сдвигающих импульсов. При этом из содержания регистра 4 вычитается значение arctg 2 -+ при qj (либо проводится суммирование при qj - 1).

5 Содержимое регистров 7 и 8 ячеек псевдоумножителей перекрестно суммируется - вычитается со сдвинутыми переадресованными координатными составляющими тригонометрического вектора, который вращается на

0 сходящуюся последовательность угловых приращений (констант).

Полученный в каждой итерации результат последовательно, начиная с младших разрядов, заносится в освобождающиеся старшие

5 разряды накопительных регистров и сдвигается до конца регистра.

После выполнения п+1 итераций в регистре 4 находится нулевое значение, в регистре 7 - значение синуса, в регистре 8 - значение

0 косинуса. Однако для большинства значений аргумента в итерационный процесс сходится на итерации, номер которой меньше п. При этом в регистре 4 содержимое равно нулю и блок 12 анализа сходимости (цифровая схема

5 сравнения с логическим нулем) выдает сигнал в блок 15 сброса, а блок 16 управления прекращает выдавать тактовые сдвигающие импульсы на следующей итерации. После остановки процесса вычисления блок

16 управления снимает сигнал с выхода 22. Второй этап вычисления тригонометрического тангенса - операция деления полученных синуса на косинус - также основан на принципе псевдоделения и псевдоумножения в итерационном процессе с параллельным решением разностных рекуррентных соотнощений. Каждое соотнощение вычисляется последовательно за () тактов. Алгоритм деления записывается в виде:

X, Хп, Xj+г Xj - qjYn,2-(i „ - О

.. +1 при .

:rrsign ::: J/n У

J

{ -1 При + 2-)

tg9.

п,

После снятия импульса управления, что соответствует началу второго этапа вычисления, вентиль 17 закрывается, схема 14 соединяет выход блока 13 анализа сходимости с входом блока 15, а схема 5 - второй выход блока 6

памяти с константами вида 2 - на вход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Двоичное устройство деления | 1974 |

|

SU497585A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления экспоненциальной функции | 1973 |

|

SU538366A1 |

| Устройство для формирования гиперболических функций | 1973 |

|

SU484522A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1973 |

|

SU536490A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

Авторы

Даты

1976-11-30—Публикация

1973-10-04—Подача