дом Запись устройства, первый вход блока синхронизации является входом Пуск устройства, а второй вход блока синхронизации - входом Сброс устройства.

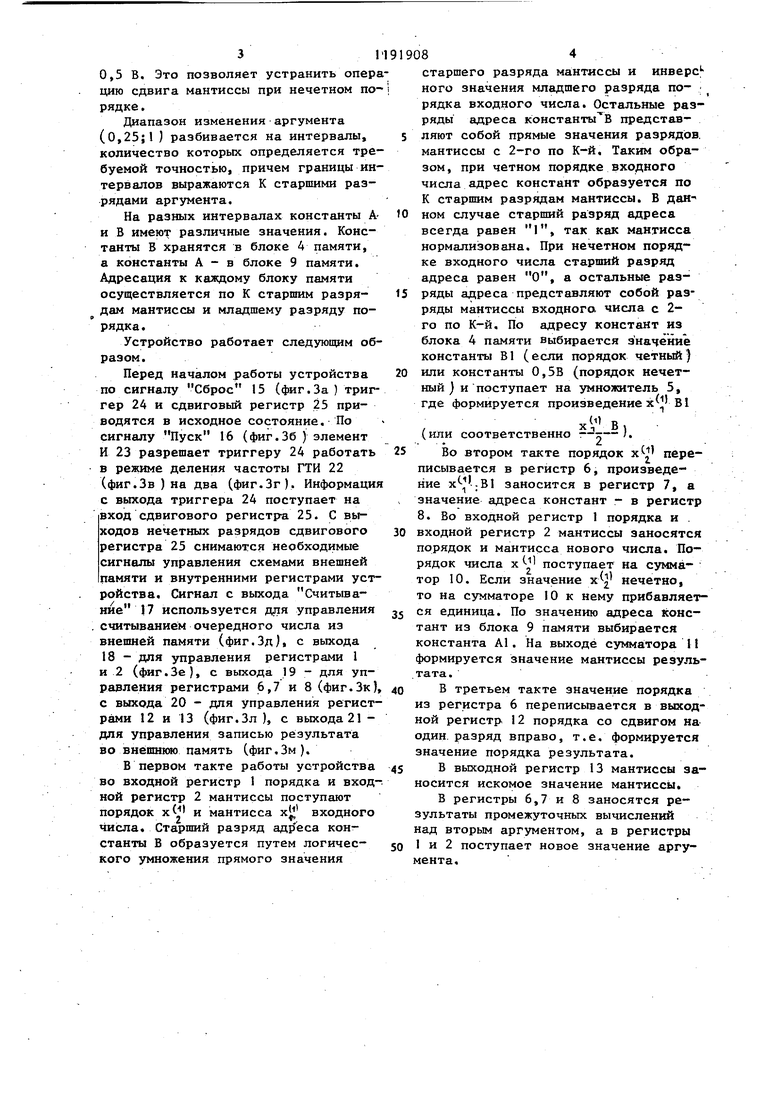

2, Устройство поп.1,отлич ающее с я тем, что блок синхронизации содержит генератор тактовых импульсов, элемент И, триггер и сдвиговый регистр, причем инверсный выход триггера подключен к первому входу элемента И блока синхронизации, прямой выход триггера подключен к информационному входу сдви гового регистра, выход элемента И блока синхронизации подключен к уп91908

равляющему входу триггера, прямой .выход генератора тактовых импульсов подключен к счетному входу триггера, инверсный выход генератора тактовых импульсов подключен к входу синхронизации сдвигового регистра, выходы первого, третьего, пятого, седьмого и девятого разрядов сдвигового регистра являются соответственно первым, вторым, третьим, четвертым и пятым выходами блока синхронизации, второй вход элемента И блока синхронизации является первьм входом блока синхронизации, а соединенные между собой входы сброса сдвигового регистра и триггера являются вторым входом блока синхронизации..

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Устройство для возведения в степень | 1985 |

|

SU1290308A1 |

| Устройство для вычисления корня | 1985 |

|

SU1339556A1 |

| Устройство для вычисления корня третьей степени | 1985 |

|

SU1288695A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1145340A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1273921A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

1. УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее семь регистров, два сумматора, два блока памяти и блок синхронизации, причем выход первого регистра подключен к информационному входу второго регистра, выход первого сумматора подклю- . чей к информационному входу пятого регистра, отличающееся тем, что, с целью расширения диапазона входных чисел, в него введены элемент И и умножитель, причем адресный вход первого блока памяти, начиная с второго разряда, подключен к выходу третьего регистра, начиная с второго разряда, и к информационному входу четвертого регистра, начиная с второго разряда, инверсный выход последнего разряда первого регистра подключен к первому входу элемента И, выход первого разряда третьего регистра подключен к второму входу элемента И, выход элемента И подключен к первому разряду адресного входа первого блока памяти и к входу первого разряда четвертого регистра, выход четвертого регистра подключен к адресному входу второго блока памяти, выход второго блока памяти подключен к первому информационному входу первого сумматора, выход шестого регистра подключен к второму информационному входу первого сумматора, выход умножителя подключен к информационному входу шестого регистра, выход третьего регистра подключен к первому информационному входу умножителя, выход первого блока памяти подключен к второму информационному входу умножителя, выход второго регистра подключен к первому информационному вхосл ду второго сумматора, выход последнего разряда второго регистра подключен к последнему разряду второго информационного входа второго сумматора, второй информационный вход второго сумматора, за исключением последнего разряда, подключен к шине логического нуля устройства, выход второго сумматора подключен со сдвигом на один разряд в сторону со о последнего разряда к информационно-, му входу седьмого регистра, первый 00 выход блока синхронизации является выходом Считьшание устройства, второй выход блока синхронизации подключен к входу синхронизации первого и третьего регистров, третий выход блока синхронизации подключен к входу синхронизации второго, четвертого и шестого регистров, четвертый выход блока синхронизации подключен к входу синхронизации пятого и седьмого регистров, пятый выход блока синхронизации является выхо-

Изобретение относится к вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах при обработке данных в формате с плавающей запятой.

Цель изобретения - расширение диапазона входных чисел за-счет обработки чисел в формате с плавающей запятой,

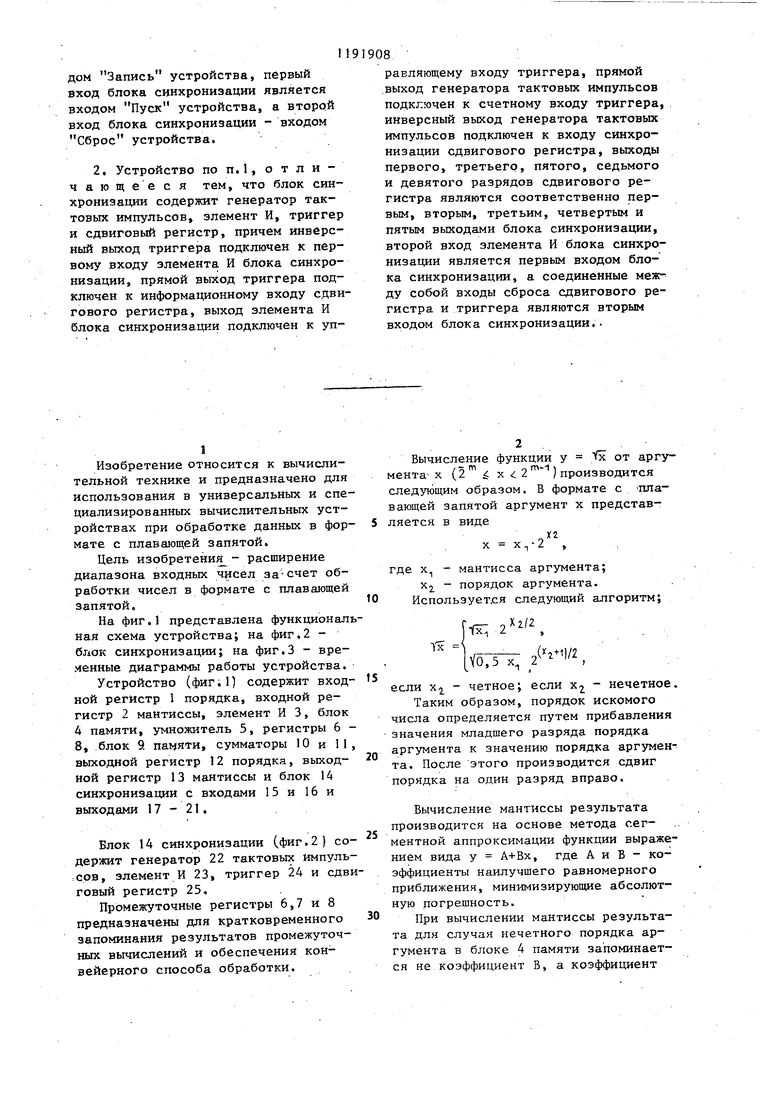

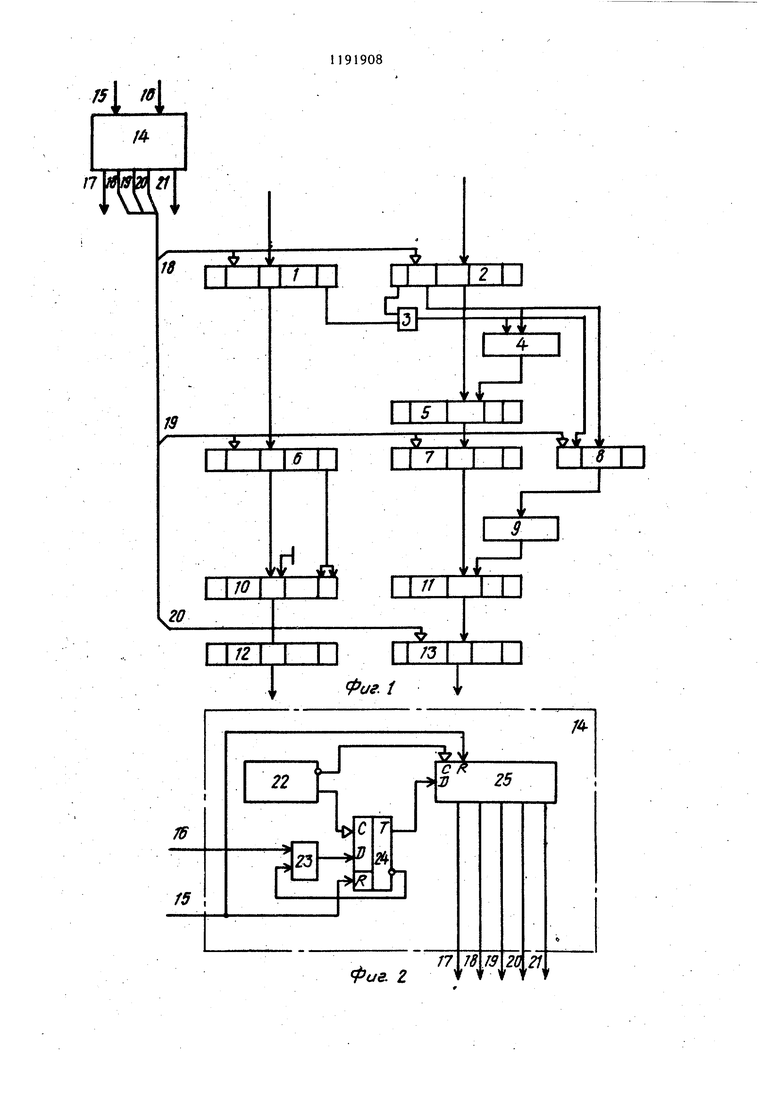

На фиг,1 представлена функциональная схема устройства; на фиг.2 блок синхронизации; на фиг.З - временные диаграммы работы устройства.

Устройство (фиг.1 содержит входной регистр 1 порядка, входной регистр 2 мантиссы, элемент И 3, блок 4 памяти, умножитель 5, регистры 6 8, блок 9, памяти, сумматоры 10 и 11, выходной регистр 12 порядка, выходной регистр 13 маштиссы и блок 14 синхронизации с входами 15 и 16 и выходами 17-21.

Блок 14 синхронизации (фиг.2) содержит генератор 22 тактовых импуль,сов, элемент И 23, триггер 24 и сдвиговый регистр 25.

Промежуточные регистры 6,7 и 8 предназначены для кратковременного запоминания результатов промежуточных вычислений и обеспечения конвейерного способа обработки.

Вычисление функции у Tfx от аргумента- к (2 х ) производится следующим образом. В формате с Плавающей запятой аргумент х представляется в виде

)Г2 X - X i ,

где х - мантисса аргумента;

Xj - порядок аргумента. Используется следующий алгоритм;

Xl/Z

Кх:; 2

-ix

YoTTl ,

у

если х - четное; если Х2 - нечетное.

Таким образом, порядок искомого числа определяется путем прибавления значения младшего разряда порядка аргумента к значению порядка аргумента. После этого производится сдвиг порядка на один разряд вправо.

Вычисление мантиссы результата производится на основе метода сегментной аппроксимации функции выражением вида у А+Вх, где А и В - коэффициенты наилучшего равномерного приближения, минимизирующие абсолютную погрешность.

При вычислении мантиссы результата для случая нечетного порядка аргумента в блоке 4 памяти запоминается не коэффициент В, а коэффициент 3 0,5 В. Это позволяет устранить опер цию сдвига мантиссы при нечетном по рядке. Диапазон изменения аргумента (0,25;1 ) разбивается на интервалы, количество которых определяется тре буемой точностью, причем границы ин тервалов выражаются К старшими разрядами аргумента. На разных интервалах константы А и В имеют различные значения. Константы В хранятся в блоке 4 памяти, а константы А - в блоке 9 памяти. Адресация к каждому блоку памяти осуществляется по К старшим разрядам мантиссы и младшему разряду порядка. Устройство работает следующим об разом. Перед Началом работы устройства по сигналу Сброс 15 (фиг.За ) триг гер 24 и сдвиговый регистр 25 приводятся в исходное состояние. По сигналу Пуск 16 (фиг.36 ) элемент И 23 разрешает триггеру 24 работать в режиме деления частоты ГТИ 22 (фиг.Зв ) на два (фиг.Зг). Информаци с выхода триггера 24 поступает на вход сдвигового регистра 25. С выходов нечетных разрядов сдвигового регистра 25 снимаются необходимые сигналы управления схемами внешней памяти и внутренними регистрами уст ройства. Сигнал с выхода Считывание 17 используется для управления . считыванием очередного числа из внешней памяти (фиг.Зд), с выхода 18 - для управления регистрами 1 и 2 (фиг.Зе), с выхода 19 - для управления регистрами 6,7 и 8 (фиг.Зк с выхода 20 - для управления регист рами 12 и 13 (фиг.3л ), с вькода21 для управления записью результата во внешнюю память (фиг.3м). В первом такте работы устройства во входной регистр 1 порядка и вход ной регистр 2 мантиссы поступают порядок и мантисса входного числа Старший разряд адреса константы В образуется путем логического умножения прямого значения 84 старшего разряда мантиссы и инверс ного значения младшего разряда порядка входного числа. Остальные разряды адреса константы В представ- ляют собой прямые значения разрядов, мантиссы с 2-го по К-й. Таким образом, при четном порядке входного числа адрес констант образуется по К старшим разрядам мантиссы. В дан ном случае старший разряд адреса всегда равен 1, так как мантисса нормализована. При нечетном порядке входного числа старший разряд адреса равен О, а остальные разряды адреса представляют собой разряды мантиссы входного числа с 2го по К-й. По адресу констант из блока 4 памяти выбирается значение константы В1 (если порядок четный) или константы 0,5В (порядок нечетный) и поступает на умножитель 5, где формируется произведение х В1 .XV Ь (или соответственно :-т-;. Во втором такте порядок переписывается в регистр 6, произведение .В1 заносится в регистр 7, а значение адреса констант - в регистр 8. Во входной регистр 1 порядка и . входной регистр 2 мантиссы заносятся порядок и мантисса нового числа. Порядок числа X поступает на сумматор 10. Если значение нечетно, то на сумматоре 10 к нему прибавляется единица. По значению адреса констант из блока 9 памяти выбирается константа А1. На выходе сумма тора 11 формируется значение мантиссы результата. В третьем такте значение порядка из регистра 6 переписьгаается в выходной регистр. 12 порядка со сдвигом на один разряд вправо, т.е. формируется значение порядка результата. В выходной регистр 13 мантиссы заносится искомое значение мантиссы. В регистры 6,7 и 8 заносятся результаты промежуточных вычислений ад вторым аргументом, а в регистры 1 и 2 поступает новое значение аргуента.

4 So4o-Vj -VoHoHs/ViH

4s4otb05 j C«5:

| Устройство для извлечения квадратного корня | 1976 |

|

SU716038A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU922735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-15—Публикация

1984-06-29—Подача