Изобретение относится к вычисли-- тельной технике и предназначено для использования в вычислительных машинах и устройствах с обработкой данных в формате с плавающей запятой

Цель изобретения расиирение функциональных возможностей устройства за счет обработки чисел в формате с плавающей запятой.

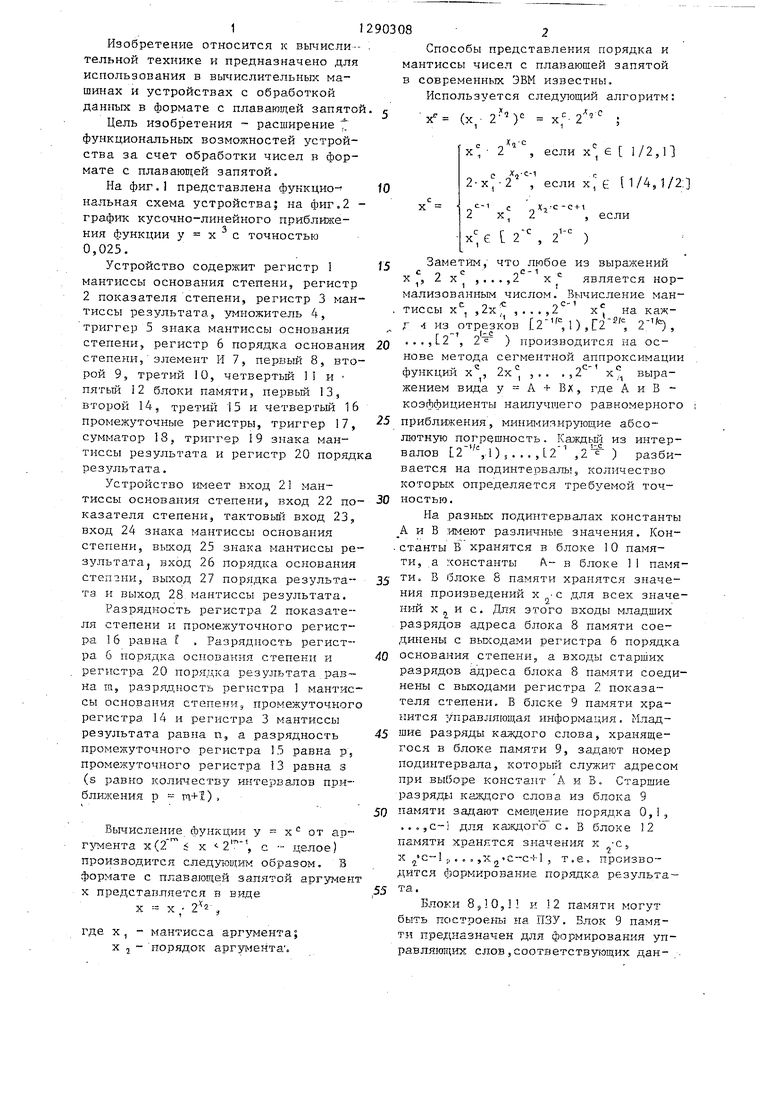

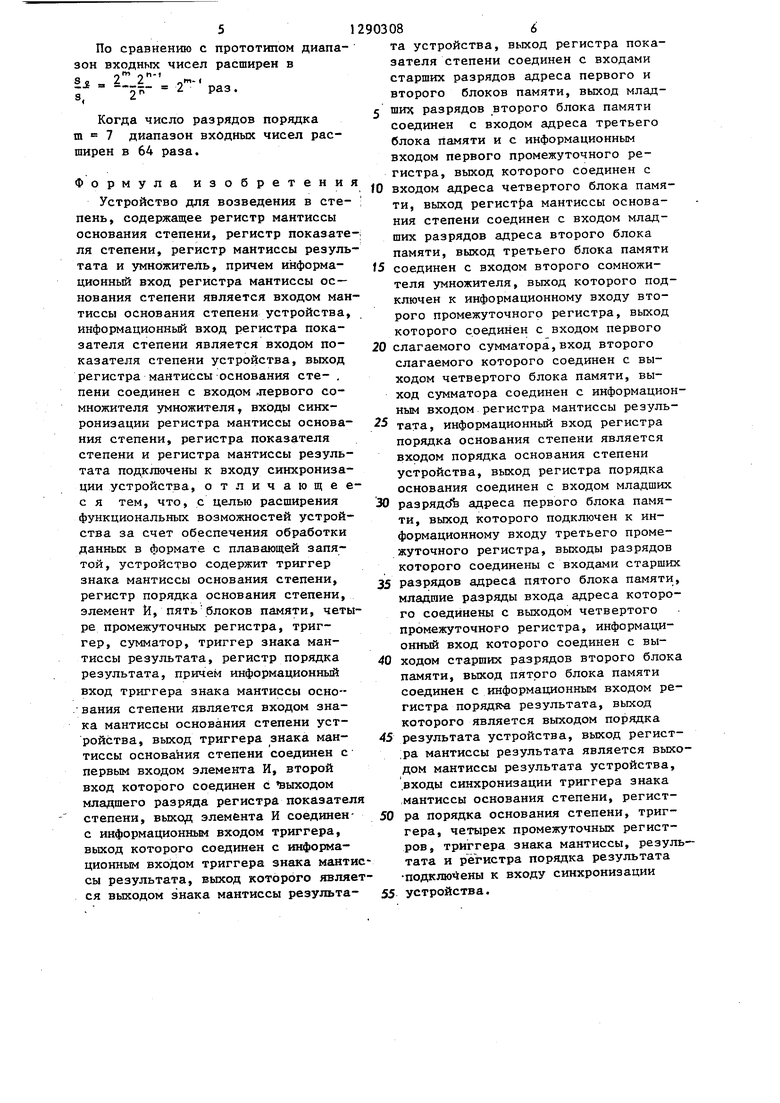

На фиг.1 представлена функцио- нальная схема устройства; на фиг.2 - график кусочно-линейного приблннсе- ния функции у X с точностью 0,025.

Устройство содержит регистр 1 мантиссы основания степени, регистр 2 показателя степени, регистр 3 мантиссы результата, умножитель 4, триггер 5 знака мантиссы основания степени, регистр 6 порядка основания степени, элемент И 7, первый 8, второй 9, третий 10, четвертьй 1 и пятый 12 блоки памяти, первый 13, второй 14, третий 15 и четвертьй 16 промежуточные регистры, триггер 17, сумматор 18, триггер 19 знака мантиссы результата и регистр 20 порядк результата.

Устройство имеет вход 21 мантиссы основания степени, вход 22 по- казателя степени, тактовьш вход 23, вход 24 знака мантиссы основания степени, выход 25 знака мантиссы результата j вход 26 порядка основания степзни, выход 27 порядка результа- та и выход 28 мантиссы результата.

Разрядность регистра 2 показателя степени и промежуточного регистра 16 равна f . Разрядность регистра б порядка основания степени и регистра 20 порядка результата равна т, разрядность регистра 1 мантиссы основания степетуИэ промежуточного регистра 14 и регистра 3 мантиссы результата равна п, а разрядность промежуточного регистра 15 равна р, промежуточного регистра 3 равна з (s равно колш-геству интервалов при- блгокения р m+l).

Вычисление функции у х от ар™ х(2 х , с - целое) производится следующим образом, В формате с плавающей запятой аргумент X представляется в виде X - X ,-

где X, - мантисса арг мента; X J порядок аргумента .

Способы представления порядка и мантиссы чисел с плавающей запятой в современных ЭВМ известны.

Используется следующий алгоритм:

х

с

0 5

0 5

0

5

0

Заметим, что любое из выражений

с- 1

X

X ; , . . . ,2 X является нор- Вычисление ман1 1 мализованным числом.

С п Сг тиссы X . ,2х, ,...,/

г о - UC

г из отрезков 12 , ..,,2 , 2 ) производится

на каж),Г2

-S/C

3

на осо- Ь2 /,

нове метода сегментной аппроксимации функций х, 2х, ,.. ,,2 х выражением вида у А + Вх, где А и В - коэффициенты наилучшего равномерного приближения, мини1 1нзирующие абсолютную погрешность. Каждьш из интервалов 1) 5 . . . , 12 ,2 ) разбивается на подинтервалы, количество которых; определяется требуемой точностью.

На разных подинтервалах константы А и В :имеют различные значения. Константы В хранятся в блоке 10 памяти, а константы Л- в блоке 11 памяти. В блоке 8 памяти хранятся значедля всех значе- с. Для этого входы младших разрядов адреса блока 8 памяти соединены с выходами регистра 6 порядка основания степени, а входы старших разрядов адреса блока 8 памяти соединены с выходами регистра 2 показателя степени, В блоке 9 памяти хранится управляющая информация. Младшие разряды каждого слова, хранящегося в блоке памяти 9, задают номер подынтервала, который служит адресом при выборе констамт А и В. Старшие разряды каждого слова из блока 9 памяти задают смещение порядка 0,1, ..., для каждого с. В блоке 12 памяти хранятся значения х -Cj

ния произведении х: „ с

НИИ X и

С™ ;,. , , ,х . ,

.е, произво

дится формирование порядка результата.

Блор;и BslO, и 12 памяти могут быть построены на ПЗУ. Блок 9 памяти предназначен для формирования управляющих слов,соответствующих дан- .

5

По сравнению с прототипом диапазон входных чисел расширен в

„ nf лП-1

f-z-j- -- - Когда число разрядов порядка m 7 диапазон входных чисел расширен в 64 раза.

Формула изобретени Устройство для возведения в степень, содержащее регистр мантиссы основания степени, регистр показателя степени, регистр мантиссы результата и умножитель, причем информа- ционньй вход регистра мантиссы основания степени является входом мантиссы основания степени устройства, информационньй вход регистра показателя степени является входом показателя степени устройства, выход регистра мантиссы основания сте- , пени соединен с входом лервого сомножителя умножителя, входы синхронизации регистра мантиссы основания степени, регистра показателя степени и регистра мантиссы результата подключены к входу синхронизации устройства, отличающее с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения обработки данных в формате с плавающей запятой, устройство содержит триггер знака мантиссы основания степени, регистр порядка основания степени, элемент И, пять блоков памяти, четыре промежуточных регистра, триггер, сумматор, триггер знака мантиссы результата, регистр порядка результата, причем информационный вход триггера знака мантиссы осно- вания степени является входом знака мантиссы основания степени устройства, выход триггера знака мантиссы основайия степени соединен с первым входом элемента И, второй вход которого соединен с выходом младшего разряда регистра показател степени, выход элемента И соединен- с информационным входом триггера, выход которого соединен с информационным входом триггера знака манти сы результата, выход которого являе ся выходом знака мантиссы результа

903086

та устройства, выход регистра показателя степени соединен с входами старших разрядов адреса первого и второго блоков памяти, выход млад5 ших разрядов второго блока памяти соединен с входом адреса третьего блока памяти и с информационным входом первого промежуточного регистра, выход которого соединен с JO входом адреса четвертого блока памяти, выход регист{)а мантиссы основания степени соединен с входом младших разрядов адреса второго блока памяти, выход третьего блока памяти

15 соединен с входом второго сомножителя умножителя, выход которого подключен к информационному входу второго промежуточного регистра, выход которого соединен с входом первого

20 слагаемого сумматора,вход второго слагаемого которого соединен с выходом четвертого блока памяти, выход сумматора соединен с информационным входом регистра мантиссы резуль25 тата, информационный вход регистра порядка основания степени является входом порядка основания степени устройства, выход регистра порядка основания соединен с входом младших

30 разрядбЬ адреса первого блока памяти, выход которого подключен к информационному входу третьего промежуточного регистра, выходы разрядов которого соединены с входами старших

35 разрядов адреса пятого блока памяти, младшие разряды входа адреса которого соединены с выходом четвертого промежуточного регистра, информационный вход которого соединен с вы40 ходом старших разрядов второго блока памяти, выход пятого блока памяти соединен с информационным входом регистра порядка результата, выход которого является выходом порядка

45 результата устройства, выход регист- ;ра мантиссы результата является выходом мантиссы результата устройства, входы синхронизации триггера знака .мантиссы основания степени, регист50 ра порядка основания степени, триггера, четырех промежуточных регистров, триггера знака мантиссы, результата и рё гистра порядка результата подклю 1ены к входу синхронизации

55 устройства.

ному интервалу приближения и вычисляемой функции у х. Блок 9 памяти имеет большое количество адресных входов (п+1), но управляющие слова меняются только при переходе от интервала к интервалу.

Р1з-за большого количества адресных входов блок 9 памяти целесообразно реализовать не на ПЗУ, а на программируемой логической матрице (например, при , для реализации блока 9 памяти достаточно использовать 1 микросхему 556PT1J .

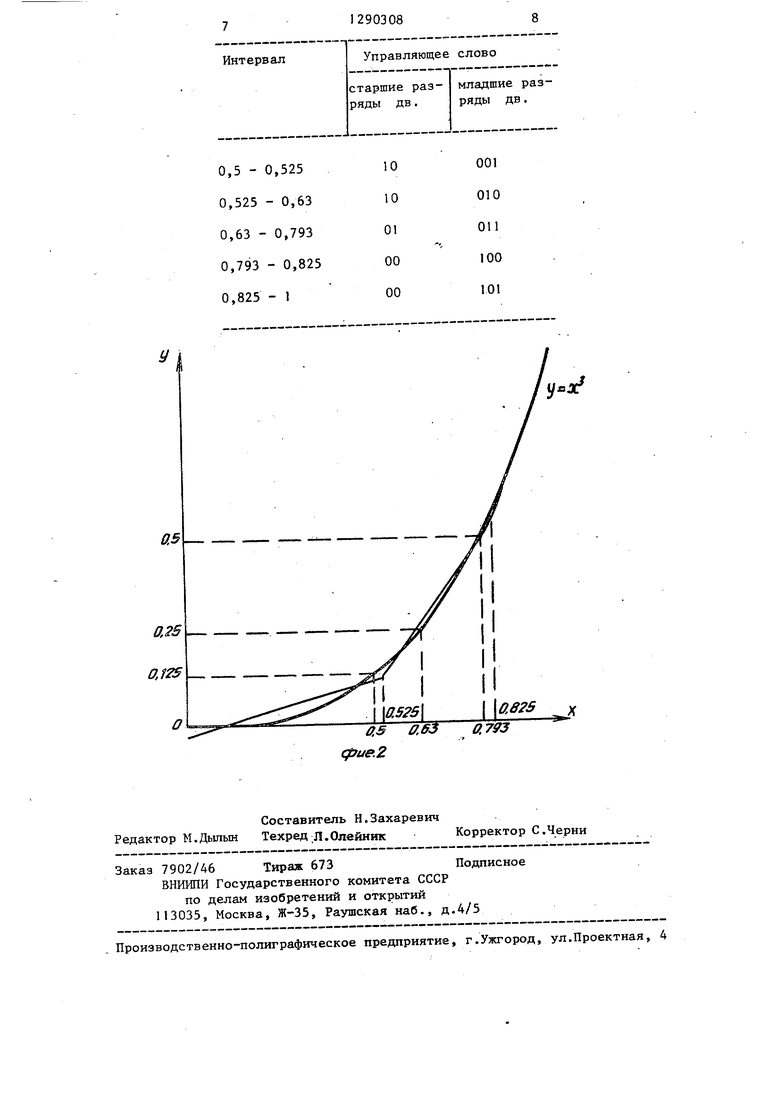

Например, для функции у х при вычислении с точностью 0,025 управляющая информация в блоке 8 ,. памяти (фиг,2j представлена в таблице.

Устройство работает следующим образом.

В первом такте работы устройства в регистр 2 показателя степени поступает значение показателя степени с. В том же такте в триггер 5 знака мантиссы основания степени, регистр 6 порядка основания степени и регистр 1 мантиссы основания степени, поступают соответственно значения знака мантиссы основания степени, порядка основания степени х и мантиссы основания степени х. При помощи элемента и 7 образуется значени знака, мантиссы ,результата. Если показатель степени с является чет- ным числом, т.е. младший разряд равен нулю, то на выходе элемента И 7 (мантисса результата положитель- на), если с нечетное число, то через элемент И 7 с выхода триггера 5 зна- ка мантиссы основания степени пропускается старое значение знака., На выходе блока 8 памяти формируется значение х -с. При этом если значение х представляет собой зна- чение порядка со смещением, то на выходе блока 8 памяти будет значение

В устройстве реализован принцип совмещения операций во времени. Таким образом, -за счет того, что пред(х - р) с, где р - величина смещения.

Из блока 9 памяти по адресу, который

определяется значением показателя сте-50 устройство работает в формате с плавающей запятой, диапазон входных чисел значительно расширен. Диапазон входных чисел равен (так как мантисса нормализована)

пени и значением мантиссы основания степени, выбирается управляющее слово, В

зависимости от того,

- 1

интервале 2 , ), . .., 2

в каком

0

находится число х , в старших разрядах управляющего слова будет значение смещения порядка с -1 , с-2,..,,, 1,0 соответственно. В зависимости от того, в какой из интервалов ап

90308 4

проксимации попадает число х и в зависимости от значения показателя степени с в младших разрядах управляющего слова будет находится 2 значение номера интервала, являющееся адресом для выборки параметров аппроксимации А и В. Константа В выбирается из блока 10 памяти. На выходе умножителя 4 формируется зна- Ш чение х В.

Во втором такте значение х В запоминается в регистре 4, ние смещения порядка - в регистре 16, з-начение ( р) с - в регистре J5 15, значение знака мантиссы основания степени - в триггере 17, значение номера интервала аппроксимации - в регистре 13. С выхода блока 12

памяти снимается значение порядка 20 результата

(х,-р) с

+ с + р.

+ р, . . . , ()

с +

(

ч с т.е. значение порядка результата при необходимости формируется со смещением. С выхода блока II памяти снимается значение константы А, а на выходе сумматора 18 формируется приближенное значение мантиссы А + +В х .Одновременно в регистры 2,6 и 1 и триггер 5 заносятся новые значения основания и показателя степени и формируются новые значения знака мантиссы, произведение порядка на показатель степени, смещение по- рядка, номера интервала и выбирается новая константа В.,

В третьем такте в триггер i 9 заносится значение знака мантиссы ре- зуль ата, а в регистры 20 и 3 - значения порядка и мантиссы результата.. Одновременно в регистры 2,6 и и триггер 5 заносятся новые значения показателя и основания степени.

В устройстве реализован принцип совмещения операций во времени. Таким образом, -за счет того, что пред55

s, 2-.

где га - разрядность порядка; и - разрядность мантиссы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления корня | 1985 |

|

SU1339556A1 |

| Устройство для вычисления корня третьей степени | 1985 |

|

SU1288695A1 |

| Устройство для вычисления корня @ -степени | 1986 |

|

SU1381494A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1191908A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Устройство для извлечения корня третьей степени | 1989 |

|

SU1656531A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| Устройство для вычисления синуса | 1986 |

|

SU1319025A1 |

| Преобразователь комплексных сигналов | 1983 |

|

SU1104525A1 |

Изобретение относится к вычислительной технике, предназначено для использования в вычислительных машинах и обеспечивает обработку данных в формате с плавающей запятой. Устройство содержит регистр 1 мантиссы основания степени., регистр 2 показателя степени, регистр 3 мантиссы результата, умножитель 4, триггер 5 знака мантиссы основания степени, регистр 6 порядка основания степени, элемент И 7, блоки памяти. . 8 - 12,промежуточные регистры 13 -16, триггер 17, сумматор 18, триггер 1У знака мантиссы результата, регистр 20 порядка результата. Мантисса основания степени, порядок основания степени, показатель степени, знак мантиссы основания степени подаются на входы 21, 26, 22 и 24 устройства соответственно. На выходах 25, 27 и 28 формируются знак мантиссы, порядок и мантисса результата соответственно. Тактирование осуществляется по входу 23 устройства. Вычисления проводятся на основе сегментной аппроксимации степенных функций . 2 Ш1. (Л J гг к ьо о о bo о СХ)

Составитель Н.Захаревич Редактор М.Дылын Техред Л.Олейник Корректор С.Черни

Заказ 7902/46 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Уокерли Дж | |||

| Архитектура и программирование микроэвм | |||

| - М.: Мир, 1984, книга 1, с.148 | |||

| Устройство для возведения в степень | 1983 |

|

SU1087990A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ,(54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ | |||

Авторы

Даты

1987-02-15—Публикация

1985-07-08—Подача