импульсов, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входами сдвига регистров сдвига группы, с синхровходом логического анализатора и входом сдвига регистра сдвига8 выход генератора тактовых импульсов соединен со счетньм входом счетчика, информационные выходы которого соединены с соответствующими информационными входами дешифратора j n выходов которого соединены с входами записи соответствующих регистров сдвИТга второй группы, (п+1)-й выход дешифратора соединен с входами останова блока ввода и генератора тактовых импульсов, И)-и выход дешифратора соединен с вторым входом второго элемента ИЛИ, выход первого элемента ИЛИ соединен с входом элемента НЕ, выход которого соединен с вторыми информационными входами сумматоров по модулю два группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1307459A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ, содержащее блок управления, логический анализатор, блок индикации, генератор тестов, блок свертки по модулю два, сумматор по модулю два,,регистр сдвига, группу сумматоров по модулю два, группу регистров сдвига, причем выходы сумматоров по модулю два группы соединены с соответствующими информационными входами блока свертки по модулю два, информационный выход которого соеди-. нен с первым информационным входом сумматора по модулю два, группа информационных входов которого соединена с соответствующими выходами регистра сдвига, информационный вход которого соединен с выходом сумматора по модулю два, информационные входы блока индикации соединены с соответствующими выходами регистра сдвига, информационные входы регистров сдвига группы соединены с соответствующими выходами генератора тестов и сумматоров по модулю два группы, группы информационных входов которых соединены с п-1 выходами соответствующих регистров сдвига группы, за исключением выходов п -х разрядов (п - число тестовых слов ), которые соединены с первыми информационными входами соответствующих сумматоров по модулю два группы, с соответствующими входами - выходами контролируемого цифрового узла и с соответствую1ЦИМИ информационными входами логического анализатора, вход пуска устройства соединен с входом пуска блока управления и генератора тестов, о т-- личающееся тем, что, с сл целью расширения функциональных воз.можностей за счет контроля цифровых блоков с неоднократной сменой входоввькодов в процессе контроля, оно содержит в блоке управления генератор пачки импульсов, два элемента ИЛИ, элемент НЕ, а генератор тестов содержит блок ввода, генератор тактосо со вых импульсов, счетчик, дешифратор, группу регистров, причем выходы регистров группы соединены с соответствующими информационными входами блока свертки по модулю два, выходом сумматора по модулю два группы и информационными входами регистров сдвига группы и являются выходами генератора тестов, вход пуска генератора тестов соединен с входами старта блока ввода и генератора тактовых импульсов, входом сброса«счетчика и первым входом первого элемента ИЛИ, второй вход которого соединен с входом контроля устройства и с входом старта генератора пачки

Изобретение относится к цифровой вычислительной технике и может быть использовано для поиска неисправностей в сложных цифровых схемах автоматики и вычислительной техники.

Цель изобретения - расширение функциональных возможностей за счет контроля цифровьпс блоков с неоднократной сменой входов-выходов в процессе контроля и повышение коэффициента использования оборудования.

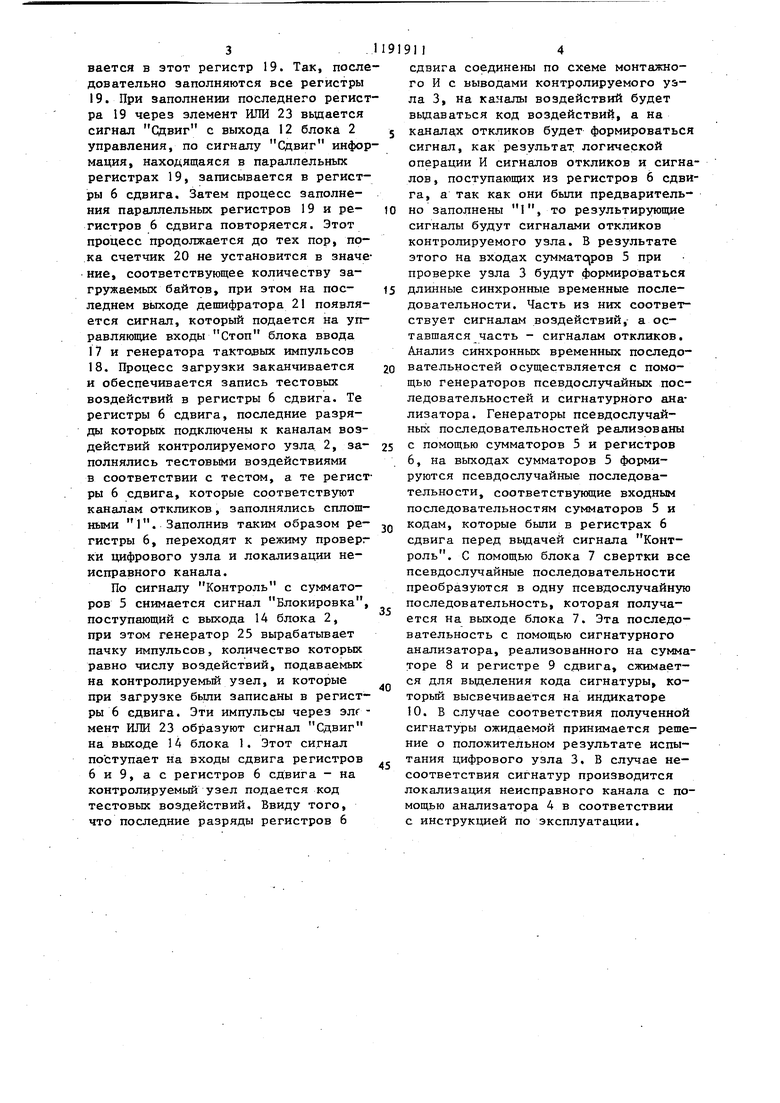

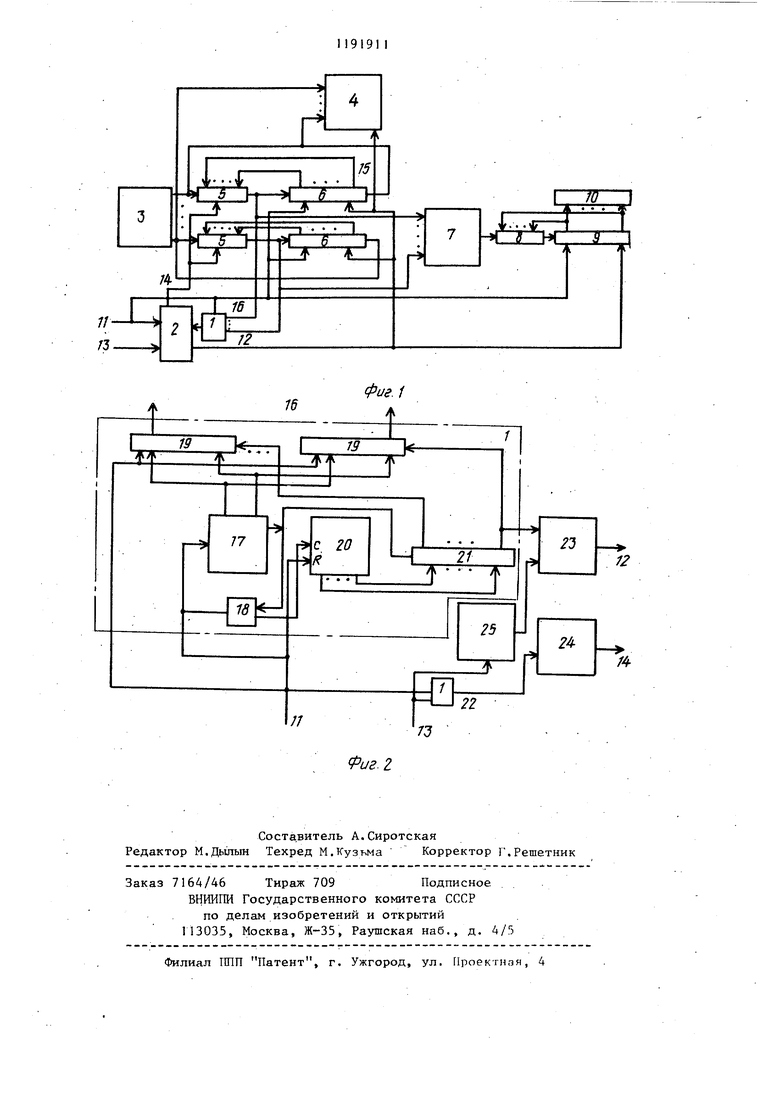

На фиг,1 изображена функциональная схема устройства для контроля цифровых узлов; на фиг.2 - схема генератора тестов и блока управления.

Устройство содержит генератор 1 тестовJ блок 2 управления, контролируемый цифровой узел 3, логический анализатор 4, группу сумматоров 5 по модулю два первую группу регистров 6 сдвига, блок-7 свертки по мо-. дулю двЕа сумматор 8 по модулю два, регистр 9 сдвига, блок 10 индикации, вход 11 установки устройства, выход 12 сдвига блока управления, вход 13 режима контроля устройства, выход 14 блокировки блока управления, выходы .15 йп-х разрядов регистров сдвига первой группы, выходы 16 генератора тестов.

Генератор тестов содержит блок 17 ,ввода,генератор 18 тактовых импульсов, вторую группу регистров 19 сдвига, счетчик 20, дешифратор 21.

Блок управления содержит первый элемент ИЛИ 22, второй элемент ИЛИ 23, элемент НЕ 24, генератор 25 пачек импульсов ,

В схеме в качестве блока 17 ввода и генератора тактовых импульсов 18 может быть использован фотосчитыва- тель, так как при считывании очередного байта на синхронизирующем выходе фотосчитывания появляется импульс синхронизации. Может быть использован любой серийно- вьтускаемый анализатор, например анализатор логический шестнадцатиканальный.

Устройство для контроля цифровых узлов работает в еледую1цих режимах: загрузка регистров сдвига, проверка цифрового узла и локализации неисправного канала.

Работа устройства начинается по Установка, при этом обеспечивается установка в начальное состояние регистров 6 и 9, с выхода

14 блока 2 на сумматоры 5 поступает сигнал Блокировка, который вырабатывается инвертором 24 при отсутствии сигнала Контроль. Сигнал Блокировка отключает выходы сумматоров

5 от информационных входов регистров. Сигнал Установка также обнуляет счетчик 20 и запускает блок ввода 17 и генератор тактовых импульсов 18 по управляющим входам Старт. При этом

при считывании очередного байта на вьпсоде генератора тактовых испульсов появляется импульс, который изменяет На единицу значение счетчика 20, на соответствующем выходе дешифратора 21 появляется сигнал, который подается на управляющий вход записью соответствующего 8-разрядного параллельного регистра 19, и этот байт записывается в этот регистр 19. Так, после довательно заполняются все регистры 19. При заполнении последнего регисг ра 19 через элемент ИЛИ 23 вьщается сигнал Одвиг с выхода I2 блока 2 управления, по сигналу Сдвиг инфор нация, находящаяся в параллельных регистрах 19, записывается в регистры 6 сдвига. Затем процесс заполнения параллельных регистров 19 и регистров 6 сдвига повторяется. Этот процесс продолжается до тех пор, пока счетчик 20 не установится в значение, соответствующее количеству загружаемых байтов, при этом на последнем выходе депшфратора 21 появляется сигнал, который подается на управляющие входы Стоп блока ввода 17 и генератора тактовых импульсов 18. Процесс Загрузки заканчивается и обеспечивается запись тестовых воздействий в регистры 6 сдвига. Те регистры 6 сдвига, последние разряды которых подключены к каналам воздействий контролируемого узла 2, заполнялись тестовьми воздействиями в соответствии с тестом, а те регистры 6 сдвига, которые соответствуют каналам откликов, заполнялись сплошными 1. Заполнив таким образом регистры 6, переходят к режиму проверг ки цифрового узла и локализации неисправного канала.

По сигналу Контроль с сумматоров 5 снимается сигнал Блокировка, поступающий с выхода 14 блока 2, при этом генератор 25 вырабатывает пачку импульсов, количество которых равно числу воздействий, подаваемых на контролируемый узел, и которые при загрузке были записаны в регистры 6 сдвига. Эти импульсы через элг мент ИЛИ 23 образуют сигнал Сдвиг на выходе 14 блока 1. Этот сигнал поступает на входы сдвига регистров 6 и 9, ас регистров 6 сдвига - на контролируемый узел подается код тестовых воздействий. Ввиду того, что последние разряды регистров 6

1919114

сдвига соединены по схеме монтажного И с выводами контролируемого уэла 3, на каз1алы воздействий будет вьщаваться код воздействий, а на 5 каналах откликов будет формироваться сигнал, как результат, логической операции И сигналов откликов и сигналов, поступающих из регистров 6 сдвига, а так как они быпи предварительно заполнены 1, то результирующие сигналы будут сигналами откликов контролируемого узла. В результате этого на входах суммато(ров 5 при проверке узла 3 будут формироваться

15 длинные синхронные временные последовательности. Часть из них соответствует сигналам воздействий,- а оставшаяся часть - сигналам откликов. Анализ синхронных временных последовательностей осуществляется с помощью генераторов псевдослучайных последовательностей и сигнатурного ана лизатора. Генераторы псевдослучайных последовательностей реализованы

25 с помощью сумматоров 5 и регистров 6, на выходах сумматоров 5 формируются псевдослучайные последовательности, соответствующие входным последовательностям сумматоров 5 и

2Q кодам, которые быпи в регистрах 6 сдвига перед вьщачей сигнала Контроль. С помощью блока 7 свертки все псевдослучайные последовательности преобразуются в одну псевдослучайную последовательность, которая получается на выходе блока 7. Эта последовательность с помощью сигнатурного анализатора, реализованного на сумматоре 8 и регистре 9 сдвига, сжимает- ся для выделения кода сигнатуры, который высвечивается на индикаторе 10. В случае соответствия полученной сигнатуры ожидаемой принимается решение о положительном результате испы- 2 тания цифрового узла 3. В случае несоответствия сигнатур производится локализация неисправного канала с помощью анализатора 4 в соответствии с инструкцией по эксплуатации.

фиг. /

| Устройство для контроля многовы-ХОдНыХ цифРОВыХ узлОВ | 1979 |

|

SU817721A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пестряков В.Б | |||

| и др | |||

| Шумопрдобные сигналы в системах передачи информации | |||

| - М | |||

| : Сов | |||

| радио, 1973 | |||

| Каган В.М | |||

| и Мкртумян И.Б | |||

| Основы эксплуатации ЭВМ | |||

| - М.: Энергоатом, 1983. | |||

Авторы

Даты

1985-11-15—Публикация

1984-06-25—Подача