Изобретение относится к вычислительной, технике, в частности к интегрирующим устройствам, и может быть использовано в цифровых системах управления и системах обработки данных.

Цель изобретения - сокращение оборудования.

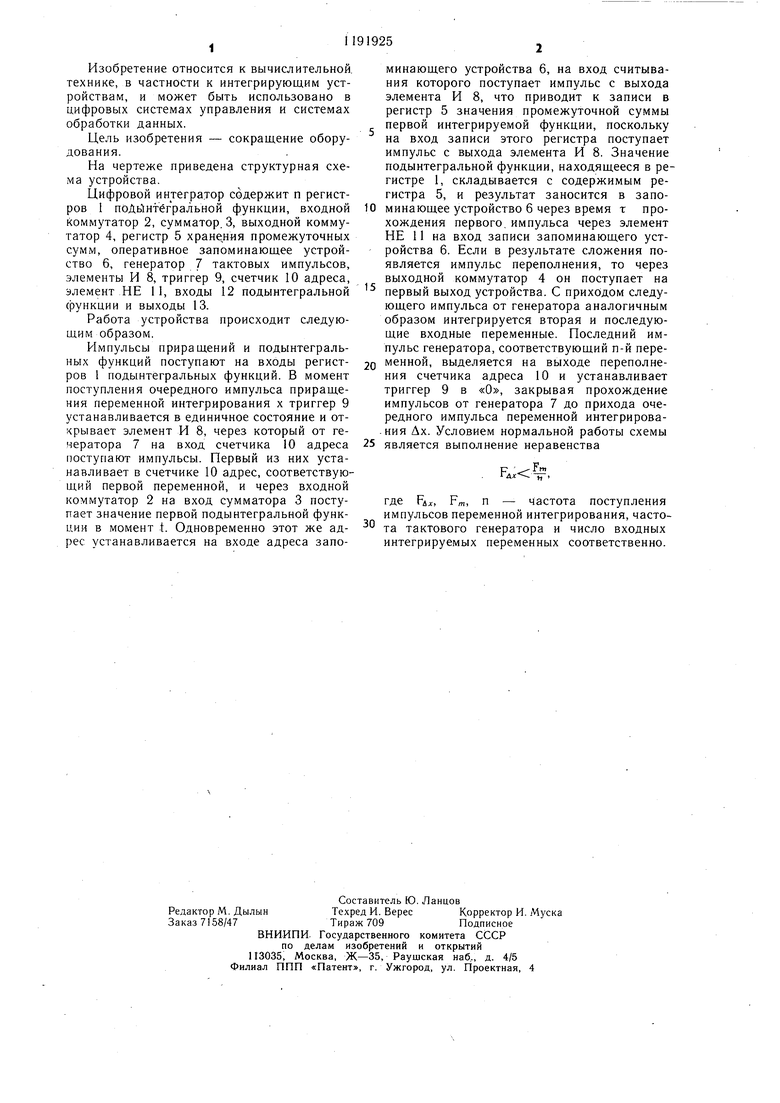

На чертеже приведена структурная схема устройства.

Цифровой интегратор содержит п регистров I поДь1нтёгральной функции, входной коммутатор 2, сумматор, 3, выходной коммутатор 4, регистр 5 хранения промежуточных сумм, оперативное запоминающее устройство 6, генератор 7 тактовых импульсов, элементы И 8, триггер 9, счетчик 10 адреса, элемент НЕ II, входы 12 подынтегральной функции и выходы 13.

Работа устройства происходит следующим образом.

Импульсы приращений и подынтегральных функций поступают на входы регистров 1 подынтегральных функций. В момент поступления очередного импульса приращения переменной интегрирования х триггер 9 устанавливается в единичное состояние и открывает элемент И 8, через который от генератора 7 на вход счетчика 10 адреса поступают импульсы. Первый из них устанавливает в счетчике 10 адрес, соответствующий первой переменной, и через входной коммутатор 2 на вход сумматора 3 поступает значение первой подынтегральной функции в момент t. Одновременно этот же адрес устанавливается на входе адреса запоминающего устройства 6, на вход считывания которого поступает импульс с выхода элемента И 8, что приводит к записи в регистр 5 значения промежуточной суммы первой интегрируемой функции, поскольку на вход записи этого регистра поступает импульс с выхода элемента И 8. Значение подынтегральной функции, находящееся в регистре 1, складывается с содержимым регистра 5, и результат заносится в запоминающее устройство 6 через время т прохождения первого, импульса через элемент НЕ 11 на вход записи запоминающего устройства 6. Если в результате сложения появляется импульс переполнения, то через выходной коммутатор 4 он поступает на

первый выход устройства. С приходом следующего импульса от генератора аналогичным образом интегрируется вторая и последующие входные переменные. Последний импульс генератора, соответствующий п-й переQ менной, выделяется на выходе переполнения счетчика адреса 10 и устанавливает триггер 9 в «О, закрывая прохождение импульсов от генератора 7 до прихода очередного импульса переменной интегрирова-ния Дх. Условием нормальной работы схемы

является выполнение неравенства

Р

. ,

где Fi, Fm, п - частота поступления импульсов переменной интегрирования, частота тактового генератора и число входных интегрируемых переменных соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство для сбора информации | 1985 |

|

SU1262554A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Узловой элемент цифровой сетки для решения краевых задач теории поля | 1985 |

|

SU1283788A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Устройство отсчета интервалов времени | 1982 |

|

SU1103228A1 |

| Автокоррелятор | 1990 |

|

SU1833894A1 |

ЦИФРОВОЙ ИНТЕГРАТОР, содержаший группу регистров подынтегральной функции, сумматор, регистр хранения промежуточных сумм, генератор тактовых импульсов и входной коммутатор, причем информационные входы регистров подынтегральной функции являются входами подынтегральной функции интегратора, выходы регистров подынтегральной функции соединены с информационными входами входного коммутатора, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом регистра хранения промежуточных сумм, отличающийся тем, что, с целью сокращения оборудования, он SrF.f) 13 содержит выходной коммутатор, оперативное запоминаюшее устройство, счетчик адреса, элемент НЕ, элемент И и триггер, причем выход результата сумматора соединен с информационным входом оперативного запоминающего устройства, выход которого соединен с информационным входом регистра хранения промежуточных сумм, вход записи которого соединен с входом чтения оперативного запоминающего устройства, со счетным входом счетчика адреса, с выходом элемента И и через элемент НЕ с входом записи оперативного запоминающего устройства, адресный вход которого соединен с управляющими входами входного и выходного коммутаторов и с информационным выходом счетчика адреса, выход переполнения которого соединен с входом установки в jg «О триггера, вход установки в «1 которого является входом переменной интег- СЛ рирования интегратора, выход триггера соединен с первым входом элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, выход переноса сумматора соединен с информационным входом выходного коммутатора, выходы которого являются выходами интегратора.

| Гладкий В | |||

| С | |||

| Вероятностные вычислительные модели | |||

| - М.; Наука, 1973, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

| Вычислительные машины непрерывного действия | |||

| - М.: Высшая школа, 1964, с | |||

| Устройство для телефонирования по проводам токами высокой частоты | 1921 |

|

SU374A1 |

Авторы

Даты

1985-11-15—Публикация

1983-07-22—Подача