Изобретение относится к запоминаю иим устройствам и может быть использовано при создании полупроводниковых больших интегральных схем памяти (БИС памяти).

,ель изобретения - упрощение уст)ойства.

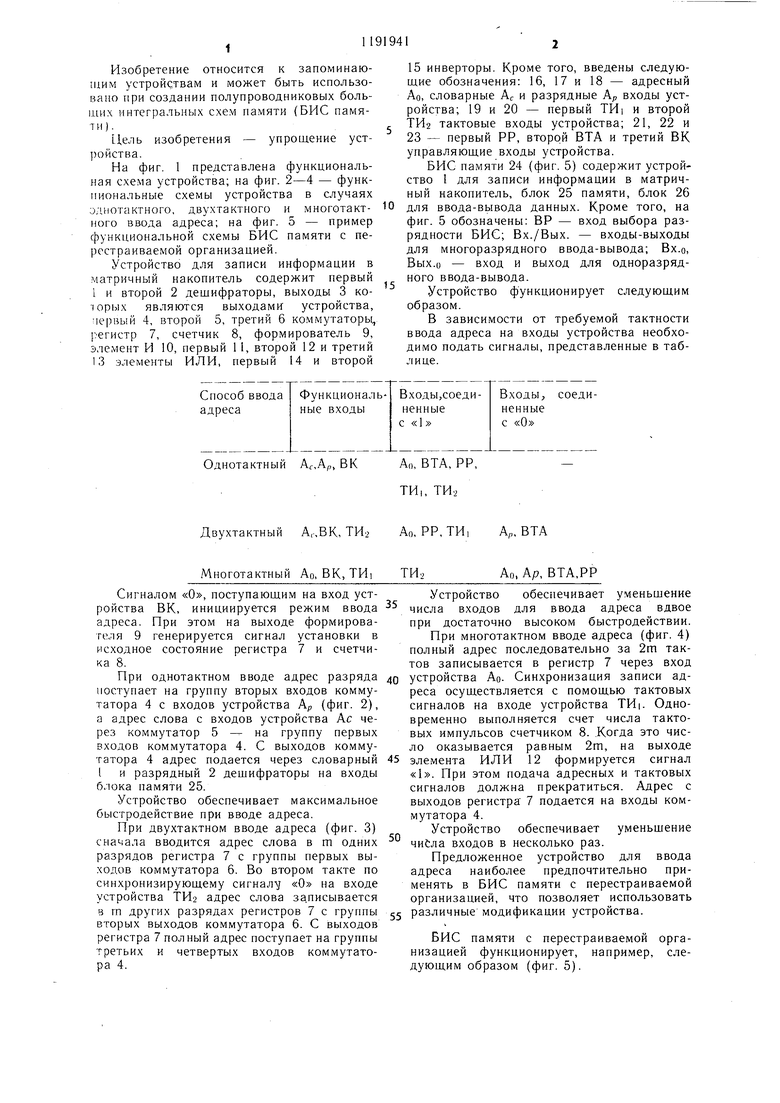

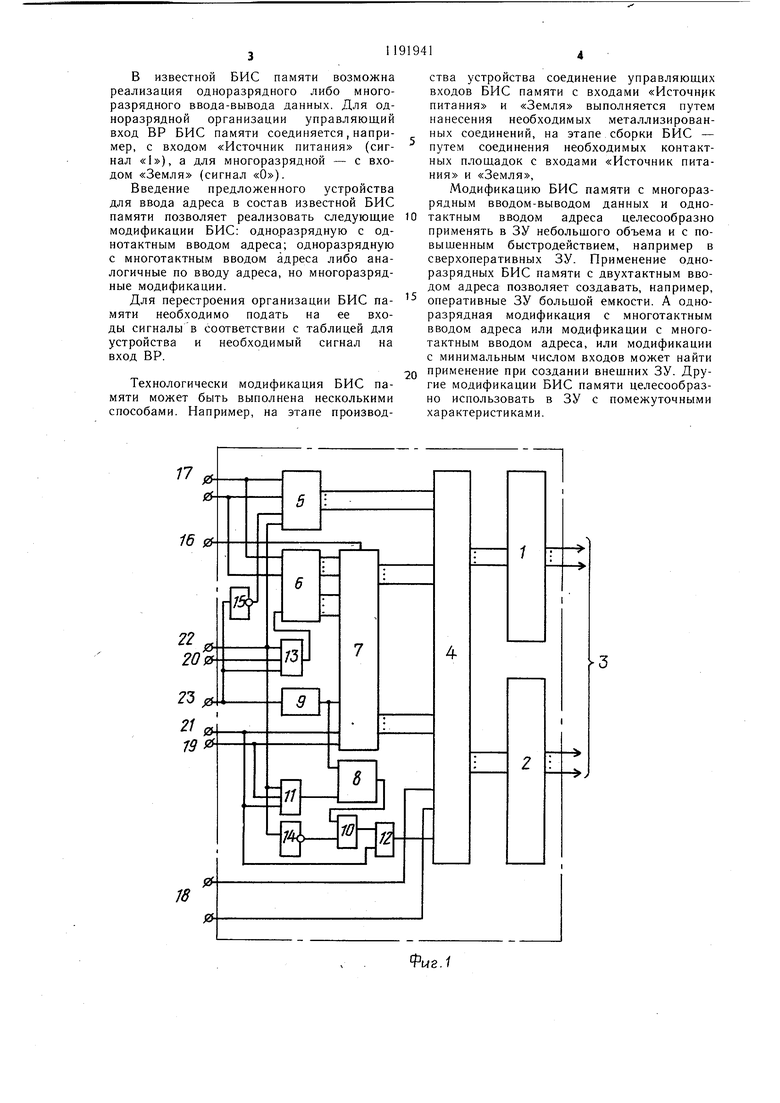

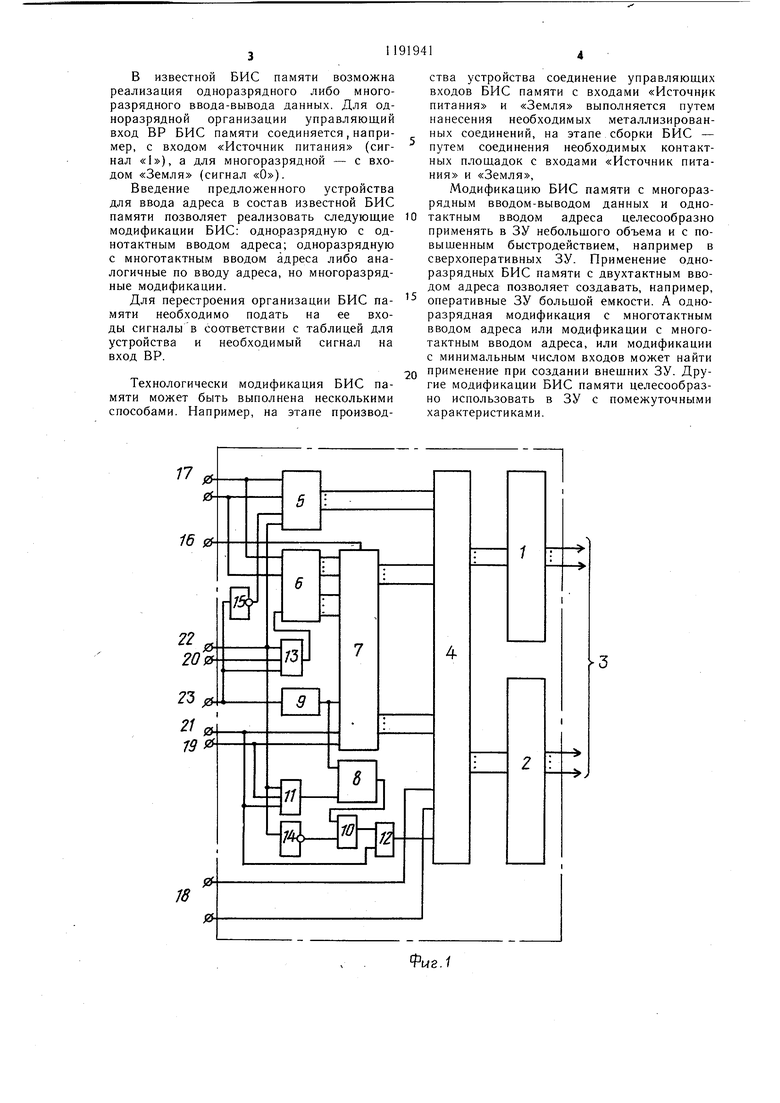

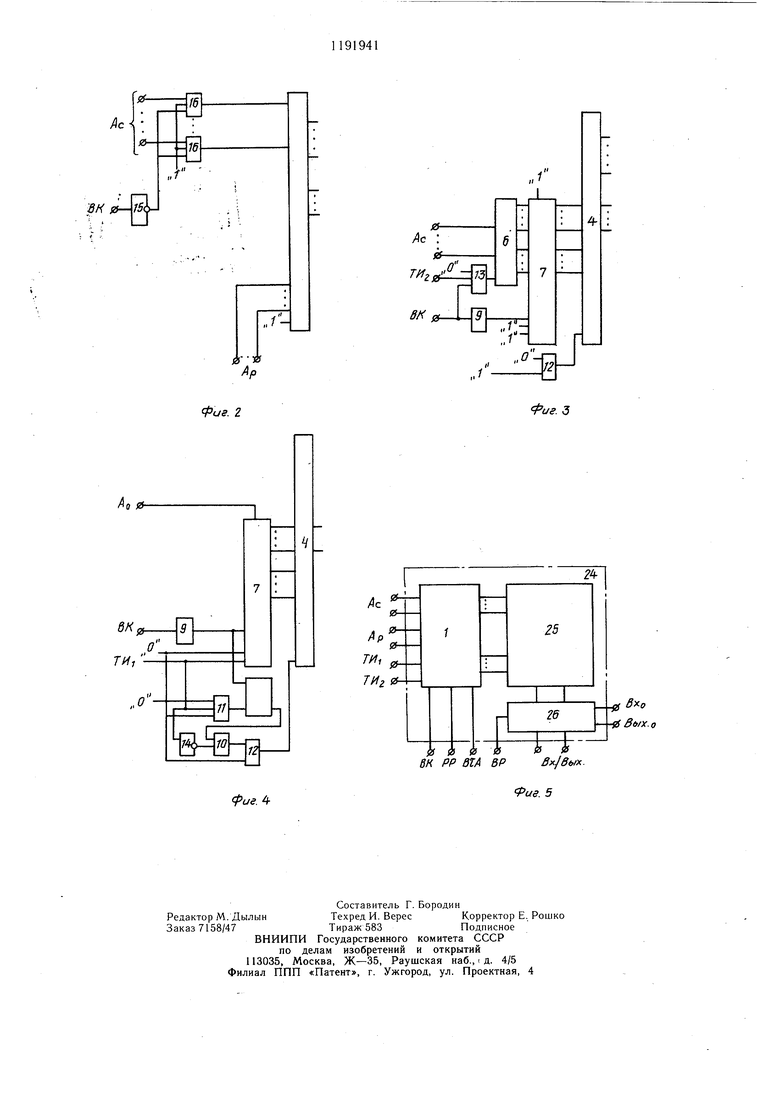

На фиг. 1 представлена функциональная схема устройства; на фиг. 2-4 - функциональные схемы устройства в случаях элнотактного, двухтактного и многотактного ввода адреса; на фиг. 5 - пример функциональной схемы БИС памяти с перестраиваемой организацией.

Устройство для записи информации в матричный накопитель содержит первый 1 и второй 2 дешифраторы, выходы 3 которых являются выходами устройства, первый 4, второй 5, третий 6 коммутаторы, регистр 7, счетчик 8, формирователь 9, элемент И 10, первый 11, второй 12 и третий 13 элементы ИЛИ, первый 14 и второй

15 инверторы. Кроме того, введены следующие обозначения: 16, 17 и 18 - адресный АО, словарные Ас и разрядные Ар входы устройства; 19 и 20 - первый THi и второй ТИ2 тактовые входы устройства; 21, 22 и 23 - первый РР, второй ВТА и третий ВК управляющие входы устройства.

БИС памяти 24 (фиг. 5) содержит устройство 1 для записи информации в матричный накопитель, блок 25 памяти, блок 26 для ввода-вывода данных. Кроме того, на фиг. 5 обозначены: ВР - вход выбора разрядности БИС; Вх./Вых. - входы-выходы для многоразрядного ввода-вывода; BX.Q, Вых.о - вход и выход для одноразрядного ввода-вывода.

Устройство функционирует следующим образом.

В зависимости от требуемой тактности ввода адреса на входы устройства необходимо подать сигналы, представленные в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Многоканальное устройство для ввода-вывода аналоговой информации | 1988 |

|

SU1564606A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1982 |

|

SU1104519A1 |

| Программируемый контроллер | 1989 |

|

SU1647594A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Запоминающее устройство с последовательным доступом | 1982 |

|

SU1070606A2 |

УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ В МАТРИЧНЫЙ НАКОПИТЕЛЬ, содержащее первый и второй дешифраторы, выходы которых являются выходами устройства, элементы И, ИЛИ, инверторы, отличающееся тем, что, с целью упрощения устройства, оно содержит коммутаторы, счетчик, регистр, формирователь, причем выходы первой и второй групп первого коммутатора соединены с входами соответственно первого и второго дешифраторов, входы первой группы первого коммутатора являются адресными входами первой группы устройства, входы второй группы. соединены с выходами регистра, а входы третьей -группы - с выходами второго коммутатора, входы группы которого соединены с входами группы третьего коммутатора и являются адресными входами второй группы устройства, выходы третьего коммутатора соединены с выходами группы регистра, один управляющий вход счетчика соединен с выходом формирователя и первым управляющим входом регистра, а другой - с выходом первого элемента ИЛИ, выход счетчика соединен с первым входом элемента И, второй вход которого соединен с выходом первого инвертора, а выход соединен с первым входом второго элемента ИЛИ, выход которого соединен с управляющим входом первого коммутатора, а второй вход соединен с вторым управляющим входом регистра, входом первого элемента ИЛИ и является первым управляющим входом устройства, третий управляющий вход регистра соединен с вторым входом первого элемента ИЛИ и является вторым управляющим входом устройства, вход первого инвертора соединен с треть Q им входом первого элемента ИЛИ, первым (Л управляющим входом второго коммутатора, первым входом третьего элемента ИЛИ и является третьим управляющим входом устройства, вход формирователя соединен с вторым входом третьего элемента ИЛИ, входом второго инвертора и является четвертым управляющим входом устройства, выход второго инвертора соединен с вторым управляющим входом второго коммутатора, выход третьего элемента ИЛИ соединен со с управляющим входом третьего коммутатора, а третий вход третьего элемента ИЛИ со является пятым управляющим входом 4: устройства , информационный вход регистра является адресным входом устройства.

Однотактный А,,Ар, ВКАО, ВТА, РР,

Двухтактный А,.,ВК, ТИ2 АО, РР,ТИ1 А,,, ВТА

Многотактный АО, ВК, THi ТИ2

Сигналом «О, поступающим на вход устройства ВК, инициируется режим ввода адреса. При этом на выходе формирователя 9 генерируется сигнал установки в исходное состояние регистра 7 и счетчика 8.

При однотактном вводе адрес разряда поступает на группу вторых входов коммутатора 4 с входов устройства Ар (фиг. 2), а адрес слова с входов устройства Ас через коммутатор 5 -- на группу первых входов коммутатора 4. С выходов коммутатора 4 адрес подается через словарный I и разрядный 2 дешифраторы на входы блока памяти 25.

Устройство обеспечивает максимальное быстродействие при вводе адреса.

При двухтактном вводе адреса (фиг. 3) сначала вводится адрес слова в ш одних разрядов регистра 7 с группы первых выходов коммутатора 6. Во втором такте по синхронизирующему сигналу «О на входе устройства ТИ2 адрес слова записывается в гп других разрядах регистров 7 с группы вторых выходов коммутатора 6. С выходов регистра 7 полный адрес поступает на группы третьих и четвертых входов коммутатора 4.

ТИ|, ТИ2

АО, Ау9, ВТА,РР

Устройство обеспечивает уменьщение

числа входов для ввода адреса вдвое при достаточно высоком быстродействии.

При многотактном вводе адреса (фиг. 4) полный адрес последовательно за 2гп тактов записывается в регистр 7 через вход устройства АО. Синхронизация записи адреса осуществляется с помощью тактовых сигналов на входе устройства ТИ|. Одновременно выполняется счет числа тактовых импульсов счетчиком 8. .Когда это число оказывается равным 2т, на выходе 5 элемента ИЛИ 12 формируется сигнал «1. При этом подача адресных и тактовых сигналов должна прекратиться. Адрес с выходов регистра 7 подается на входы коммутатора 4.

Устройство обеспечивает уменьшение чиСла входов в несколько раз.

Предложенное устройство для ввода адреса наиболее предпочтительно применять в БИС памяти с перестраиваемой организацией, что позволяет использовать 5 различные модификации устройства.

БИС памяти с перестраиваемой организацией функционирует, например, следующим образом (фиг. 5).

В известной БИС памяти возможна реализация одноразрядного либо многоразрядного ввода-вывода данных. Для одноразрядной организации управляющий вход ВР БИС памяти соединяется, например, с входом «Источник питания (сигнал «1), а для многоразрядной - с входом «Земля (сигнал «О).

Введение предложенного устройства для ввода адреса в состав известной БИС памяти позволяет реализовать следующие модификации БИС: одноразрядную с однотактным вводом адреса; одноразрядную с многотактным вводом адреса либо аналогичные по вводу адреса, но многоразрядные модификации.

Для перестроения организации БИС памяти необходимо подать на ее входы сигналы в соответствии с таблицей для устройства и необходимый сигнал на вход ВР.

Технологически модификация БИС памяти может быть выполнена несколькими способами. Например, на этапе производства устройства соединение управляющих входов БИС памяти с входами «Источник питания и «Земля выполняется путем нанесения необходимых металлизированных соединений, на этапе сборки БИС - путем соединения необходимых контактных площадок с входами «Источник питания и «Земля,

Модификацию БИС памяти с многоразрядным вводом-выводом данных и одно0 тактным вводом адреса целесообразно применять в ЗУ небольшого объема и с повышенным быстродействием, например в сверхоперативных ЗУ. Применение одноразрядных БИС памяти с двухтактным вводом адреса позволяет создавать, например,

оперативные ЗУ большой емкости. А одноразрядная модификация с многотактным вводом адреса или модификации с многотактным вводом адреса, или модификации с минимальным числом входов может найти

Q применение при создании внешних ЗУ. Другие модификации БИС памяти целесообразно использовать в ЗУ с помежуточными характеристиками.

Pu3. 2

pue. 4

Фиг. J

/IP ТИ, 7Hz

8)0 -4 3er/x.o

Pue. 5

| Патент США № 4293932, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Патент США № 4354256, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1985-11-15—Публикация

1984-03-13—Подача