Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, и может быть использовано в автоматических системах для связи с цифровыми вычислительными устройствами,

.Цель изобретения - повышение функциональной надежности за счет ис- кл5очения сбоев, вызванных кратковременным снятием питания,и за счет фор-Ш тором под воздействием тактовых иммирования выходного кода только после приема достоверной информации.

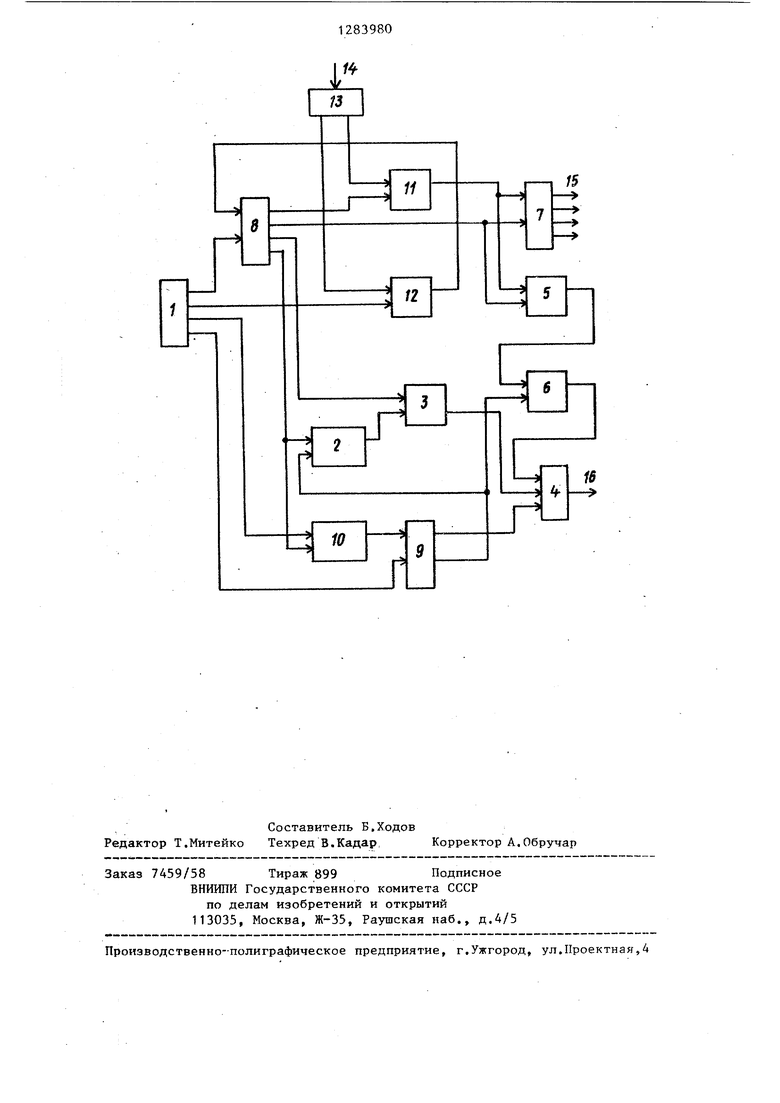

На чертеже представлена функциональная схема преобразователя.

Преобразователь последовательного кода IB параллельный содержит генератор 1 тактовых импульсов,.первый счетчик 2 импульсов, первый триггер 3, первый и вторрй элементы И 4 и 5, второй триггер 6, регистр 7 сдвига,, первый и второй распределители 8 и 9 импульсов, второй счетчик 10 импульсов, третий и четвертый триггеры 11 и 12, формирователь 13 импульсов,

Вход формирователя 13 импульсов является входом 14 преобразователя, выходы регистра 7 - выходами 15 преобразователя, а выход элемента И 4- выходом записи 16 преобразователя.

Преобразователь последовательного кода Е параллельный работает следующим образом.

Двоичный последовательный 32-разрядный код поступает по входу 14 в

пульсов с выхода первого распределителя 8 импульсов происходит продвижение информации, и одновременно информационные импульсы, соответству15 ющие коду 1 , через второй элемент И 5 поступают на счетный вход второго триггера 6, В 32-рязрядном коде,поступающем по входу 14, содержится разряд четности, дополняющий инфор20 мацию до нечетного состояния. Таким образом, при поступлении всех 32-х разрядов кода на выходе второго триггера 6 формируется разрешающий сигнал, если количество единиц в ко25 де было нечетное. После прохождения 32-х импульсов следует пауза, В этот момент времени на вход установки в О второго счетчика 10 сигналы не юступают, а на счетный вход подаются

УЗ

импульсы с выхода генератора 1, Если

зремя между импульсами синхронизации соответствует паузе между словами, на выходе второго счетчика 10 вырабатывается разрешающий сигнал,ко- формирователь импульсов 13, где пре- торый, поступая на второй распредели- образуется в последовательность им- тель импульсов 9, под воздействием пульсов информации и импульсов син- тактовых импульсов с генератора Г выхронизации, 1 мпульс синхронизации поступает на информационный вход четвертого триггера 12 и тактовыми импульсами с генератора 1 записывается в четвертый триггер 12 и с его выхода подается на вход первого распределителя В импульсов, на другой вход которого поступают тактовые импульсы с генератора 1, на входе первого распределителя 8 импульсов формируется последовательность импульсов,.первый из которых, поступая на вход синхронизации третьего триггера 11, записывает информацию в третий триггер 11. Второй импульс с выхода первого распределителя 8 импульсов, поступая на вход регистра 7 сдвига, производит

рабатывает два импульса. Первый импульс поступает на второй вход пер40 вого элемента И 4, если есть разрешение от триггера 3 и триггера 6, формирует сигнал разрешения записи информации, выдаваемой по выходу 16. Второй импульс с выхода второго рас45 пределителя 9 импульсов подается на первый счетчик 2 и триггер 6 и обнуляет их. Триггер 3 формирует сигнал разрешения, .если поступило 32 импульса, если импульсов больше или

50 меньше 32-х, сигнал разрешения приема информации не формируется.

Импульсы на выходах генератора 1 тактовых импульсов формируются в та- последовательный сдвиг информации,по- 55 последовательно, что на кг1ждом ступившей с третьего триггера 11, последующем выходе импульс формиру- Третий импульс поступает на нулевой ется по заднему фронту импульса на вход триггера 3 и переводит его в предшествующем выходе. Причем форми- нулевое состояние, при этом на его рование импульса на первом входе провыходе вырабатывается запрещающий сигнал. Четвертый импульс подается на счетный вход первого счетчика 2, увеличивая его состояние на 1, и на вход установки в О второго счетчика 10, устанавливая его в нулевое состояние, С выхода третьего триггера 1 1 информационные импульсы поступают на вход регистра 7 сдвига, в копульсов с выхода первого распределителя 8 импульсов происходит продвижение информации, и одновременно информационные импульсы, соответству15 ющие коду 1 , через второй элемент И 5 поступают на счетный вход второг триггера 6, В 32-рязрядном коде,поступающем по входу 14, содержится разряд четности, дополняющий инфор20 мацию до нечетного состояния. Таким образом, при поступлении всех 32-х разрядов кода на выходе второго триггера 6 формируется разрешающий сигнал, если количество единиц в ко25 де было нечетное. После прохождения 32-х импульсов следует пауза, В этот момент времени на вход установки в О второго счетчика 10 сигналы не юступают, а на счетный вход подаютс

УЗ

импульсы с выхода генератора 1, Если

рабатывает два импульса. Первый импульс поступает на второй вход пер40 вого элемента И 4, если есть разрешение от триггера 3 и триггера 6, формирует сигнал разрешения записи информации, выдаваемой по выходу 16. Второй импульс с выхода второго рас45 пределителя 9 импульсов подается на первый счетчик 2 и триггер 6 и обнуляет их. Триггер 3 формирует сигнал разрешения, .если поступило 32 импульса, если импульсов больше или

50 меньше 32-х, сигнал разрешения приема информации не формируется.

исходит по заднему фронту импульса на четвертом выходе,

Форм,,ула изобретения

Преобразователь последовательного

кода в параллельный, содержащий генератор тактовых импульсов, первый счетчик импульсов, выход которого соединен с S-входом первого тригге- pa, выход которого соединен с первым входом первого элемента И, второй элемент И, выход которого соединен со счетным входом второго триггера, и регистр сдвига, отличающий с я тем, что, с целью повьппения функциональной надежности преобразователя за счет исключения сбоев, вызванных кратковременным снятием питания, и за счет формирования выходного ко- да только после приема достоверной входной информации, в него введены распределители импульсов, второй счетчик импульсов, третий и четвертый триггеры и формирователь импульсов, первый и второй выходы которого соединены с D-входами третьего и четвертого триггеров соответственно,первый выход первого распределителя импульсов соединен с С-входом третьего триггера, второй выход - с первыми входами регистра сдвига и второго элемента И, третий выход - с R-BXO- дом первого тригера, четвертый выход - со счетным входом первого счетчика импульсов и входом установки ну;я второго счетчика импульсов, пер- ый выход второго распределителя импульсов соединен с входами установки нуля первого счетчика импульсов и второго триггера, выход второго счетчика импульсов соединен с первым входом второго распределителям импульсов, второй выход которого соединен с вторым входом первого элемента И, выход второго триггера соединен с третьим входом первого элемента И, выход третьего триггера соединен с вторыми входами регистра сдвига и второго элемента И, выход четвертого триггера соединен с первым входом первого распределителя импульсов,первый выход генератора тактовых импульсов соединен с вторым входом первого распределителя импульсов, второй выход - с С-входом четвертого триггера, третий выход - со счетным входом второго счетчика импульсов, четвертый выход - с вторым входом второго распределителя импульсов, вход формирователя импульсов является входом преобразователя последовательного кода в параллельный, выходы регистра сдвига являются информационными вы- ходами преобразователя последовательного кода в параллельный, выход первого элемента И является дополнительным выходом записи преобразователя последовательного кода в параллельный.

J/l

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1985 |

|

SU1339896A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Устройство для преобразования широтно-импульсных сигналов в кодоимпульсные сигналы | 1986 |

|

SU1381701A1 |

| Устройство для отображения информации на экране элт | 1977 |

|

SU714446A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

Изобретение относится к вычис- . лительной технике, а именно к устройствам преобразования информации, представленной в веде последователь- ного кода, и может быть использовано в автоматических системах для связи с цифровыми вычислительнь1Ми устройствами. Преобразователь формирует на выходе параллельный код только в том случае, если на его вход поступило заранее заданное количество разрядов последовательного кода и в момент преобразования не было сбоев, вызванных кратковременным снятием питания или эти сбои не при- .вели к искажению входной информации. Данное свойство обеспечивает преобразователю высокую функциональную надежность. Преобразователь последовательного кода в параллельный содержит генератор тактовых импульсов, два счетчика импульсов, два элемента И, четыре триггера, два распределителя импульсов, регистр сдвига и формирователь импульсов. 1 ил.

| Устройство для преобразования последовательного кода в параллельный | 1982 |

|

SU1081639A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь последовательного кода в параллельный | 1979 |

|

SU783789A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-06-27—Подача