4

00

00

о

Изобретение отнссится к вычислительной технике, может быть использовано для преобразования последовательного биполярного кода в па:рая- лельный и является усоверв енствова- кием изобретения по авт«св,№ 1 23 61 3,, Цель изобретения - расвжрение области применения преобразователя путем обеспечения возможности съема информации, начиная с заранее определенного слова.

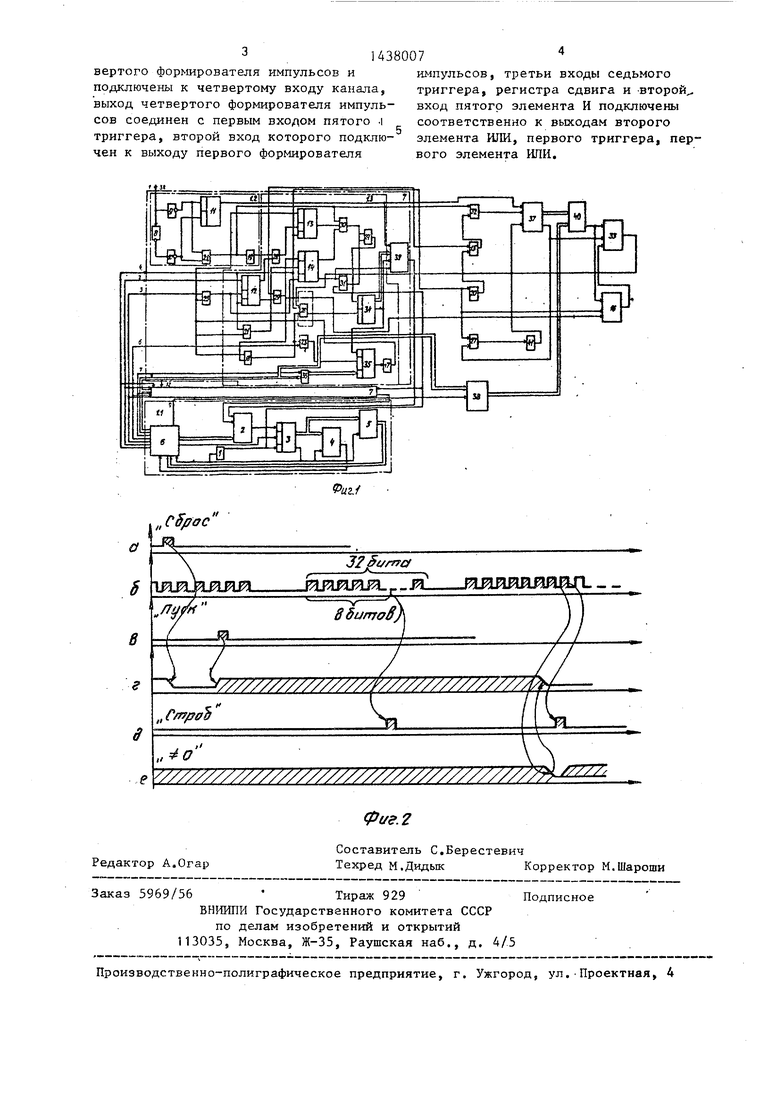

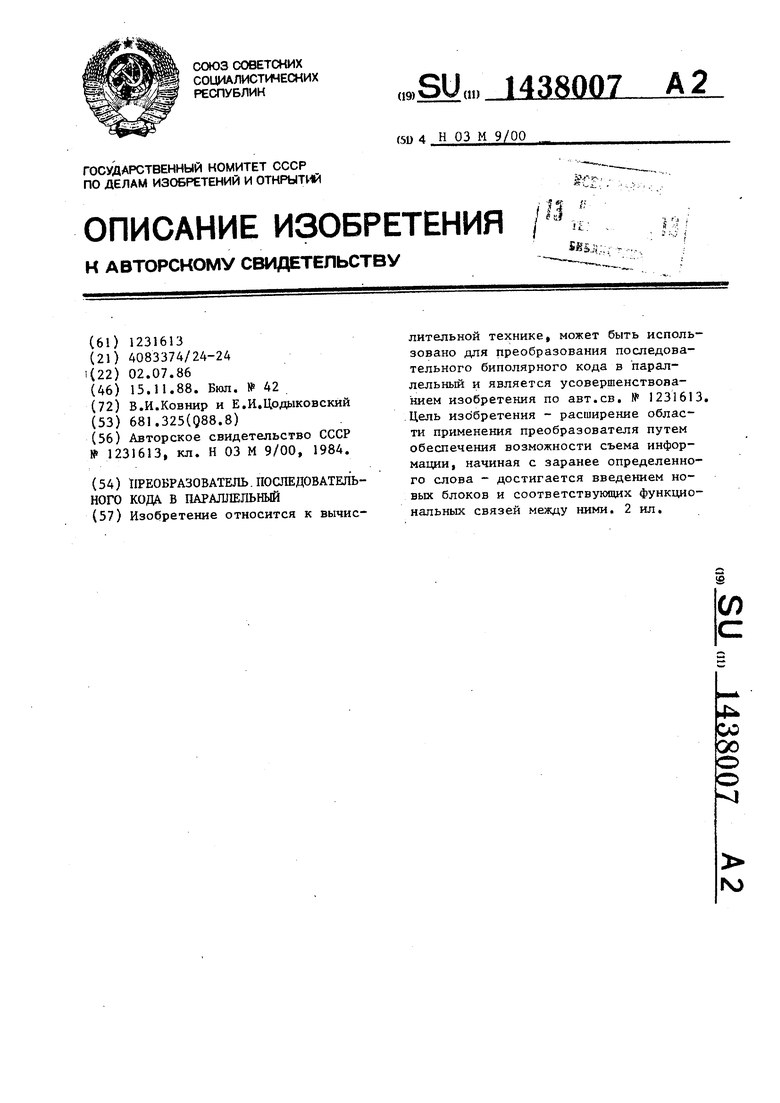

: На фиг,1 представлена бл-ок схема (/ преобразователя последовательного ко- да в параллельный; на фиг.2 - диаг- ; раммы, поясняющие его работу,

Преобразователь последовательного кода в параллельный (фигв) содержит блок 1,1 преобразования и сопряжения управляемый генератор 1, мультиплек- со р 2, регистр 3 сдвига, блок 4 конт роля нечетности, выходной регистр 5, |сонтроллер 6, К каналов 7 преобразования, каждый из которых включает инвертор 8, элементы НЕ 9 и 10, триггеры 11-16, формирователи 17-20 импульсов, элементы ШШ 21-27, элементы И 28-33 j счетчики 34-35;, регистры 36-38, блок 39 оперативной памяти, блок 40 сравне ВИЯ, элемент 41 задержки.

Преобразователь работает следую- 1дим образом,,

После включения питания в контроллере 6 вырабатывается сигнал Сброс (фига2а),, который приводит в исходное состояние все К каналов, в том числе регистр 37; сдвига, триггеры 15 и 16 в каждом из К каналов 5, запирая элементы И 32 и 33.

По команде Пуск , поступающей от элемента ИЛИ 22 (фига2в),, триггер 16 перебрасьшается и открывает элемент И 33, Независимо от команды Пуск . поступают тактовые импульсы (фиг,26) на элементы И 32 и сигнал Пауза на триггер 15б По .приходу первой паузы. Триггер 15 открывает элемент И 32 и тактовые импульсы поступают на сдвиговый регистр 37 синхронно с информацией,, После прихода восьмого им- пульса сдвиговый регистр 37 вырабатывает сигнал строб (фиг,2д)5 который поступает на элемент И 33 а также . через элемент ИЛИ 27 и элемент 4If- задержки на вход Сброс сдвигового регистра 37., Предварительно до команды Пуск в регистр 38 адреса был занесен требуемый адрес словад с которого надо приш1мать информацию в

0 5 0

-

Q п

5

преобразователь. Этот адрес сравнивается в блоке 40 сравнения4. Блок 40 сравнения имеет два выхода: выход V О и выход Если после прохождения восьш импульсов срабатывает сигнал (фиг.2е}, то сигнал Строб проходит через элемент И 33 и обнуляет счетчик 34 адреса через элемент ИГМ 26. Если вырабатывается сигнал 0, то сигнал Строб не проходит через элемент И 33, а триггер 16 сбрасывается и блокирует элемент PI 33 для дальнейшего прохождения импульсов Строб до прихода нового сигнала Пуск,

Таким образом находят н, жное сло- Е .о информащ и, я канал будет принимать информацию аналогично описанному для известного устройства

Формула изобретения

Преобразователь последовательного в параллельный по авт.ев, .. № о тл и ч а ющи и с я тем, что5 с целью расширения области применения преобразователя путем обеспечения возможности считывания инфор- мации, начиная с заранее определенного слова, в каждый из К каналов преоб разования введены пятый и шестой элементы И, пятый и шестой триггеры, регистр сдвига, блок сравнения, чет- вер-пзш формирователь импульсов, седьмой элемент ИЛИ, элемент задержки и регистр адреса, информационный и ттравляющий входы которого подключены соответственно к восьмому и девятому входам канала преобразования, выход подключен к первому входу блока сравнения, выход пятого триггера соединен с первым входом пятого элемента Из выход которого соединен с первым входом регистра сдвига, первый выход которого с вторым входом блока сравнения., выход которо-. го соедикен с первыми входами шестого триггера и шестого элемента И, выход которого подключен к третьему, входу пятого элемента HJMj вькод седьмого элемента ИЛИ через элемент задержки соединен с зто- рьм входом регистра сдвига, второй выход которого соединен с первыг- входом седьмого элемента ИЛИ и третьим входом шестого элемента К, вторые входы седьмого эле мента 1ШИ. и шестого триггера объединены с входом чет . 1438007

вертого формирователя импульсов и импульсов, третьи входы седьмого подключены к четвертому входу канала, триггера, регистра сдвига и .второй выход четвертого формирователя импуль- вход пятого элемента И подключены сов соединен с первым входом пятого .1 соответственно к выходам второго триггера, второй вход которого подклю- элемента ИЛИ, первого триггера, перчен к выходу первого формирователя

вого элемента ИЛИ.

вого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1987 |

|

SU1444814A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Цифровой фазометр | 1988 |

|

SU1511706A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

Изобретение относится к вычислительной технике, может быть использовано для преобразования последовательного биполярного кода в параллельный и является усовершенствованием изобретения по авт.св. № 1231613. .Цель изобретения - расширение области применения преобразователя путем обеспечения возможности съема информации, начиная с заранее определенного слова - достигается введением новых блоков и соответствующих функциональных связей между ними. 2 ил.

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1231613A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-15—Публикация

1986-07-02—Подача