СО

0д

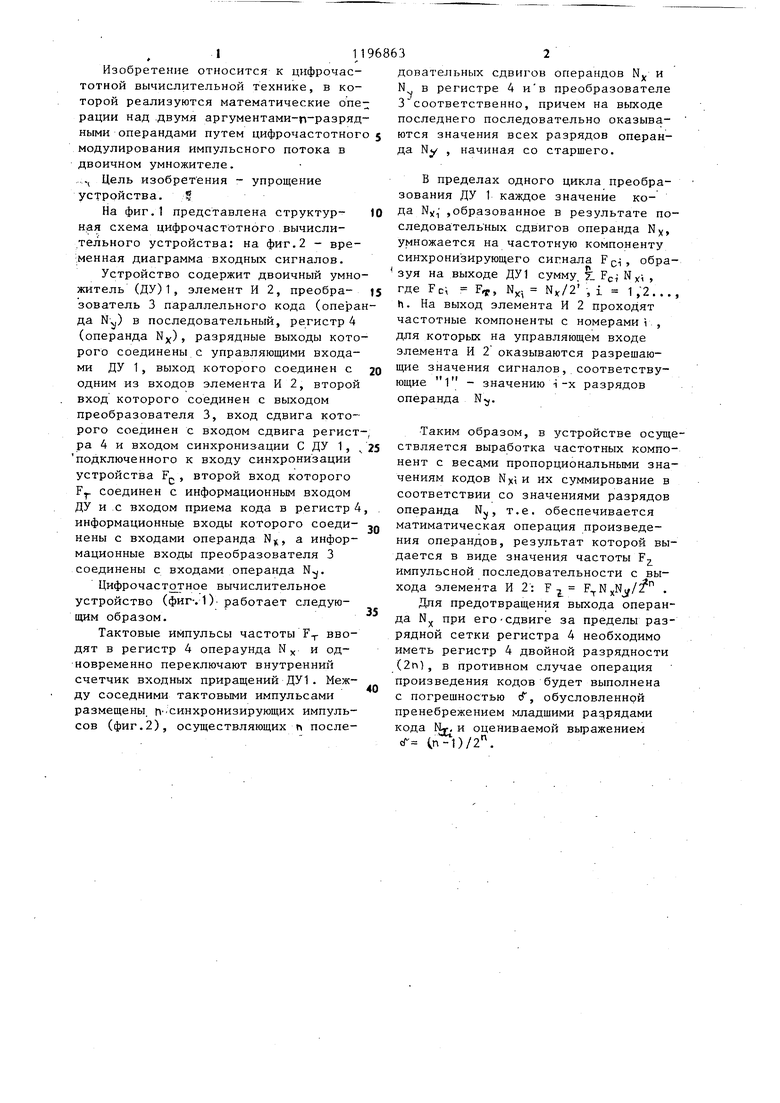

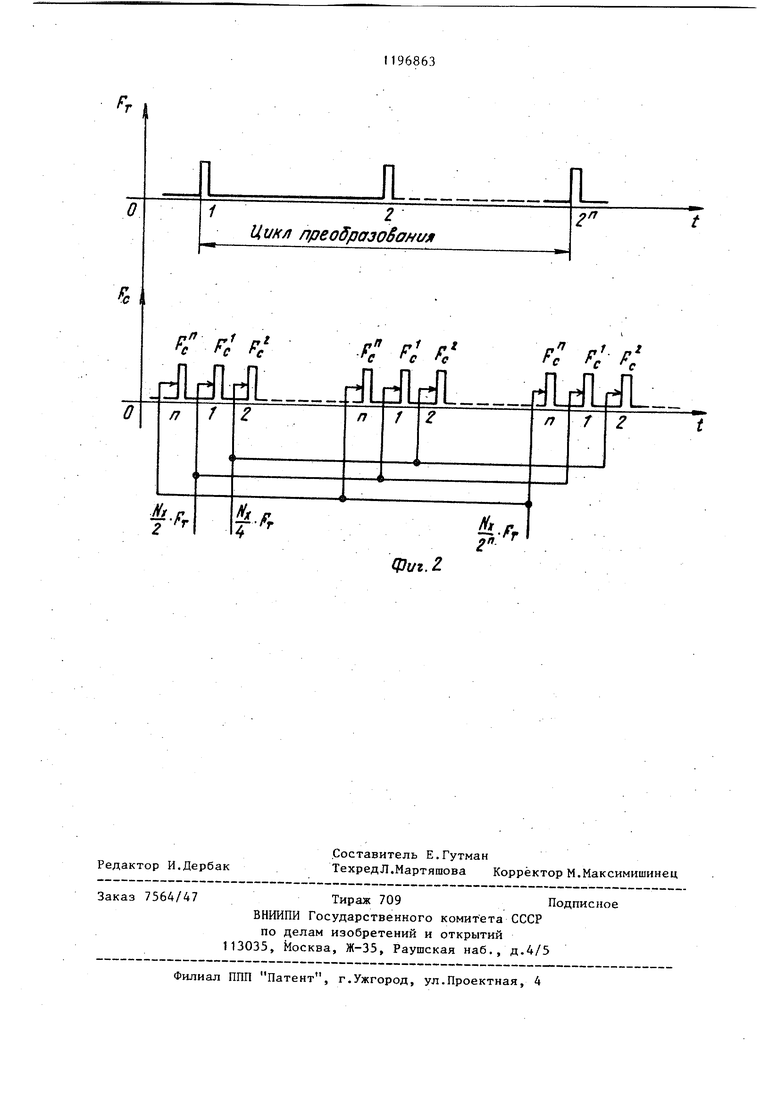

00 9д 00 Изобретение относится к цифрочастотной вычислительной технике, в которой реализуются математические опе рации над .двумя аргументами-п разряд ными операндами путем цифрочастотног модулирования импульсного потока в двоичном умножителе. . .J Цель изобретения - упрощение устройства. S На фиг.1 представлена структурная схема цифрочастотного вычислительного устройства: на фиг.2 - временная диаграмма входных сигналов. Устройство содержит двоичный умно житель (ДУ)1, элемент И 2, преобразователь 3 параллельного кода (опера да N-) в последовательный, регистр 4 (операнда Ny), разрядные выходы кото рого соединены с управляющими входами ДУ 1, выход которого соединен с одним из входов элемента И 2, второй вход которого соединен с выходом преобразователя 3, вход сдвига которого соединен с входом сдвига регист ра 4 и входом синхронизации С ДУ 1, подключенного к входу синхронизации устройства F, второй вход которого F,. соединен с информационным входом ДУ и с входом приема кода в регистр 4 информационные входы которого соединены с входами операнда N, а информационные входы преобразователя 3 соединены с входами операнда N. Цифрочастотное вычислительное устройство (фиг-. 1). работает следующим образом. Тактовые импульсы частоты F-p вводят в регистр 4 операунда N и одновременно переключают внутренний счетчик входных приращений ДУ1. Между соседними тактовыми импульсами размещены г синхронизирующих импульсов (фиг.2), осуществляющих п последовательных сдвигов операндов N и N в регистре 4 ив преобразователе 3 соответственно, причем на выходе последнего последовательно оказываются значения всех разрядов операнда Ny , начиная со старшего. В пределах одного цикла преобразования ДУ 1 каждое значение кода ,образованное в результате последовательных сдвигов операнда Ну, умножается на частотную компоненту Fci , обрасин-хронизирующего сигнала зуя на выходе ДУ1 сумму, Ji , где FC F,, N. ,1 1 ,2. . . , h. Ha выход элемента И 2 проходят частотные компоненты с номерами г , для которых на управляющем входе элемента И 2 оказываются разрешающие значения сигналов, соответствующие 1 - значению i-X разрядов операнда Ny. Таким образом, в устройстве осуществляется выработка частотных компонент с весдми пропорциональными значениям кодов Nxi и их суммирование в соответствии со значениями разрядов операнда N,, т.е. обеспечивается матиматическая операция произведения операндов, результат которой выдается в виде значения частоты F импульсной последовательности с выхода элемента И 2: F . Для предотвращения выхода операнда NJJ при его-сдвиге за пределы разрядной сетки регистра 4 необходимо иметь регистр 4 двойной разрядности (2п), в противном случае операция произведения кодов будет выполнена с погрешностью с, обусловленной пренебрежением младшими разрядами кода NT. и оцениваемой выражением с СпЧ)/2.

Фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для извлечения корня | 1985 |

|

SU1273922A1 |

| Устройство для умножения 12N-разрядных двоичных чисел | 1988 |

|

SU1589271A1 |

| Число-импульсный функциональный преобразователь | 1979 |

|

SU773620A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Генератор нормально распределенных случайных чисел | 1984 |

|

SU1226450A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

даФРОЧАСТОТНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее двоичный умножитель, регистр и элемент И, выход которого соединен с выходом устройства, а первый вход подключен к выходу двоичного умножителя, управляющие входы которого соединены с выходами разрядов регистра, отличающееся тем, что с целью упрощения, оно содержит преобразователь .параллельного кода в последовательный, выход которого соединен с вторым входом элемента И, информационный вход двоичного умножителя соединен с информационным входом устройства, вход синхронизации которого соединен с входами синхронизации двоичного преобразователя параллельного кода в последовательный и входом управления сдвигом регистра, информационные входы которого соединены с входами перв-ого § операнда устройства, входы преобразователя параллельного кода в последоО) вательный соединены с входами второго операнда устройства.

| Данчеев В.П | |||

| Цифрочастотные вычислительные устройства | |||

| - М.:Энергия, 1976, с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Цифрочастотное вычислительное устройство | 1979 |

|

SU855656A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-01-04—Подача