(54) ЧИСЛО-ИМГОЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ,

1

Изобретение относится к вычислительной технике и может быть исполь- эовано при построении специализированных вычислителей, работа которых основана на принципах цифрового интегрирования, т.е. связана с числоимпульсной обработкой информации.

Известно устройство, содержащее счетчики импульсов, вычислительные операции в котором осуществляются ,за счет управления коэффициентами деления счетчиков l.

Однако устройство не имеет возможности разделить меньшее число на большее.

Наиболее близким по технической сущности к предложенному является устройство, содержащее умножители, регистры, счетчики; причем входы сдвива и записи регистров соединены с соответствующими входами устройства, разрядные входы регистров соединены с информационными входами устройства, выход последнего разряда каждого регистра подключен к последовательному входу этого регистра, выходы разрядов первого и второго регистров подключены соответственно к разрядным входам первого и второго умножителей, тактовые вхолы которых соединены со входами устройства, входы записи первого и второго счетчиков и установки в ноль счетчиков и умножителей соединены со входш- и устройства, выходы разрядов первого и второго счетчиков являются выходами устройст,ва 2.

Недостатком известного устройства является невозможность реализации операции деления.

Цель изобретения - расширение класса решаемых задач за счет возможности выполнения операции деления.

Поставленная цель достигается тем, что в устройство, содержащее умножитель, регистры, счетчики, при-, чем входы сдвига и записи регистроя

20 соединены с соответствующими входаt.Ki устройства, разрядные входы регистров соединены с информационными входами устройства, выход послед- него разряда каждого регистра под25 . ключен к пocлeдoвaтeльнo i входу

этого регистра, выходы разрядов первого и второго регистров подключены соответственно к разрядным входам первого и второго y шoжитeлeй,

30 . тактовые входы которых соединены со,

входами устройства, выходы записи ; первого и второго счетчиков и входы установки в ноль счетчиков и умножителей соединены со входами устройства, выходы разрядов первого и второго счетчиков являются выходами) устройства, дополнительно введен коммутатор, информационные входы которого соединены со входами устройства, а управляющие - со входами

управления устройства, первый и второй входеа коммутатора связаны с выходами первого и второго умножителя соответственно, первый и второй выходы коммутатора подключены к входам суммирования первого и второго счетчиков соответственно,-третий и четвертый выходы коммутатора подключены к выходам вычитания первого и второго счетчиков соответственно, разрядные входы первого и второго счетчикЪв подключены к разядным выходам первого и второго егистров соответственно-.

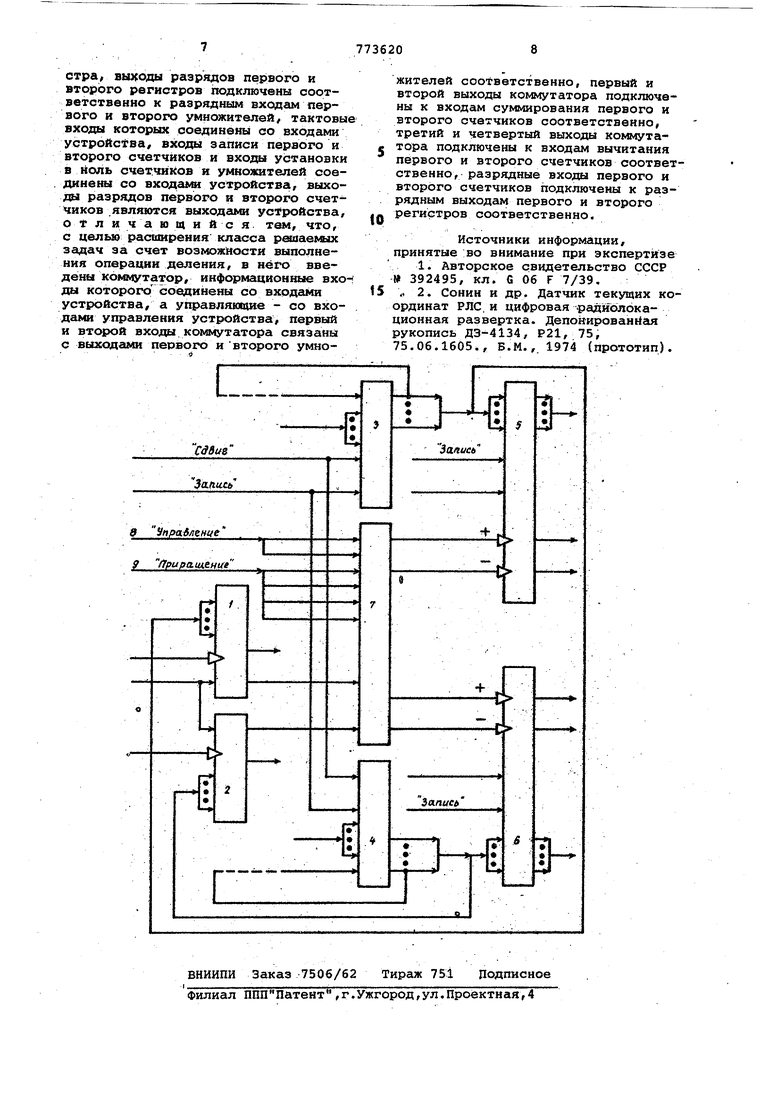

. На чертеже представлена блок-схеа устройства. ,.

Устройство содержит умножители 1 и 2, регистры 3 и 4, счетчики 5 б, коммутатор 7, .входы 8 управления коммутатором 7, входы 9 прира-. ений.

Функционирование устройства основано на принципах цифрового интегрирования. Устройство может выполнять несколько вычислительных операций {суммирование, вычитание, умножение, деление).

Каждую из операций устройство осуществляет за цикл вычисления, длительность которого определяется длительностью формирования числоимпульсного кода операнда, который вырабатывается в процессе выполнения операции, т.е. при выполнении операции сложения определяется величиной второго слагаемого, при выполнении операции умножения - величиной, второго сомножителя, а при делении - величиной самого частного.

Для описания работы устройства . примем, что все операнды а., Ь, с и d нормированы так, что каждому из них соответствует п разрядное двоичное число (Tie. число а или Ь или с, или d),. изменяющееся в пределах от О до 1-2 с весом младшего разряда 2.

Возможно несколько алгоритмов выполнения устройством операции умножения.. . : .

Поэтому рассмотрим-работу устройства при выполнении операции умножения первого операнда а и второго операнда Ь на третий операнд с по тому алгоритму, который наиболее полно характеризует устройство и определяется логическим значением С старшего разряда операнда С-20 2 .,

Операция умножения по этому агГГоритму осуществляется следуКщим образом.

Перед началом каждого цикла операции в устройстве содержится информация, обусловленная предыдущим циклом работы, а с входов 8 устройства на входы коммутатора 7 приходит двухразрядный управляющий код, который активизирует работу коммут.атора 7 так, что коммутатор 7 разрешает прохождение сигнала с выхода умножителя 1 и сигнала с выхода умножителя 2 при соответственно на суммирующий вход счетчика 5 и суммирующий вход счетчика б, а при - на вычитающий вход счетчика

5и вычитающий вход счетчика 6.

При этом непосредственно перед началом цикла вычисления умножители 1 И 2 устанавливаются в О, в регистре 3 и 4 заносятся или последовательными или параллельными кодами соответственно операнда а и Ь. , если , то -счетчики 5 и

6устанавливаются в О, а если С,1, то в счетчик 5 с регистра 3 заносится операнд а, а в счетчик б с регистра 4 - операнд Ь.

После этого начинается цикл вы-, числения, который производится при по импульсам число-импульсного кода, соответствуклцего прямому двоичному коду операнда , а при - по импульсам число-импульсного кода, соответствуквдего дополнительному коду операнда С, т.е. по ч 1сло-импуль.сному коду операнда САОП I (Сд.оп) , где )- и 2 соответственно логический и весовой коэффициенты операнда . Поэтому в течение цикла вычисления с входов устройства на тактовые входы умножителей 1 и 2 поступают импульсы число-импульсного кода С при С 0 или Сдоп при , число которых равно: ,

К(С )(.) ,

По импульсам М( операнду а умнжитель 1 на выходе вырабатывает импульсы число-импульсного кода, умножитель 2 по импульсам Nt) и операнду Ь - импульсы число-импульсного кода.

Так как , то в результате выполнения операции через время Т, в счетчике 5 и в счетчике б будут содержаться соответственно код первого и второго произведений, определяемых в соответствии с алгоритмом выпВлнения операции умножения/

а-с , ,( ) ,Ъс ,Нце-С()

Не трудно заметить, что длительность цикла вычисления можно оценить выражением

N(

где Т - период частоты последователности тактовых импульсов.

Рассмотрим осущестбление в устростве операции деления.

Для выполнения этой операций с входов 8 устройства на коммутатор 7 поступает управляющий код, который активизирует работу коммутатора 7 так, что коммутатор 7 разрешает прохождение сигнала с выхода . умножения 1 и выхода умножения 2, соответственно, на вычитающий вход счетчика 6 и вычитающий вход счетчика 6 и вычитакяций вход счетчика 5,

Устройство работает следующим образом.

Перед началом цикла выполнения операции, умножители 1 и 2 устанавливаются в О, а в регистры 3 и 4 заносятся последовательными, или параллельными кодами соответственно операнды а и Ь. После занесения операндов в регистры 3 и 4, если окажется, что одновременно и ,5 и ,5, то на регистры 3 и 4 поступают сдвиговые импульсы.

По этим импульсам, число которых не более п, содержимое обоих регистров 3 и 4 сдвигается вправо до тех пор, пока в старшем разряде по крайней мере одного из регистров при или не появится 1

Это производится для того, чтобы повысить точность выполнения операции деления в том случае, когда исходные величины операндов а -и Ь малы.

После выполнения сдвига производится запись в счетчики 5 и б с регистров 3 и 4 соответственно операндов а и Ь таких, что если одновременно эти операнды не равны О, то для них обязательно выполняется условие 0, или Ь 1-2.

Таким образом, перед началом вычисления умножители 1 и 2 обнулены, в регистре 3 и в счетчике 5 содержися операнд а, а в регистре 4 и счетчике 6 - операнд Ь.

Цикл вычисления осуществляется так, что сначала с число-импульсных входов 9 устройства через ком« утатор 7 на вычитающие входы счетчиков 5 и б поступает одновременно по корректирукйдему импульсу, а затем чере коммутатор 7 на вычитающий вход счетчика 5 поступают импульсы числоимпульсного кода с выхода умножител 2, а на вычитающий вход счетчика б импульсы число-импульсного кода аd(t) с, выхода умножителя 1, где d(t) - некоторый операнд, представленный импульсами число-импульсного кода, поступающими на тактовые входы умножителей 1 и 2 с входов устройства в течение цикла деления. .Содержимое счетчиков 5 и б начинает уменьшаться сначала по импульсу коррекции, а затем по импульсам число-импульсного кода b.d(t) и импульсам число-импульсного кода a«l(t) соответственно.

Этот процесс, продолжается до тех

0 пор, пока не переполнится, по крайней мере, один из счетчиков 5 или б. Причем при переполнении счетчика 5 на выходе генерируется импульс переполнения, -аналогично и при пере5полнении :счетчика 6.

Импульсы переполнения снимаются с устройства и сигнализируют о том, что цикл выполнения текущей операции заканчивается. В некоторый мент после окончания любого из этих импульсов прекращается поступление на тактовые входы умножителей последовательности импульсов, представляющей число-импульсный код некоторого аргумента d.

5

Следовательно, переполнение одного из счетчиков 5 или б или одновременное переполнение обоих счетчиков означает;решение одного или обоих уравнений системы:

0 d(tci)a/b . d{tЪ)b/a

Решением системы является величина d такая, что

при , (toi)a/b

5

при , (tb)b/a .

при , (ta)d(tb) .

Результат выполнения операции -деления, импульсы d снимаются с входа устройства и соответствуют числу, изменякядемуся от О до (1-2) . «

0

Таким образом, устройство позволяет автоматически поделить меньшее нз двух чисел на большее из них.

Нетрудно заметить, что устройство позволяет также автоматически

5 поделитьбольшее из двух чисел на меньшее из них.

При выполнении функции известного устройства, предложенное устройство может иметь в два раза более

0 высокое быстродействие, чем известное.

изобретения

Число-импульсный функциональный преобразователь, содержащий умножители, регистры, счетчики, причем входы сдвига и запись регистров соединены с соответствующими входами устройства, разрядные входы регистров соединены с информационными входами устройства, выход последнего ряда каждого регистра подключен к последовательному входу этого ретиотра, выводы разрядов первого и второго регистров подключены соответственно к разрядным входам первого и второго умножителей, тактовы входы которых соединены со входами устройства, входы записи первого и второго счетчиков и входы установки в ноль счетчиков и умножителей соединены со входа «1 устройства, выхода разрядов первого и второго счетчиков .являются выходами устройства, от л и ч а ю щ и И с я. тем, что, с целью расширения класса решаегюых задач за счет возможности выполнения операции деления, в пеРо введены коммутатор, информационные вхо да которого соединены со входами устройства, а управля1а11(ие - со входами управления устройства, первый и второй входы ко имутатора связаны с выходёши первого и втсфого умножителей соответственно, первый и второй выходы коммутатора подключены к входам суммирования первого и второго счетчиков соответственно, третий и четвертый выходы коммутатора подключены к входам вычитания первого и второго счетчиков соответственно, разрядные входы первого и второго счетчиков подключены к разрядным выходам первого и второго регистров соответственно.

Источники информации, принятые :во внимание при экспертизе

1. Авторское свидетельство СССР 392495, кл. G Об F 7/39. , 2. Сонин и др. Датчик текущих координат РЛС, и цифровая радиолокационная развертка. Депон ированйая рукопись ДЗ-4134, Р21, 75, 75.06.1605., Б.М., 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1979 |

|

SU773622A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

Авторы

Даты

1980-10-23—Публикация

1979-04-04—Подача