Изобретение относится к вычислительной технике в частности к устройствам управления различными объектами в условиях поступления множества заявок на обслуживание.

Цель изобретения - сокращение оборудования.

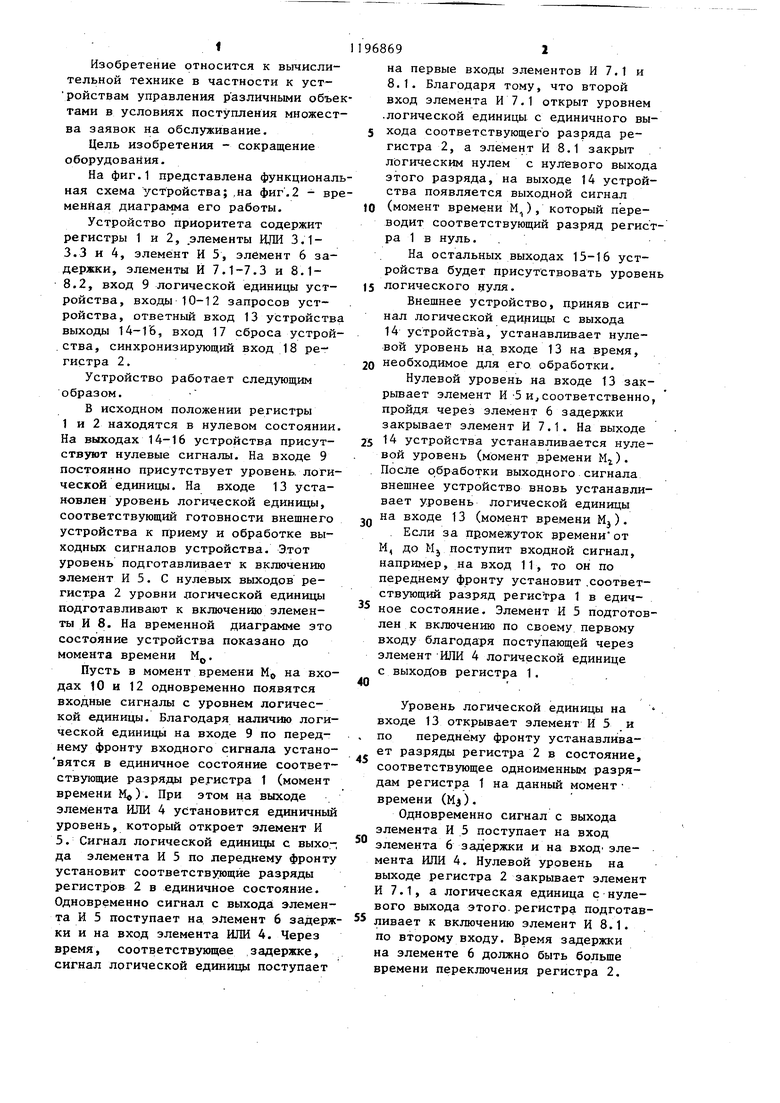

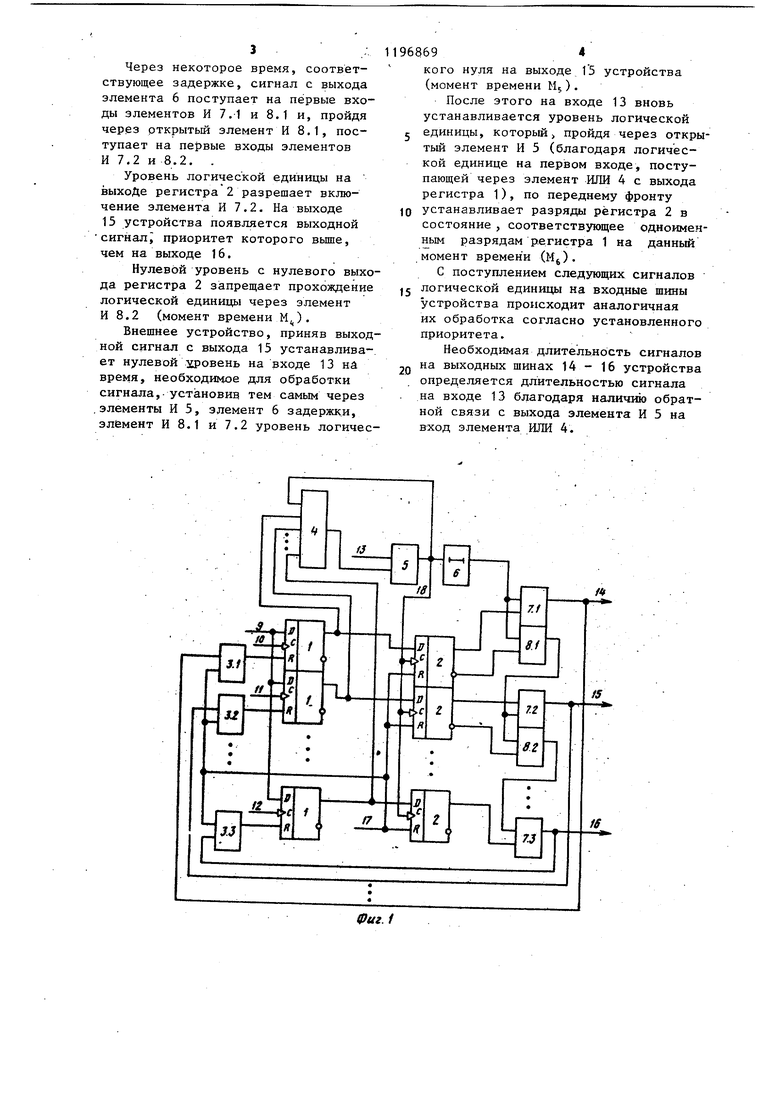

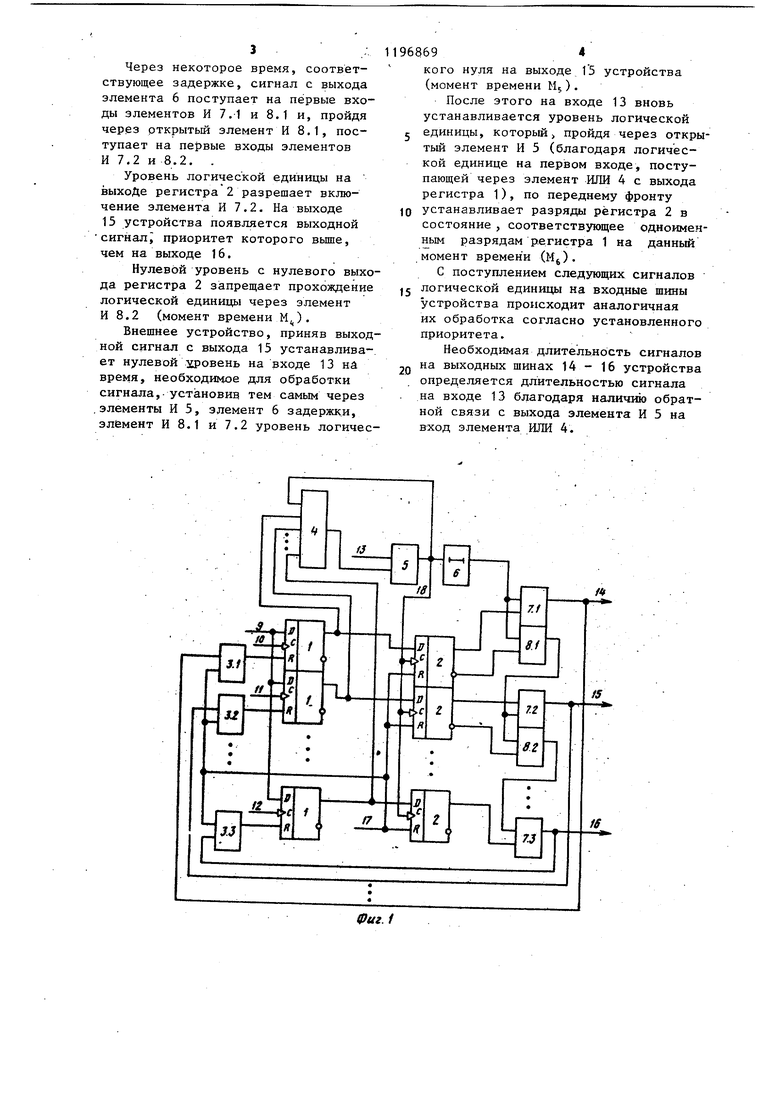

На фиг.1 представлена функциональная схема устройства;,на фиг.2 - временная диагра1 1ма его работы.

Устройство приоритета содержит регистры 1 и 2, .элементы ИЛИ 3,13.3 и 4, злемёнт И 5, элемент 6 задержки, элементы И 7.1-7.3 и 8.18.2, вход 9 логической единицы устройства, входы 10-12 запросов устройства, ответный вход 13 устройства выходы 14-16, вход 17 сброса устрой. ства, синхронизирующий вход 18 регистра 2.

Устройство работает следующим образом.

В исходном положении регистры 1 и 2 находятся в нулевом состоянии На выходах 14-16 устройства присутствуют нулевые сигналы. На входе 9 постоянно присутствует уровень, логической единицы. На входе 13 установлен уровень логической единицы, соответствующий готовности внещнего устройства к приему и обработке выходных сигналов устройства. Этот уровень подготавливает к включению элемент И 5. С нулевых выходов регистра 2 уровни югической единиць подготавливают к включению элементы И 8. На временной диаграмме это состояние устройства показано до момента времени М.

Пусть в момент времени М на входах 10 и 12 одновременно появятся входные сигналы с уровнем логической единицы. Благодаря наличию логической единицы на входе 9 по переднему фронту входного сигнала установятся в единичное состояние соответствующие разряды регистра 1 (момент времени MO). При этом на выходе элемента ИЛИ 4 установится единичный уровень, который откроет элемент И 5. Сигнал логической единицы с выхода элемента И 5 по лереднему фронту установит соответствующие разряды регистров 2 в единичное состояние. Одновременно сигнал с выхода элемента И 5 поступает на элемент 6 задержки и на вход элемента ИЛИ 4. Через время, соответствующее задержке, сигнал логической единицы поступает

968692

на первые входы элементов И 7.1 и 8.1. Благодаря тому, что второй вход элемента И 7.1 открыт уровнем .логической единицы с единичного выхода соответствующего разряда регистра 2, а элемент И 8.1 закрыт логическим нулем с нулевого выхода этого разряда, на выходе 14 устройства появляется выходной сигнал

10 (момент времени М), который переводит соответствующий разряд регистра 1 в нуль. ,

На остальных выходах 15-16 устройства будет присутствовать уровень

15 логического гуля.

Внешнее устройство, приняв сигнал логической едирицы с выхода 14 устройства, устанавливает нулевой уровень на входе 13 на время,

20 необходимое для его обработки.

Нулевой уровень на входе 13 закрывает элемент И -5 Илсоответственно, пройдя через элемент 6 задержки закрывает элемент И 7.1. На выходе

25 14 устройства устанавливается нулевой уровень (момент времени Mj). . После о.бработки выходного сигнала внешнее устройство вновь устанавливает уровень логической единицы

, на входе 13 (момент времени Mj). . Если за промежуток времениот М, до MJ поступит входной сигнал, например, на вход 11, то он по переднему фронту установит .соответствующий разряд регистра 1 в едич ное состояние. Элемент И 5 подготовлен к включению по своему первому входу благодаря поступающей через элемент ИЛИ 4 логической единице

с выходов регистра 1. 40

Уровень логической единицы на входе 13 открывает элемент И 5 и по переднему фронту устанавливает разряды регистра 2 в состояние, соответствующее одноименным разрядам регистра 1 на данный момент времени (Mj).

Одновременно сигнал с выхода элемента И 5 поступает на вход элемента 6 задержки и на вхоДэлемента ИЖ 4. Нулевой уровень на выходе регистра 2 закрывает элемент И 7.1, а логическая единица с нулевого выхода этого.регистру подготавливает к включению элемент И 8.1. по второму входу. Время задержки на элементе 6 должно быть больще времени переключения регистра 2.

3.

Через некоторое время, соответствующее задержке, сигнал с выхода элемента 6 поступает на первые входы элементов И 7.1 и 8.1 и, пройдя через рткрытьй элемент И 8.1, поступает на первые входы элементов И 7.2 и 8.2. .

Уровень логической единицы на выходе регистра2 разрешает включение элемента И 7.2. На выходе 15 устройства появляется выходной сигнал приоритет которого вьше, чем на выходе 16.

Нулевой уровень с нулевого выхода регистра 2 запрещает прохождение логической единицы через элемент И 8.2 (момент времени М,,).

Внешнее устройство, приняв выходной сигнал с выхода 15 устанавливает нулевой уровень на входе 13 на время, необходимое для обработки сигнала,- установив тем самьм через .элементы И 5, элемент 6 задержки, элбмент И 8.1 и 7.2 уровень логичес96869

кого нуля на выходе Г5 устройства (момент времени М).

После этого на входе 13 вновь устанавливается уровень логической с единицы, который пройдя через открытый элемент И 5 (благодаря логической единице на пер;вом входе, поступающей через элемент ИЛИ 4 с выхода регистра 1), по переднему фронту Q устанавливает разряды регистра 2 в состояние , соответствующее одноименным разрядам регистра 1 на данный момент времени (М).

С поступлением следующих сигналов с логической единицы на входные шины устройства происходит аналогичная их обработка согласно установленного приоритета.

Необходимая длительность сигналов на выходных шинах 14-16 устройства

20 определяется длительностью сигнала на входе 13 благодаря наличию обратной связи с выхода элемента И 5 на вход элемента ИЛИ 4.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестовых воздействий | 1987 |

|

SU1476473A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Устройство для имитации технической системы конвейерного типа | 1990 |

|

SU1741102A1 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

| Коммутатор с заданием порядка коммутации | 1986 |

|

SU1319268A1 |

| Устройство для имитации технической системы конвейерного типа | 1988 |

|

SU1522159A1 |

| Устройство для деления на константу 2 @ -1 | 1987 |

|

SU1490675A1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

УСТРОЙСТВО ПРИОРИТЕТА, содержащее элемент И, элемент ИЛИ,два регистра, группу элементов ИЛИ, группу элементов И, при этом единичные выходы первого регистра соединены с входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого соединен с ответным входом устройства, выходы четных элементов И группы соединены с первыми входами следующих нечетного и четного элементов И группы,выходы нечетных элементов И группы являются выходами устрой,ства, отличающее с я тем, что, с целью сокращения оборудования, оно содержит элемент задержки, причем каждый вход запроса устройства канала соединен с синхронизирующим входом одноименного разряда первого регистра, информационные входы которого соединены с входом логичес-кой единицы устройства, входы сброса первого регистра соединены с выходами соответствующих элементов ИЛИ группы, первые входы которых соединены с входом сброса устройства и с входами сброса второго, регистра, единичные выходы первого регистра соединены с информационными Ьходами второго регистра, синхронизирующие входы второго регистра- соединены с выходом элемента И, с соответствующим входом элемента ИЛИ и входом элемента задержки, выход которого сл соединен с первыми входами первого и второго элементов И группы, вторые входы нечетных элементов И группы соединены с выходами соответствующих разрядов второго регистра,вторые входы четных элементов И группы соединены инверсными выходами соотю ветствующих разрядов второго регистО) ра, выходы устройства соединены с 00 вторыми входами одноименных элеменР со тов ИЛИ группы.

| Многоканальное устройство приоритета | 1979 |

|

SU811260A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство приоритета | 1978 |

|

SU811256A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-07-06—Подача