Изобретение относится к импульсной и вычислительной технике, в частности к импульсным счетчикам фазоимпульс- ным представлением информации, и может быть применено в устройствах промышленной автоматики и вычислительной техники.

Цель изобретения - повышение достоверности функционирования и автоматизация процесса восстановления работоспособности.

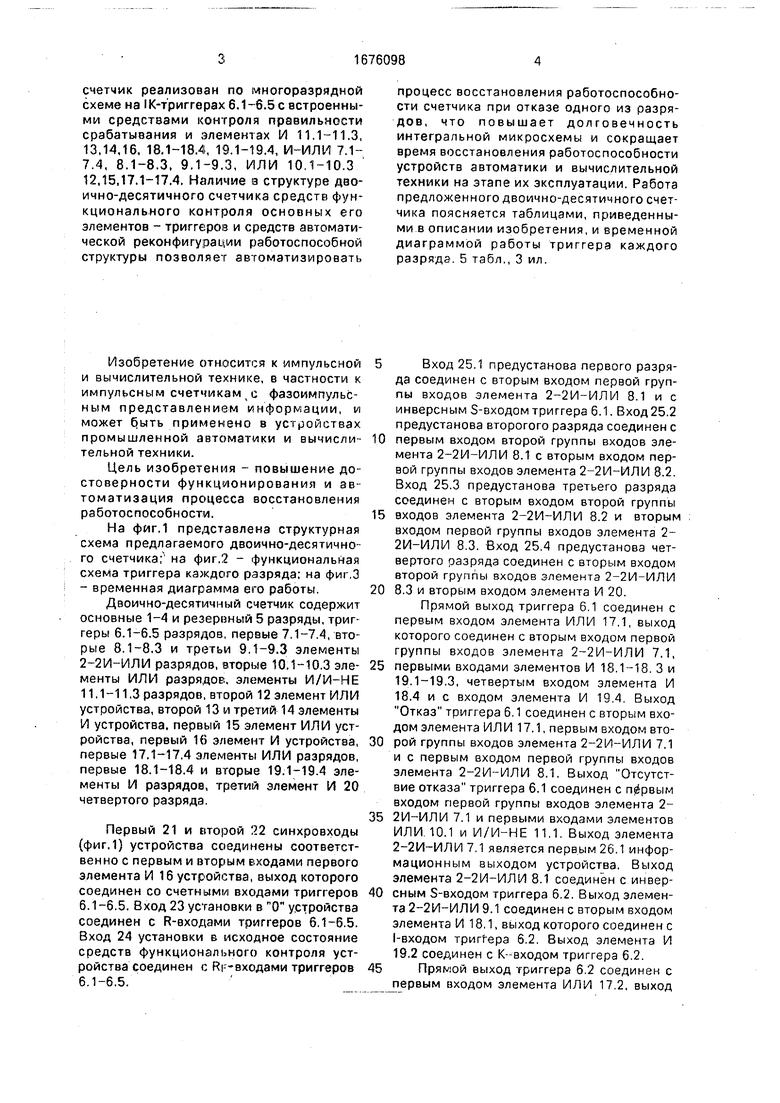

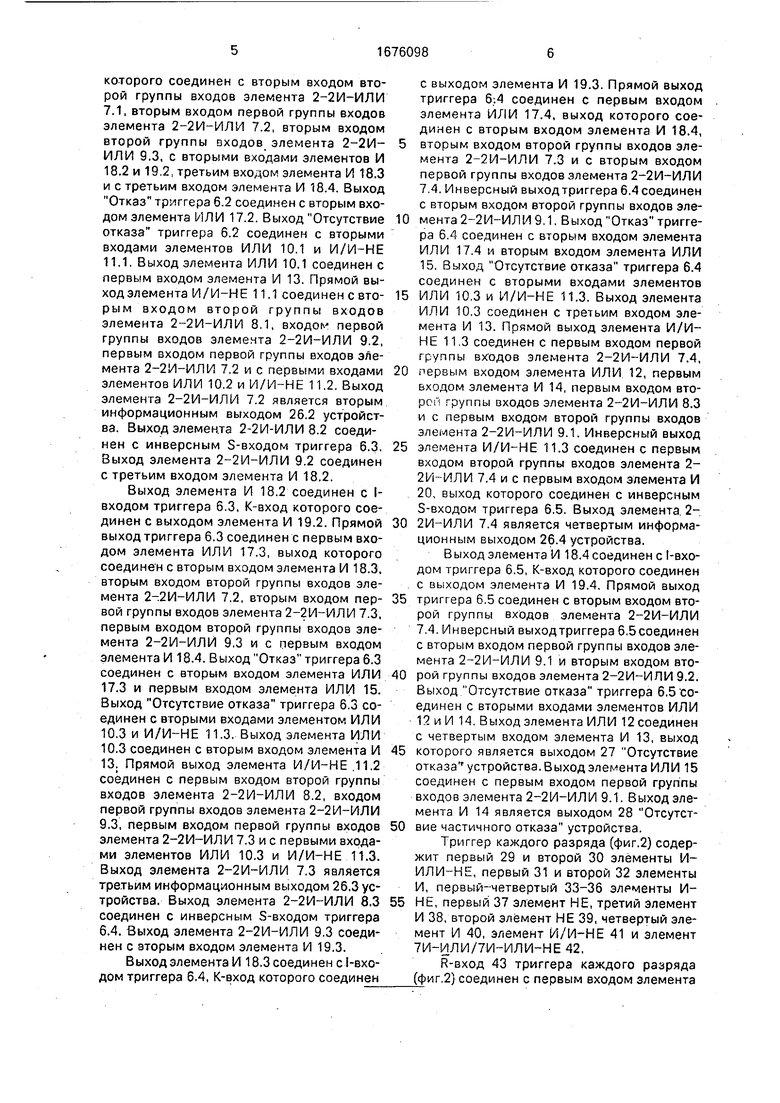

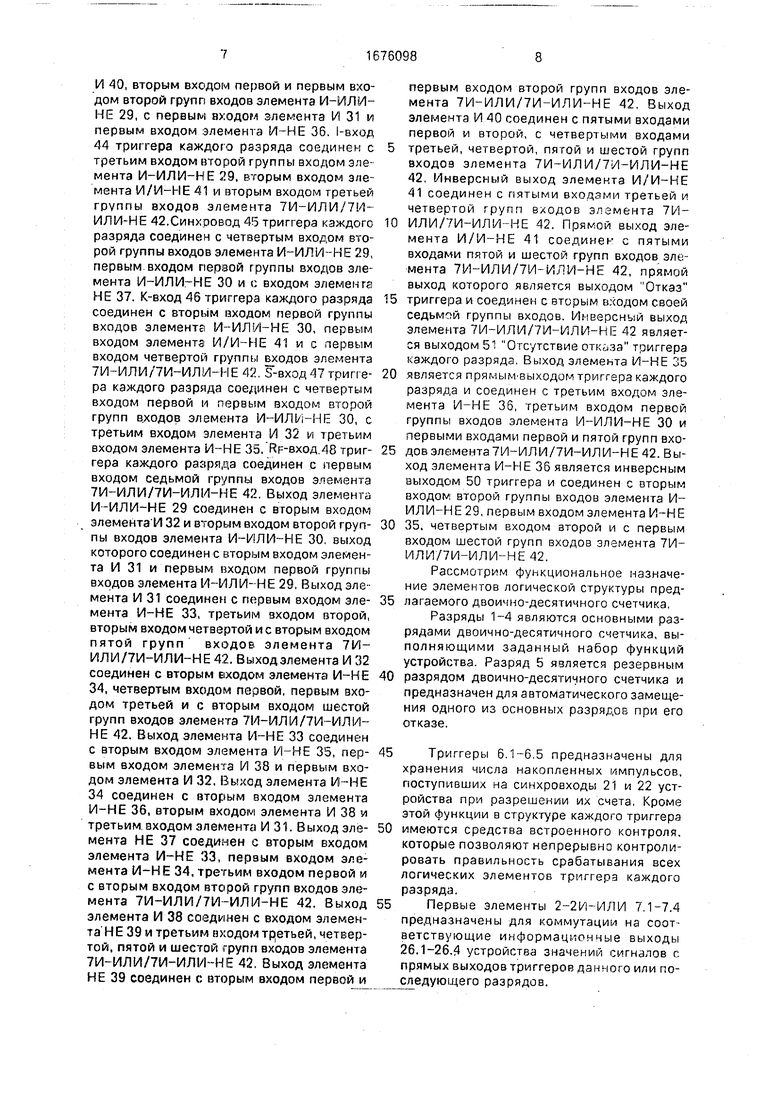

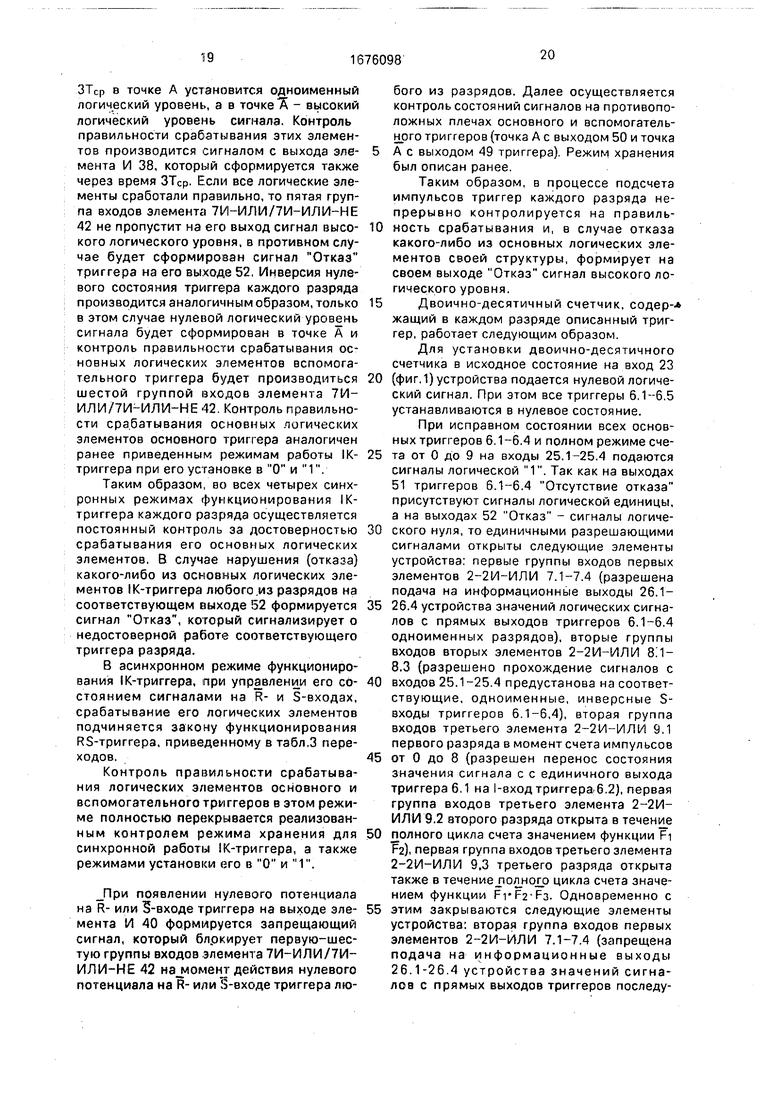

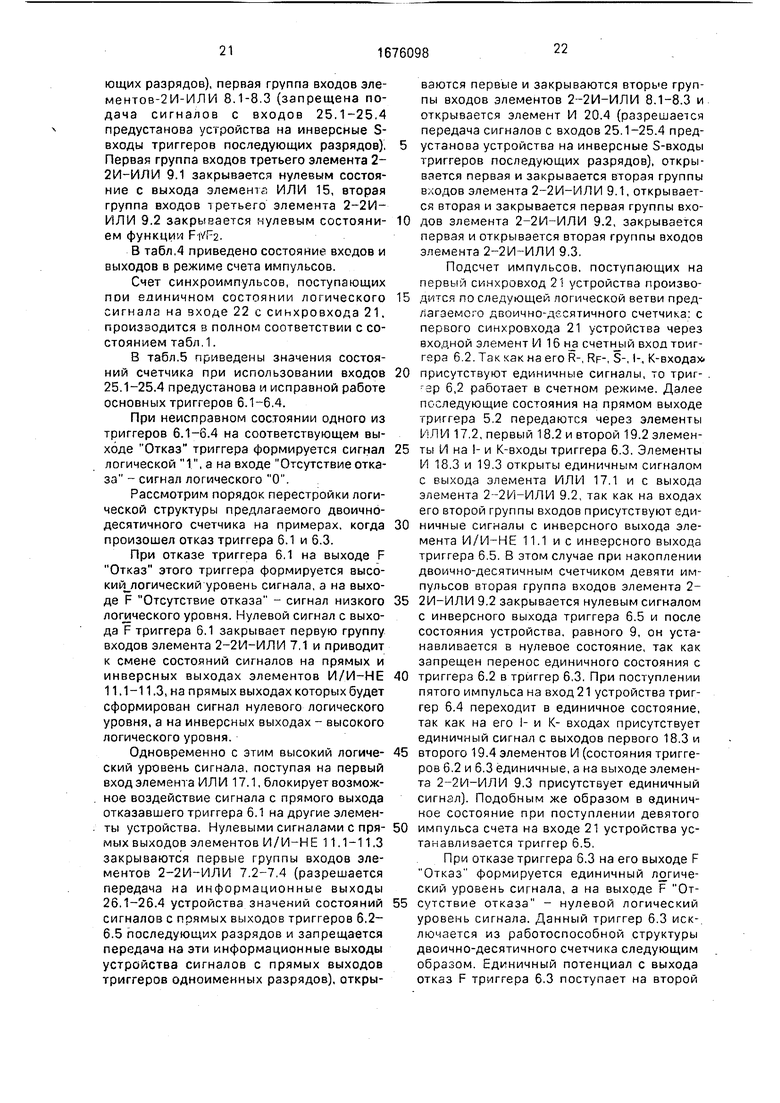

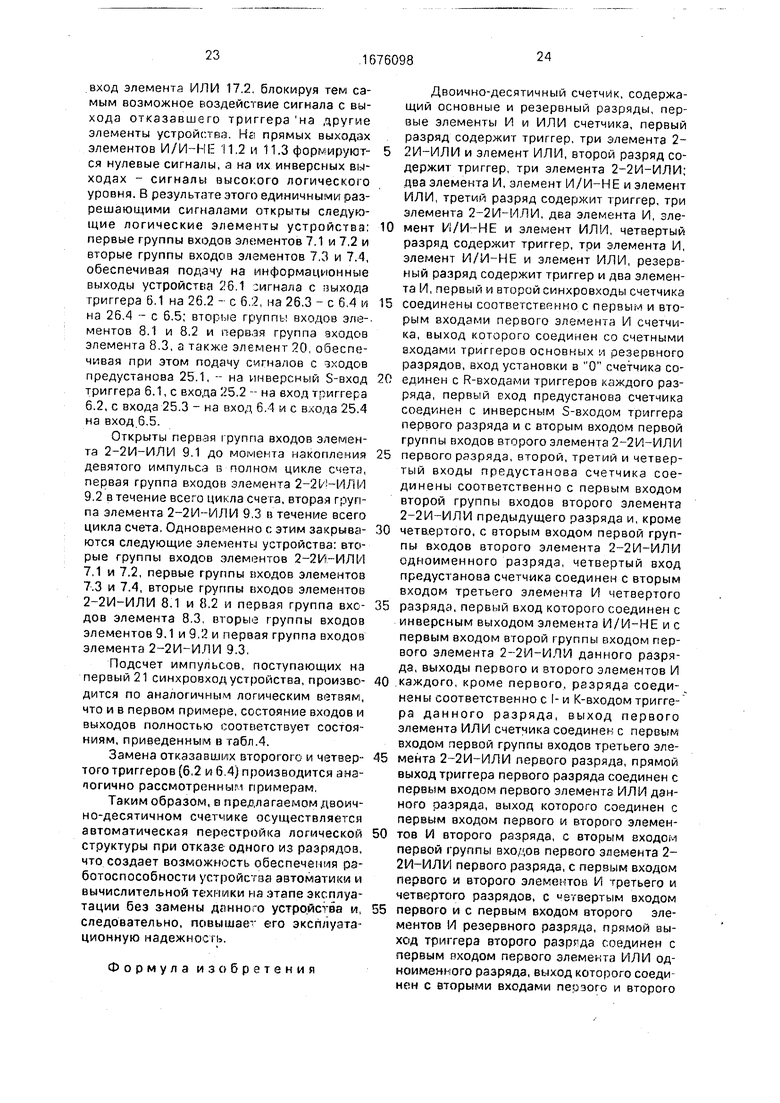

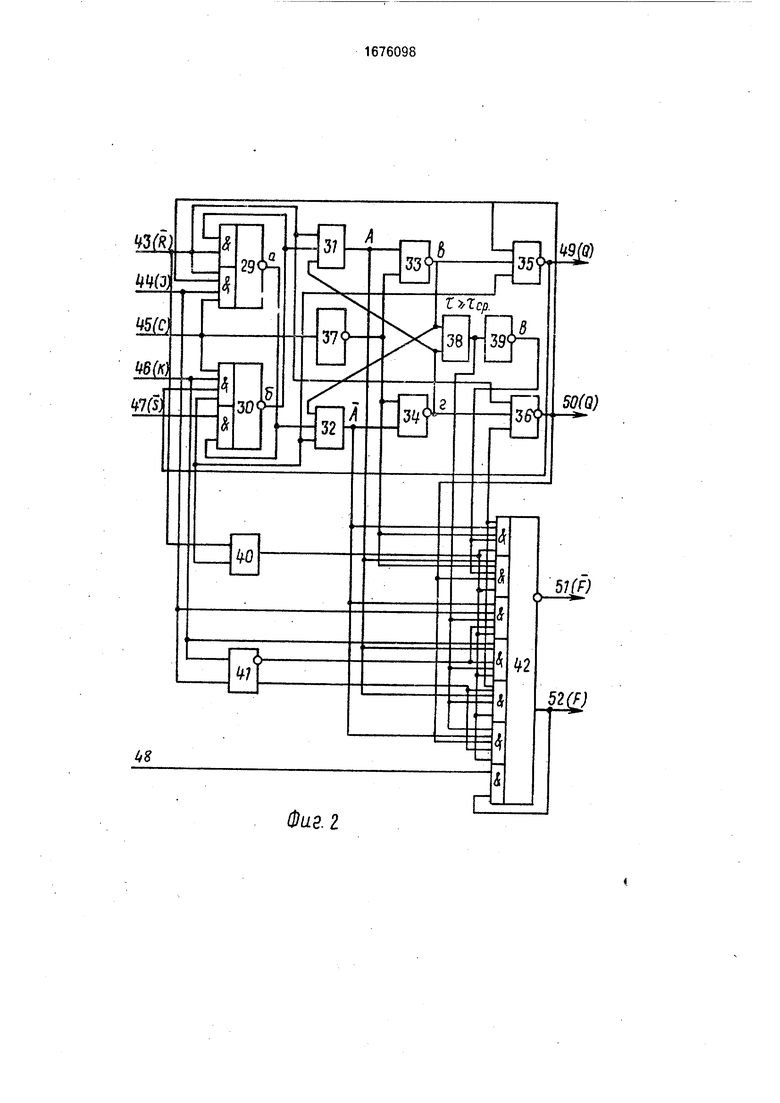

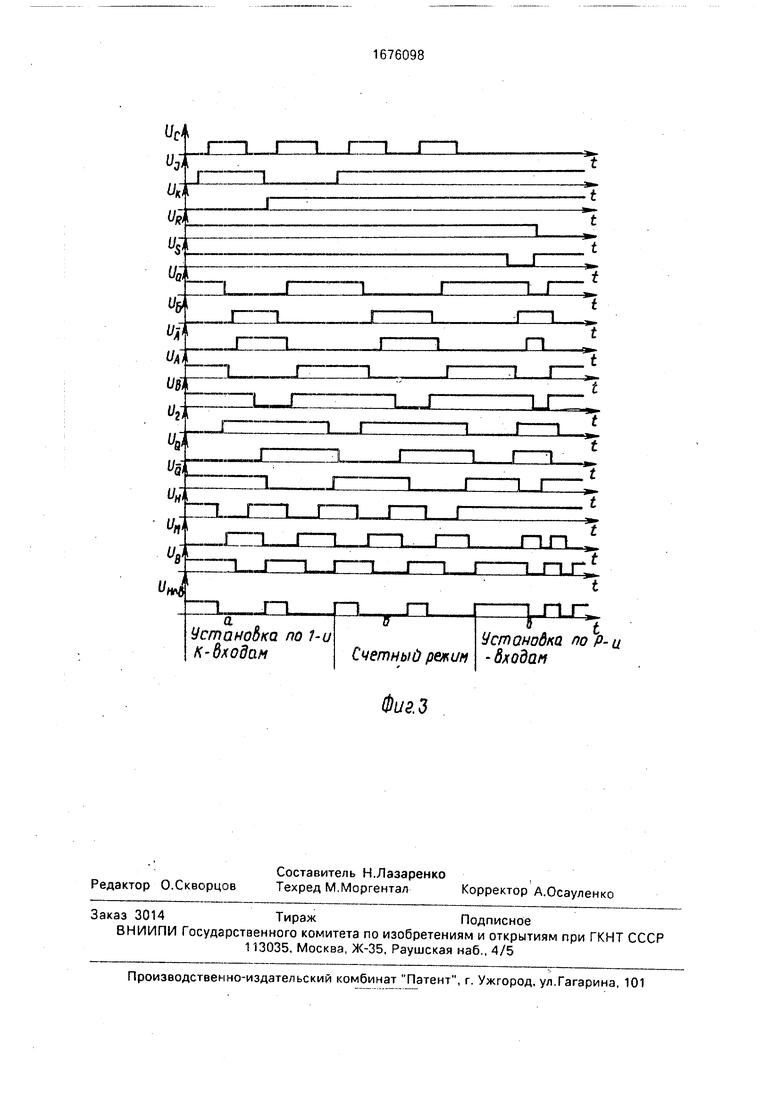

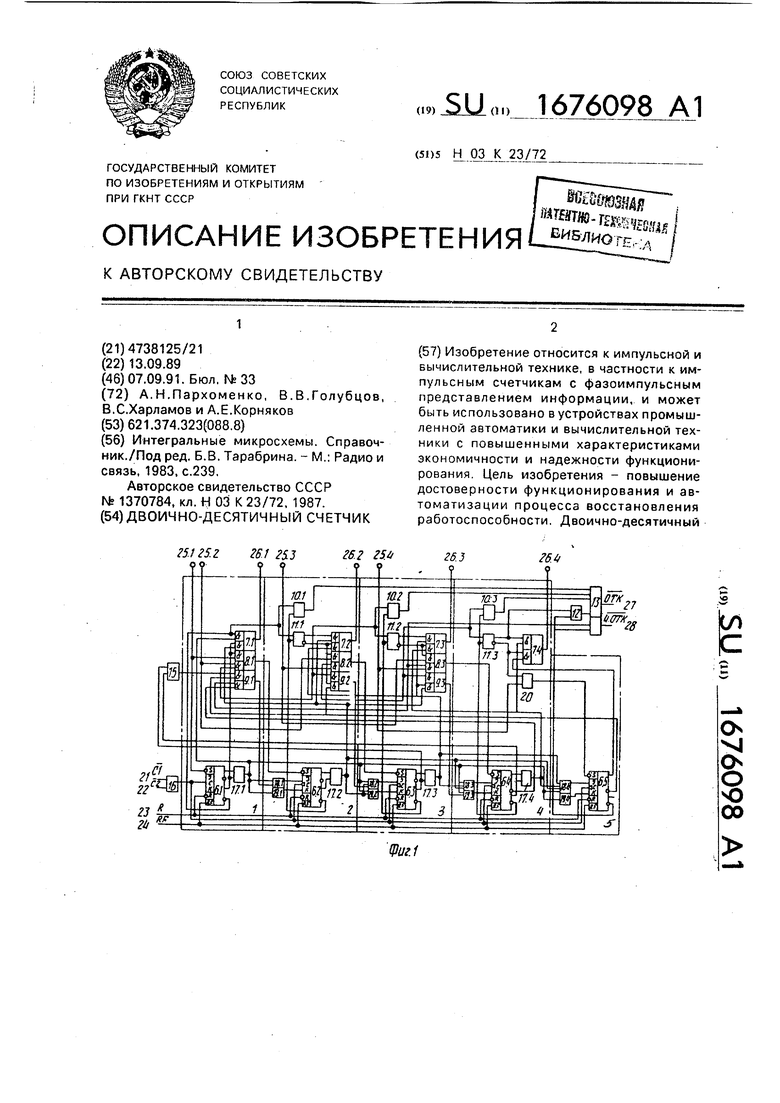

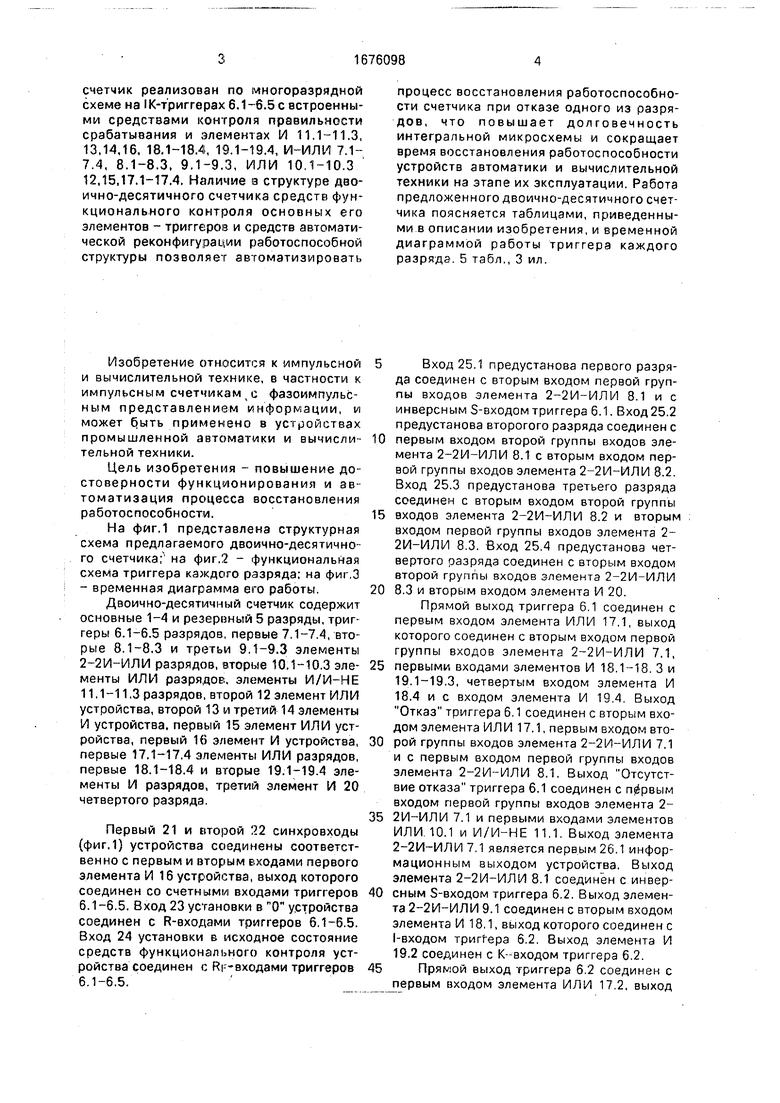

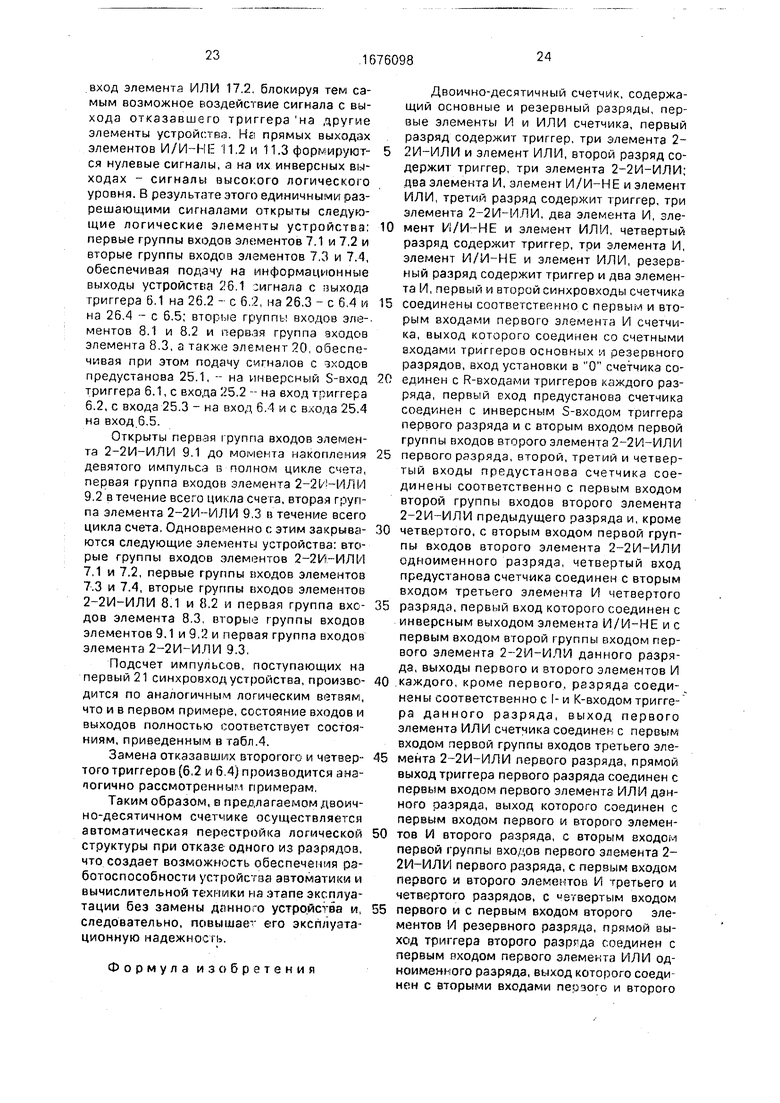

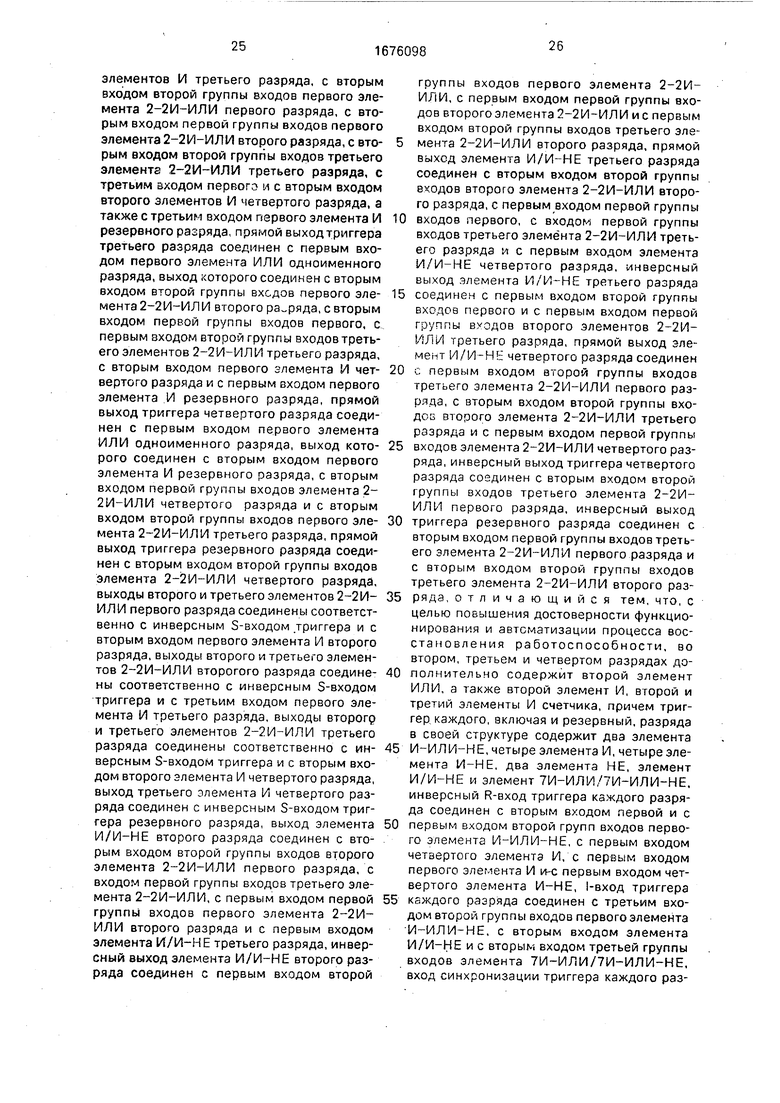

На фиг.1 представлена структурная схема предлагаемого двоично-десятичного счетчика; на фиг.2 - функциональная схема триггера каждого разряда; на фиг.З - временная диаграмма его работы.

Двоично-десятичный счетчик содержит основные 1-4 и резервный 5 разряды, триггеры 6.1-6.5 разрядов, первые 7.1-7.4, вторые 8.1-8.3 и третьи 9.1-9.3 элементы 2-2И-ИЛИ разрядов, вторые 10.1-10.3 элементы ИЛИ разрядов, элементы И/И-НЕ 11.1-11,3 разрядов, второй 12 элемент ИЛИ устройства, второй 13 и третий 14 элементы И устройства, первый 15 элемент ИЛИ устройства, первый 16 элемент И устройства, первые 17.1-17.4 элементы ИЛИ разрядов, первые 18.1-18.4 и вторые 19.1-19.4 элементы И разрядов, третий элемент И 20 четвертого разряда.

Первый 21 и второй 22 синхровходы (фиг.1) устройства соединены соответственно с первым и вторым входами первого элемента И 16 устройства, выход которого соединен со счетными входами триггеров 6.1-6.5. Вход 23 установки в О устройства соединен с R-входами триггеров 6.1-6.5. Вход 24 установки в исходное состояние средств функционального контроля устройства соединен с Rp-входами триггеров 6.1-6.5.

Вход 25.1 предустанова первого разряда соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 8.1 и с инверсным S-входом триггера 6,1. Вход 25.2 предустанова второгого разряда соединен с

первым входом второй группы входов элемента 2-2И-ИЛИ 8.1 с вторым входом первой группы входов элемента 2-2И-ИЛИ 8.2. Вход 25.3 предустанова третьего разряда соединен с вторым входом второй группы

входов элемента 2-2И-ИЛИ 8.2 и вторым входом первой группы входов элемента 2- 2И-ИЛИ 8.3. Вход 25.4 предустанова четвертого разряда соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ

8.3 и вторым входом элемента И 20.

Прямой выход триггера 6.1 соединен с первым входом элемента ИЛИ 17.1, выход которого соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 7.1,

первыми входами элементов И 18.1-18. 3 и 19,1-19.3, четвертым входом элемента И 18.4 и с входом элемента И 19.4. Выход Отказ триггера 6.1 соединен с вторым входом элемента ИЛИ 17.1, первым входом второй группы входов элемента 2-2И-ИЛИ 7,1 и с первым входом первой группы входов элемента 2-2И-ИЛИ 8.1. Выход Отсутствие отказа триггера 6.1 соединен с первым входом первой группы входов элемента 22И-ИЛИ 7.1 и первыми входами элементов ИЛИ, 10.1 и И/И-НЕ 11.1. Выход элемента 2-2И-ИЛИ 7.1 является первым 26.1 информационным выходом устройства. Выход элемента 2-2И-ИЛИ 8.1 соединен с инверсным S-входом триггера 6.2. Выход элемента 2-2И-ИЛИ 9.1 соединен с вторым входом элемента И 18.1, выход которого соединен с 1-входом триггера 6.2. Выход элемента И 19.2 соединен с «--входом триггера 6.2.

Прямой выход триггера 6.2 соединен с первым входом элемента ИЛИ 17.2, выход

которого соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 7.1, вторым входом первой группы входов элемента 2-2И-ИЛИ 7.2, вторым входом второй группы входов элемента 2-2И- ИЛИ 9.3, с вторыми входами элементов И

18.2и 19,2, третьим входом элемента И 18.3 и с третьим входом элемента И 18.4. Выход Отказ триггера 6.2 соединен с вторым входом элемента ИЛИ 17.2. Выход Отсутствие отказа триггера 6.2 соединен с вторыми входами элементов ИЛИ 10.1 и И/И-НЕ 11.1. Выход элемента ИЛИ 10.1 соединен с первым входом элемента И 13. Прямой выход элемента И/И-НЕ 11.1 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 8.1, входов первой группы входов элемента 2-2И-ИЛИ 9.2, первым входом первой группы входов элемента 2-2И-ИЛИ 7.2 и с первыми входами элементов ИЛИ 10.2 и И/И-НЕ 11.2. Выход элемента 2-2И-ИЛИ 7.2 является вторым информационным выходом 26.2 устройства. Выход элемента 2-2И-ИЛИ 8.2 соединен с инверсным S-входом триггера 6.3, Выход элемента 2-2И-ИЛИ 9.2 соединен с третьим входом элемента И 18.2,

Выход элемента И 18.2 соединен с I- входом триггера 6.3, К-вход которого соединен с выходом элемента И 19.2. Прямой выход триггера 6.3 соединен с первым входом элемента ИЛИ 17.3, выход которого соединен с вторым входом элемента И 18.3, вторым входом второй группы входов элемента 2-2И-ИЛИ 7,2, вторым входом первой группы входов элемента 2-2И-ИЛИ 7.3, первым входом второй группы входов элемента 2-2И-ИЛИ 9.3 и с первым входом элемента И 18.4. Выход Отказ триггера 6.3 соединен с вторым входом элемента ИЛИ

17.3и первым входом элемента ИЛИ 15, Выход Отсутствие отказа триггера 6.3 соединен с вторыми входами элементом ИЛИ 10.3 и И/И-НЕ 11.3. Выход элемента ИЛИ 10.3 соединен с вторым входом элемента И 13. Прямой выход элемента И/И-НЕ 11.2 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 8,2, входом первой группы входов элемента 2-2И-ИЛИ

9.3,первым входом первой группы входов элемента 2-2И-ИЛИ 7.3 и с первыми входами элементов ИЛИ 10.3 и И/И-НЕ 11.3. Выход элемента 2-2И-ИЛИ 7.3 является третьим информационным выходом 26,3 устройства. Выход элемента 2-2И-ИЛИ 8.3 соединен с инверсным S-входом триггера

6.4,Выход элемента 2-2И-ИЛИ 9.3 соединен с вторым входом элемента И 19,3.

Выход элемента И 18.3 соединен cl-вхс- дом триггера 6.4, К-вход которого соединен

с выходом элемента И 19.3. Прямой выход триггера 6:4 соединен с первым входом элемента ИЛИ 17.4, выход которого соединен с вторым входом элемента И 18.4,

вторым входом второй группы входов элемента 2-2И-ИЛИ 7.3 и с вторым входом первой группы входов элемента 2-2И-ИЛИ 7.4. Инверсный выход триггера 6.4 соединен с вторым входом второй группы входов эле0 мента2-2И-ИЛИ9.1. Выход Отказ триггера 6.4 соединен с вторым входом элемента ИЛИ 17.4 и вторым входом элемента ИЛИ 15. Выход Отсутствие отказа триггера 6.4 соединен с вторыми входами элементов

5 ИЛИ 10.3 и И/И-НЕ 11.3. Выход элемента ИЛИ 10.3 соединен с третьим входом элемента И 13. Прямой выход элемента И/И- НЕ 11 3 соединен с первым входом первой группы входов элемента 2-2И-ИЛИ 7.4,

0 первым входом элемента ИЛИ 12, первым входом элемента И 14, первым входом второй группы входов элемента 2-2И-ИЛИ 8.3 и с первым входом второй группы входов элемента 2-2И-ИЛИ 9.1. Инверсный выход

5 элемента И/И-НЕ 11.3 соединен с первым входом второй группы входов элемента 2- 2И-ИЛИ 7.4 и с первым входом элемента И 20, выход которого соединен с инверсным S-входом триггера 6.5. Выход элемента 20 2И-ИЛИ 7.4 является четвертым информационным выходом 26.4 устройства.

Выход элемента И 18.4 соединен с (-входом триггера 6.5, К-вход которого соединен с выходом элемента И 19.4, Прямой выход

5 триггера 6.5 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 7.4. Инверсный выход триггера 6.5 соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 9.1 и вторым входом вто0 рой группы входов элемента 2-2И-И ЛИ 9.2. Выход Отсутствие отказа триггера 6.5 соединен с вторыми входами элементов ИЛИ 12 и И 14. Выход элемента ИЛИ 12 соединен с четвертым входом элемента И 13, выход

5 которого является выходом 27 Отсутствие отказа устройства. Выход элемента ИЛИ 15 соединен с первым входом первой группы входов элемента 2-2И-ИЛИ 9.1. Выход элемента И 14 является выходом 28 Отсутст0 вне частичного отказа устройства.

Триггер каждого разряда (фиг.2) содержит первый 29 и второй 30 элементы И- ИЛИ-НЕ, первый 31 и второй 32 элементы И, первый-четвертый 33-36 элементы И5 НЕ, первый 37 элемент НЕ, третий элемент И 38, второй элемент НЕ 39, четвертый элемент И 40, элемент И/И-НЕ 41 и элемент 7И-ИЛИ/7И-ИЛИ-НЕ 42.

R-вход 43 триггера каждого разряда (фиг,2) соединен с первым входом элемента

И 40, вторым входом первой и первым входом второй групп входов элемента И-ИЛИ- НЕ 29, с первым входом элемента И 31 и первым входом элемента И-НЕ 36. 1-вход 44 триггера каждого разряда соединен с третьим входом второй группы входом элемента И-ИЛИ-НЕ 29, вторым входом элемента И/И-НЕ 41 и вторым входом третьей группы входов элемента 7И-ИЛИ/7И- ИЛИ-НЕ 42.Синхровод 45 триггера каждого разряда соединен с четвертым входом второй группы входов элемента И-ИЛИ-НЕ 29, первым входом первой группы входов элемента И-ИЛИ-НЕ 30 и с входом элемента НЕ 37. К-вход 46 триггера каждого разряда соединен с вторым входом первой группы входов элемента И-ИЛ1Л-НЕ 30, первым входом элемента И/И-НЕ 41 и с первым входом четвертой группы входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42. S-вход 47 триггера каждого разряда соединен с четвертым входом первой и первым входом второй групп в.ходов элемента И-ИЛИ-НЕ 30, с третьим входом элемента И 32 и третьим входом элемента И-НЕ 35, Рр-вход.48 триггера каждого разряда соединен с первым входом седьмой группы входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42. Выход элемента И-ИЛИ-НЕ 29 соединен с вторым входом элемента И 32 и вторым входом второй группы входов элемента И-ИЛИ-НЕ 30, выход которого соединен с вторым входом элемента И 31 и первым входом первой группы входов элемента И-ИЛИ-НЕ 29. Выход элемента И 31 соединен с первым входом элемента И-НЕ 33, третьим входом второй, вторым входом четвертой и с вторым входом пятой групп входов элемента 7И- ИЛИ/7И-ИЛИ-НЕ 42. Выход элемента И 32 соединен с вторым входом элемента И-НЕ 34, четвертым входом первой, первым входом третьей и с вторым входом шестой групп входов элемента 7И-ИЛИ/7И-ИЛИ- НЕ 42. Выход элемента И-НЕ 33 соединен с вторым входом элемента И-НЕ 35, первым входом элемента И 38 и первым входом элемента И 32. Выход элемента И-НЕ 34 соединен с вторым входом элемента И-НЕ 36, вторым входом элемента И 38 и третьим.входом элемента И 31. Выход элемента НЕ 37 соединен с вторым входом элемента И-НЕ 33, первым входом элемента И-НЕ 34, третьим входом первой и с вторым входом второй групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42. Выход элемента И 38 соединен с входом элемента Н Е 39 и третьим входом третьей, четвертой, пятой и шестой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42. Выход элемента НЕ 39 соединен с вторым входом первой и

первым входом второй групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42. Выход элемента И 40 соединен с пятыми входами первой и второй, с четвертыми входами

третьей, четвертой, пятой и шестой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42. Инверсный выход элемента И/И-НЕ 41 соединен с пятыми входами третьей и четвертой групп входов элемента 7ИИЛИ/7И-ИЛИ-НЕ 42. Прямой выход элемента И/И-НЕ 41 соединен с пятыми входами пятой и шестой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42, прямой выход которого является выходом Отказ

триггера и соединен с вторым входом своей седьмой группы входов. Инверсный выход элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42 является выходом 51 Отсутствие отказа триггера каждого разряда. Выход элемента И-НЕ 35

является прямым выходом триггера каждого разряда и соединен с третьим входом элемента И-НЕ 36, третьим входом первой группы входов элемента И-ИЛИ-НЕ 30 и первыми входами первой и пятой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42. Выход элемента И-НЕ 36 является инверсным выходом 50 триггера и соединен с вторым входом второй группы входов элемента И- ИЛИ-НЕ 29, первым входом элемента И-НЕ

35, четвертым входом второй и с первым входом шестой групп входов элемента 7И- ИЛИ/7И-ИЛИ-НЕ 42.

Рассмотрим функциональное назначение элементов логической структуры предлатаемого двоично-десятичного счетчика.

Разряды 1-4 являются основными разрядами двоично-десятичного счетчика, выполняющими заданный набор функций устройства. Разряд 5 является резервным

разрядом двоично-десятичного счетчика и предназначен для автоматического замещения одного из основных разрядов при его отказе.

Триггеры 6.1-6.5 предназначены для хранения числа накопленных импульсов, поступивших на синхровходы 21 и 22 устройства при разрешении их счета. Кроме этой функции в структуре каждого триггера

имеются средства встроенного контроля, которые позволяют непрерывно контролировать правильность срабатывания всех логических элементов триггера каждого разряда.

Первые элементы 2-2И-ИЛИ 7.1-7.4 предназначены для коммутации на соответствующие информационные выходы 26.1-26.4 устройства значений сигналов с прямых выходов триггеров данного или последующего разрядов.

Вторые элементы 2-2И-ИЛИ 8.1-8.3 и элемент И 20 осуществляют коммутацию входа предустанова 25.1-25.4 на инверсный вход триггера данного или последующего разряда, в зависимости от его исправного (или неисправного) состояния. Третьи элементы 2-2И-ИЛИ 9.1-9.3 обеспечивают алгоритм функционирования двоично-десятичного счетчика, учиты-. вая работоспособность соответствующих триггеров разрядов.

Элементы ИЛИ 10.1-10.3 и 12 предназначены для обобщения сигналов Отсутствие отказа триггеров 6.1-6.5 разрядов,

Элементы И/И-НЕ 11.1-11.3 используются для формирования функций учета исп- равного (неисправного) состояния триггеров одноименного и всех предыдущих разрядов На прямом и инверсном выходах элемента И/И-НЕ . формируются соответственно функции FiAp2 и Fit/F2 (где FI, имея значение логической единицы, означает исправность соответствующего триггера; FI, имея значение логического нуля, означает неисправность соответствующего триггера). Соответственно на выходах эле- мента И/И-НЕ 11.2 формируются функции Fr Р2 Рз и FiV F2vF3,-a на выходах элемента И/И-НЕ 11.3 формируются Р1лР2лРзлР4 и FivF2vF3VF4.

Элемент И 13 обобщает сигнал Отсутствие отказа во всех триггерах 6.1-6.5 разрядов и формирует на своем выходе сигнал Отсутствие отказа устройства в целом.

Элемент И 14 формирует на своем выходе сигнал Отсутствие частичного отказа означающего, что в устройстве нет отказавшего ни одного триггера разрядов. При отказе хотя бы одного из триггеров 6.1 - 6.5 на выходе элемента И 14 формируется нулевой логический потенциал, сигнализирующий о наличии частичного отказа в устройстве.

Элементы ИЛИ 17.1-17.4 предназначены для блокировки значения логического уррвня сигнала на прямом выходе отказавшего триггера на логику работы исправных элементов устройства.

Первые 18.1-18,4 и вторые 19.1-19.4 элементы И являются входной логикой I- и К-входов триггеров разрядов двоично-десятичного счетчика.

Элементы И-ИЛИ-НЕ 29 и 30, И 31 и 32, НЕ 37 и И-НЕ 33 и 34 образуют схему вспомогательного триггера с входной логикой работы IK-или RS-триггера (фиг.2).

Элементы И-НЕ 35 и 36 образуют схему основного триггера каждого разряда.

Элемент НЕ 37 предназначен для организации двухтактного режима работы 1Ктриггера при наличии одного тактового входа 45. Кроме того, на выходе элемента НЕ 37 вырабатывается сигнал разрешения сравнения сигналов на противоположных

плечах (выходах) основного и всдрмогатель- ного триггеров (фиг.2 точки А и Q, точки А и Q) в режиме хранения информации.

Элемент И 38 обеспечивает контроль наличия сигнала запрета работы основно0 го триггера и формирует на своем выходе сигнал строба сравнения, задержанного относительно положительного фронта тактового сигнала С на время не менее ЗТСр (где ТСр - время срабатывания одного

5 логического элемента структуры триггера), т.е. на время срабатывания элементов НЕ 37, И-НЕ 33 и 35, а также на время срабатывания самого элемента И 38. Особенностью элемента И 38 является то, что его время

0 срабатывания должно быть не менее ТСр, т.е. если для остальных логических элементов структуры IK-триггера время срабатывания возможно не более ТСр, то для элемента И 38 оно должно быть не менее ТСр. Данное

5 ограничение можно выполнить при разработке технологии микросхемы.

Элемент НЕ 39 предназначен для формирования на своем выходе сигнала строба сравнения, задержанного на время 4ТСр от0 носительно отрицательного фронта тактового сигнала С

Элемент И 40 предназначен для формирования сигнала запрета сравнения во второй, третьей, четвертой, пятой, шестой и

5 первой группах входов элемента 7И- ИЛИ/7И-ИЛИ-НЕ 42 в момент асинхрон; ной установки IK-триггера по его входам R 43 и S 47, соответственно, в нулевое или единичное состояние.

0Элемент И/И-НЕ 41 на своих прямом и

инеерсном.выходах формирует сигнал функций I K и I v К, которыми открываются соответственно пятая и шестая, а также третья и четвертая группы входов элемента 7И5 ИЛИ/7И-ИЛИ-НЕ 42, который осуществляет на своих группах входов контроль правильности срабатывания всех логических элементов структуры IK-триггера. В случае нарушения логики функционирова0 ния (отказ какого-либо логического элемента структуры триггера) на прямом выходе элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42 формируется сигнал Отказ, который посредством своей обратной связи через второй вход

5 седьмой группу входов осуществляет так называемый эффект самозахвата , т.е., устанавливается в устойчивое состояние логической единицы.

В общем случае на входах элемента 7И ИЛИ/7И-ИЛИ-НЕ 42 реализуется функционал отказа, который можно представить следующим аналитическим выражением:

F - (CIKRS) AV (CIKRS) A V (CIKRS) А QV(CIKRS) -А СКС A-Q/R-SVC A-Q-R S, (1) 5

где С, С - единичное и нулевое состояние тактового сигнала на С-входе 45 IK-тригге- ра;

I, I - единичное и нулевое состояние сигнала.на входе 44 IK-триггера;10

К, К - единичное и нулевое состояние сигнала на К-входе 46 IK-триггера;

R - единичное состояние сигнала на R- входе 43 1К-триггера;

S - единичное состояние сигнала на S- 15 входе 47 IK-триггера;

А, А - единичное и нулевое состояние сигналов соответственно в точках А и А на фиг.2;

Q, Q - состояния сигналов на прямом 49 20 и инверсном 50 выходах 1К-триггера.

Триггер каждого разряда в процессе функционирования двоично-десятичного счетчика работает следующим образом.

После включения питания на Rp-вход 48 25 триггера каждого разряда подается нулевой уровень сигнала для установки в исходное состояние средств функционального контроля, так как в силу случайного характера переходных процессов во время включе- 30 ния питания элемент 7И-ИЛ1/1/7И-ИЛИНЕ 42 с обратной связью (однофазный триггер) может установиться в единичное состояние на своем прямом выходе, соответствующее сигналу отказ любого из 35 триггеров разрядов.

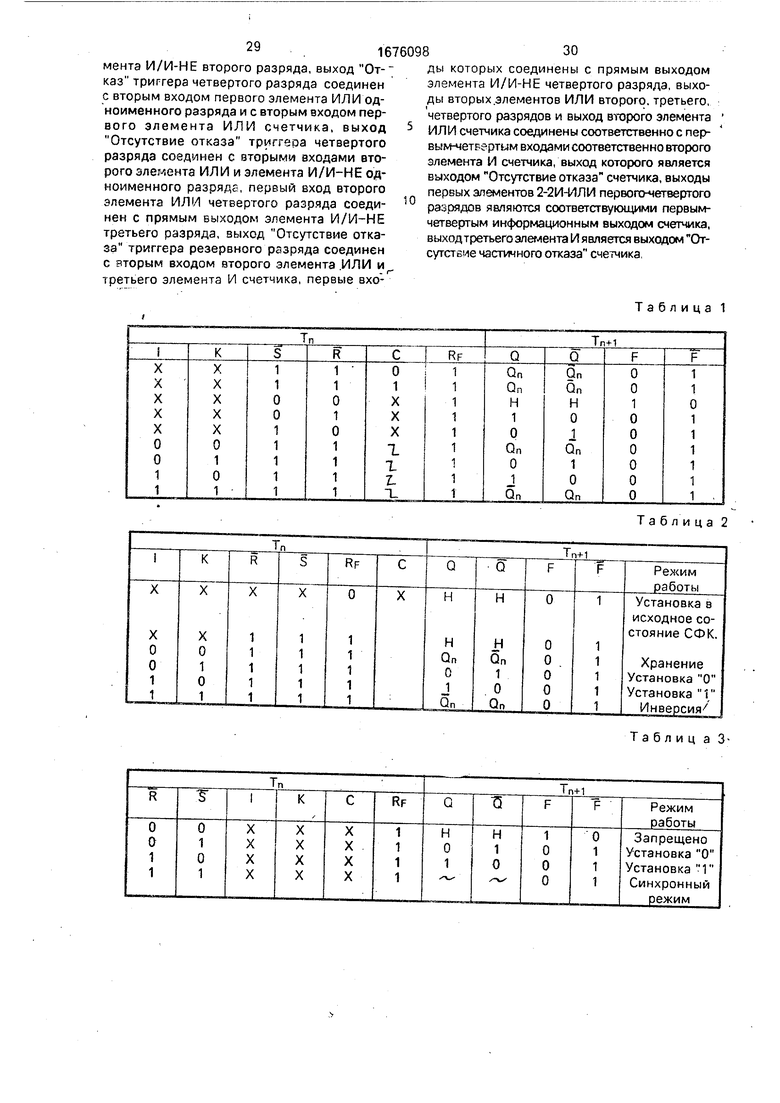

Далее, при исправном состоянии всех логических элементов, работа триггера каждого разряда подчиняется (соответствует) закону функционирования, приведенному в 40 сокращенной табл.1 переходов IK-триггера.

Из табл.1 видно, что IK-триггер работает в двух режимах: в синхронном режиме IK-триггера и в асинхронном режиме RS- триггера.45

Рассмотрим подробнее каждый из режимов работы универсального fK-триггера каждого разряда и работу элементов функционального контроля за правильностью срабатывания основных логических эле- 50 ментов триггера в ходе его функционирования,

В синхронном режиме работы IK-триггер каждого разряда функционирует в соответствии с табл.2 переходов.55

В процессе своего функционирования первая ступень IK-триггера подчиняется закону, представленному следующими аналитическими выражениями:

. A 1 -IKC/RS/VIKAC/RS/; A 1 IKC/RS/VIKAC/RS/,(2)

где I, I - единичное и нулевое соответственно состояния сигналов на l-входе IK- триггер а;

К, К - единичное и нулевое соответственно состояния сигналов на К-входе IK- триггера;

С - единичное состояние сигнала на тактовом входе IK-триггера;

R - единичное состояние сигнала на R- входе триггера;

S - единичное состояние сигнала на S- входе триггера;

А, А - единичное состояние сигнала на выходах элементов И 31 и 32 IK-триггера.

В табл.1 и 2 приняты следующие сокращения: I - вход 44 IK-триггера; К- вход К 46 IK-триггерз; R - вход R 43 IK-триггера; S - вход S 47 К-триггера; С - тактовый вход С 45 IK-триггера; RF - вход 48 установки в исходное состояние средств функционального контроля (СФ К);IK-триггера; Q- прямой выход 49 триггера; Q - инверсный выход 50 триггера; F - выход 51 Отсутствие отказа триггера, F- выход 52 Отказ IK-триггера; X - информация низкого или высокого логического уровня на соответствующем входе триггера; Qn, Qn - предыдущее состояние сигнала на прямом и инверсном соответственно выходе триггера; Тп - момент времени до подачи отрицательного фронта тактового импульса; Тп+1 - момент времени после подачи отрицательного фронта тактового импульса; Н- неопределенное состо; яние сигнала на соответствующем выходе триггера; 1.- переход от высокого уровня сигнала к низкому на С-входе 45 триггера.

За выполнением условий выражения (2) следят четвертая, пятая, шестая и третья структуры (группы входов) элемента 7И- ИЛИ/7И-ИЛИ-НЕ42.

В процессе своего функционирования вторая ступень IK-триггера (основной триггер) подчиняется закону, представленному следующими аналитическими выражениями:

Q 1 A 1 A С, (3)

За выполнением условий выражения (3) следят первая и вторая группы входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42.

Функционал отказа любого из логических элементов первой ступени (вспомогательного триггера), реализованный в предлагаемом техническом решении IK-триггера каждого разряда, можно представить следующим аналитическим выражением:

F IKC(RS) IKC(RS) -A IKAQ(RS) CVlKAQ(RS) -C,(4)

В случае нарушения условий функционирования, представленных в выражении (2) на выходе (прямом) элемента 7И ИЛИ/7И-ИЛИ-НЕ 42 уже в момент срабатывания логических элементов первой ступени вырабатывается сигнал Отказ IK- триггера.

Функционал отказа любого из логических элементов второй ступени (основного триггера), реализованный в техническом решении IK-триггера каждого разряда, можно представить выражением

F Q-A -CVQ -А-С.(5)

В случае нарушения условий функционирования, представленных в выражении (3), на выходе (прямом) элемента 7И- ИЛИ/7И-ИЛИ-НЕ 42 также выраЈатывзет- ся сигнал Отказ (К-триггера.

Рассмотрим последовательность срабатывания всех элементов логической стурктуры предлагаемого I К-триггера в его четырех основных режимах функционирования: хранение, установка О, установка инверсия.

В режиме хранения (табл.2, п.3)с приходом положительного фронта тактового импульса на С-вход триггера каждого разряда изменение состояния во вспомогательном триггере не производится. Это обусловлено следующим образом. Примем, что предыдущее состояние IK-триггера было единичным, Тогда при нулевых логических уровнях сигнала на-1- и К-входах и единичных уровнях сигналах на R-, S- и RF-ВХОДЭХ будут закрыты вторые группы входов элементов И-ИЛИ-НЕ 29 и 30, а открыты первые структуры И элементов И-ИЛИ-Н Е 29 и 30. Таким образом, срабатывание вспомогательного триггера не происходит. Контроль правильности хранения предыдущего состояния в IK-триггере каждого разряда происходит следующим образом. В результате выполнения триггером режима хранения состояний основного и вспомогательного триггеров должны совпадать. В предлагаемом устройстве это осуществляется первой и второй группами входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42 (фиг.2), на входе которых подаются сигналы с противоположных плеч основного и вспомогательного триггеров (точки А и Q, А и Q на фиг.2 соответственно), а также сигнал разрешения проведения сравнения при тактовом сигнале С 0 с выхода элемента НЕ 37 и после допустимого времени срабатывания всех элементов основного и вспомогательного триггеров, равного 4Тср,

с выхода элемента НЕ 39. При исправном функционировании всех основных логических элементов триггера каждого разряда на выходе 52 присутствует сигнал низкого

логического уровня и в противном случае триггер 42 формирует на своем прямом выходе высокий логический уровень сигнала.

При установке IK-триггера в состояние

0 О (табл.2, п.4) с приходом положительного фронта синхроимпульса на входе 45 производится запись нулевого состояния во вспомогательный триггер и, на время действия его высокого уровня, в основ5 ном триггере хранится предыдущее состояние, так как с выхода элемента НЕ 37 на входы элементов И-НЕ 33 и 34 поступает нулевой логический уровень сигнала, блокирующий возможное воздействие

0 переходных процессов в элементах И- ИЛИ-НЕ 29 и 30, И 31 и 32 вспомогательного триггера на состояние основного триггера (элементы И-НЕ 35 и 36). Срабатывание элементов вспомогательного тригге5 ра происходит следующим образом. При предыдущем единичном состоянии триггера каждого разряда вторая группа входов элемента И-ИЛИ-НЕ 30 открыта и на его выходе через время ТСр будет установлен

0 сигнал нулевого логического уровня. Первая и вторая группы входов элемента И- ИЛИ-НЕ 29 будут закрыты нулевыми потенциалами с выхода элемента И-НЕ 36 и с выхода элемента И-ИЛИ-НЕ 30. Через

5 время 2ТСр с момента поступления положительного фронта синхроимпульса на вход 45, на выходах элементов И-НЕ 33 и 34 установится высокий логический уровень сигнала. Таким образом, через время

0 2ТСр с момента поступления положительного фронта синхроимпульса на входах элементов И 31 и 32 присутствуют следующие сигналы: элемент И 31 будет закрыт нулевым логическим уровнем сигнала с вы5 хода элемента И-ИЛИ-НЕ 30, элемент И 32 пропустит на свой выход высокий логический уровень сигнала, так как на его входах будут присутствовать все высокие логические уровни сигналов (с выхода эле0 мента 33, с выхода элемента И-ИЛИ- НЕ 29 и с S-входа триггера). Следовательно, через время ЗТСр на выходе элемента И 31 (см. А на фиг.З) будет установлен сигнал нулевого логического уровня, а на выходе

5 элемента И 32 (А на фиг.З) - высокий логический уровень сигнала.

Контроль правильности срабатывания основных элементов вспомогательного триггера будет осуществлен следующим образом. Через время, несколько большее,

чем ЗТср на выходе элемента И 38, появится высокий логический уровень сигнала, который является стробом сравнения третьей и четвертой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42, осуществляющих контроль правильности срабатывания логических элементов вспомогательного триггера, Если в результате срабатывания основных логических элементов вспомогательного триггера будет выполнено условие:

(RS) -С -( К) ,(6)

где R - единичный логический уровень сигнала на R-входе триггера;

S - единичный логический уровень сигнала на S-входе триггера;

С - единичный уровень сигнала на С- входе триггера;

К - единичный уровень сигнала на К- входе триггера;

I - единичный уровень сигнала на 1-вхо- де триггера;

А - единичный уровень сигнала на выходе элемента И32, то первая ступень (элементы вспомогатель- ного триггера) сработала правильно и на прямом выходе элемента 7И-ИЛИ/7И- ИЛИ-НЕ 42 присутствует сигнал логического О. При неправильном срабатывании (отказе какого-либо из основных элементов вспомогательного триггера) равенство (6) нарушается и элемент 7И-ИЛИ/7И-ИЛИ- НЕ 42 пропускает высокий логический уровень сигнала на свой прямой выход и устанавливается в устойчивое единичное состояние, сигнализируя о возникновении отказа. На выходе 52 (F) триггера любого из разрядов формируется сигнал Отказ, означающий, что первая ступень (К-триггера сработала неправильно.

Функционирование и контроль правильности срабатывания основных логических элементов основного триггера в этом режиме производится следующим образом. По окончании действия сигнала на тактовом входе 45 и при правильном срабатывании элементов вспомогательного триггера на одном из элементов И-НЕ 33 и 34 формируется сигнал логического О, который установит сигнал на выходе элемента И 38 в одноименное состояние, что приведет к формированию высокого логического уровня сигнала на выходе элемента НЕ 39, т.е. к формированию строба сравнения через время 4Тср с момента поступления отрицательного фронта тактового сигнала. Одновременно с этим появление сигнала логического О на выходе одного из элементов И-НЕ 33 и 34, а для рассматриваемого примера сигнал логического нуля присутствует на выходе элемента И-НЕ 34, приведет к формированию единичного состояния на выходе элемента И-НЕ 36, что соответствует необходимому значению логического

сигнала на выходе 50 (Q), т.е. режиму Установка нуля. Через время 4Тср закончится переходный процесс установки в нулевое состояние сигнала на выходе элемента И-НЕ 35. Таким образом, через время 4Тср с

0 момента поступления на вход 45 триггера каждого разряда отрицательного фронта синхросигнала в основном триггере (элементы И-НЕ 35 и 36) заканчиваются переходные процессы и на первой и

5 второй группах входов элемента 7И- ИЛЙ/7И-ИЛИ-НЕ 42 производится контроль состояний противоположных плеч вспомогательного и основного триггеров (сигнал в точке А с сигналом на выходе 50 и

0 в точке А с сигналом на выходе 49). При правильном срабатывании основного триггера на прямом выходе элемента 7И- ИЛИ/7И-ИЛИ-НЕ 42 присутствует сигнал логического нуля, в противном случае выра5 батывается сигнал логической единицы, означающий отказ одного из элементов И-НЕ 35 и 36 основного триггера.

В режиме установки триггера каждого разряда в 1 (табл.2, п.5) с приходом поло0 жительного фронта синхроимпульса на вход 45 (фиг.За) производится запись единичного состояния во вспомогательный триггер и, на вермя действия синхроимпульса, основной триггер переводится в

5 режим хранения предыдущего состояния, так как с выхода элемента НЕ 37 на входы элементов И-НЕ 33 и 34 поступает нулевой логический уровень сигнала, блокирующий возможное воздействие переходных

0 процессов в логических элементах вспомогательного триггера на состояние основного триггера. Срабатывание логических элементов вспомогательного триггера производится следующим образом.

5 При предыдущем нулевом состоянии IK- триггера на выходе элемента И-ИЛИ-НЕ 29 через время 2ТСр будет сформирован нулевой логический уровень сигнала, а на выходе элемента И-ИЛИ-НЕ 30 - высокий

0 логический уровень сигнала. В результате этого элемент И 32 закрыт нулевым уровнем сигнала с выхода элемента И-ИЛИ-НЕ 29, а элемент И 31 - открыт, т.е. через время ЗТСр, при правильном срабатывании эле5 ментов вспомогательного триггера, в точке А устанавливается высокий логический уровень сигнала, а в точке А - нулевой логический уровень сигнала.

Контроль правильности срабатывания логических элементов вспомогательного

триггера в этом режиме осуществляется следующим образом. Через такое же время ЗТСр на выходе элемента И 38 формируется высокий логический уровень сигнала, который для пятой и шестой групп входов элемента 7И-ИЛИ/7И-ИЛЙ-НЕ 42 является стробом сравнения. Если же в результате срабатывания основных элементов вспомогательного триггера будет выполнено условие:

(RS) С -(IK) ,(7)

где R - единичный сигнал на R-входе триггера;

S - единичное состояние сигнала на S- входе триггера;

С - единичный сигнал на С-входе триггера;

I - единичный сигнал на 1-входе триггера;

К - нулевой сигнал на К- входе триггера;

А - единичный сигнал на выходе элемента И 31, то элементы вспомогательного триггера сработали правильно и на выходе элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42 будет присутствовать сигнал логического О. При неправильном срабатывании (отказе) какого-либо из основных логических элементов вспомогательного триггера равенство (7) нарушается и четвертая группа входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42 пропускает на его прямой выход высокий логический уровень сигнала, что приводит к формированию устойчивого сигнала Отказ на выходе 52 триггера любого из разрядов.

Функционирование и контроль правильности срабатывания основных логических элементов основного триггера в это,м режиме производится следующим образом. По окончании действия сигнала на входе 45 (фиг.З, Vc) и при правильном срабатывании вспомогательного триггера элементом И-НЕ 33 формируется сигнал логического О, который установит выходы элементов И 38 и И-НЕ 35 в соответствующие логические состояния. На выходе эле мента И 38 будет сформирован сигнал логического О, который приведет к формированию на выходе элемента НЕ 39 сигнала высокого логического уровня. Этот сигнал будет сформирован с задержкой на 4Тср по отношению к моменту появления отрицательного фронта тактового импульса. На выходе элемента И-НЕ 35 также через время ЗТСр сформируется сигнал логической единицы, который через время 4ТСр приводит к формированию сигнала логического нуля на выходе элемента И-НЕ 36. Таким образом, через время 4ТСр на выходах 49 и 50 триггера будет сформированы соответственно высокий и низкий логические уровни сигналов, что будет соответствоватьзаданномурежиму

функционирования IK-триггера, т.е. режиму Установка 1. Таким образом, через время 4ТСр с момента поступления на вход 45 IK-тоиггеоа отрицательного фронта тактового сигнала в основном триггере заканчиваются переходные процессы и на первой и второй группах входов элемента 7И- ИЛИ/7И-ИЛИ-НЕ 42 по стробу сравнения с выхода элемента НЕ 39 производится контроль правильности срабатывания

его логических элементов И-НЕ 35 и 36. При правильном срабатывании на выходе (прямом) элемента 7И- ИЛИ/7И-ИЛИ-НЕ 42 вырабатывается сигнал логического О, в противном случае - сигнал логической

1.

В режиме инверсии состояния триггера каждого разряда (табл.2, п.6), или, как его еще называют, режиме счета с приходом положительного фронта синхроимпульса на

вход 45 IK-триггера производится изменение предыдущего состояния триггера на противоположное. При исправном функционировании основных логических элементов IK-триггера должны быть

выполнены следующие равенства:

(RS) (IKQ- /V Q 1,(8)

(RS) -(IKC) А Q 1.(9)

Контроль правильности срабатывания основных логических элементов вспомогательного триггера в этом режиме осуществляется пятой и шестой группами входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42 в момент времени ЗТСр с момента появления положительного фронта тактового импульса.

Если равенства (8) и (9) не нарушаются, то сигнал Отказ на выходах 52 триггеров каждого разряда не формируется. При возникновении отказа одного из основных логических элементов вспомогательного триггера равенства (8 или 9) нарушаются и на выходах 52 триггеров разрядов формируется сигнал Отказ. Временная диаграмма работы устройства в этом режиме приведена на фиг.36. ,

Функционирование триггера каждого разряда в счетном режиме производится следующим образом. При подаче на входы IK-триггера сигналов согласно п.6 табл.2 и предыдущем единичном состоянии появление положительного фронта синхроимпульса на входе 45 приводит к срабатыванию элемента И-ИЛИ-НЕ 30, на выходе которого через время 2Тср формируется сигнал нулевого логического уровня. Через время

ЗТср в точке А установится одноименныйбого из разрядов. Далее осуществляется

логический уровень, а в точке Д - высокийконтроль состояний сигналов на противопологический уровень сигнала. Контрольложных плечах основного и вспомогательправильности срабатывания этих элемен-нрго триггеров (точка Ас выходом 50 и точка

тов производится сигналом с выхода эле-5 Ас выходом 49 триггера). Режим хранения

мента И 38, который сформируется такжебыл описан ранее.

через время ЗТср. Если все логические эле-Таким образом, в процессе подсчета менты сработали правильно, то пятая труп-импульсов триггер каждого разряда не- па входов элемента 7И-ИЛИ/7И-ИЛИ-НЕпрерывно контролируется на правиль- 42 не пропустит на его выход сигнал высо-10 ность срабатывания и, в случае отказа кого логического уровня, в противном слу-какого-либо из основных логических эле- чае будет сформирован сигнал Отказ ментов своей структуры, формирует на триггера на его выходе 52. Инверсия нуле-своем выходе Отказ сигнал высокого ло- вого состояния триггера каждого разрядагического уровня.

производится аналогичным образом, только15 Двоично-десятичный счетчик, содер- в этом случае нулевой логический уровеньжащий в каждом разряде описанный триг- сигнала будет сформирован в точке А иrep, работает следующим образом, контроль правильности срабатывания ос-Для установки двоично-десятичного новных логических элементов вспомога-счетчика в исходное состояние на вход 23 тельного триггера будет производиться20 (фиг. 1) устройства подается нулевой логиче- шестой группой входов элемента 7И-ский сигнал. При этом все триггеры 6.1-6.5 ИЛИ/7И-ИЛИ-НЕ 42. Контроль правильно-устанавливаются в нулевое состояние, сти срабатывания основных логическихПри исправном состоянии всех основ- элементов основного триггера аналогиченных триггеров 6.1-6.4 и полном режиме сче- ранее приведенным режимам работы IK-25 та от 0 до 9 на входы 25,1-25.4 подаются триггера при его установке в О и 1.сигналы логической 1. Так как на выходах

Таким образом, во всех четырех синх-51 триггеров 6.1-6.4 Отсутствие отказа

ронных режимах функционирования IK-присутствуют сигналы логической единицы,

триггера каждого разряда осуществляетсяа на выходах 52 Отказ - сигналы логичепостоянный контроль за достоверностью30 ского нуля, то единичными разрешающими

срабатывания его основных логическихсигналами открыты следующие элементы

элементов. В случае нарушения (отказа)устройства: первые группы входов первых

какого-либо из основных логических эле-элементов 2-2И-ИЛИ 7.1-7.4 (разрешена

ментов IK-триггера любого .из разрядов наподача на информационные выходы 26.1соответствующем выходе 52 формируется35 26.4 устройства значений логических сигнасигнал Отказ, который сигнализирует олов с прямых выходов триггеров 6.1-6.4

недостоверной работе соответствующегоодноименных разрядов), вторые группы

триггера разряда.входов вторых элементов 2-2И-ИЛЙ 8.1В асинхронном режиме функциониро-8.3 (разрешено прохождение сигналов с

вания IK-триггера, при управлении его со-40 входов 25.1-25.4 предустанова насоответстоянием сигналами на R- и S-входах,ствующие, одноименные, инверсные Sсрабатывание его логических элементоввходы триггеров 6.1-6,4), вторая группа

подчиняется закону функционированиявходов третьего элемента 2-2И-ИЛИ 9.1

RS-триггера, приведенному в табл.3 пере-первого разряда в момент счета импульсов

ходов.45 от 0 до 8 (разрешен перенос состояния

Контроль правильности срабатыва-значения сигнала с с единичного выхода

ния логических элементов основного итриггера 6.1 на 1-вход триггераб.2), первая

вспомогательного триггеров в этом режи-группа входов третьего элемента 2-2Име полностью перекрывается реализован-ИЛИ 9.2 второго разряда открыта в течение

ным контролем режима хранения для50 долного цикла счета значением функции FI

синхронной работы IK-триггера, а также 2), первая группа входов третьего элемента

режимами установки его в О и 1.2-2И-ИЛИ 9,3 третьего разряда открыта

также в течение полног о цикла счета значе При появлении нулевого потенциаланием функции РгР2 Рз. Одновременно с

на R- или 3-входе триггера на выходе эле-55 этим закрываются следующие элементы

мента И 40 формируется запрещающийустройства: вторая группа входов первых

сигнал, который бл.окирует первую-шес-элементов 2-2И-ИЛИ 7.1-7.4 (запрещена

тую группы входов элемента 7И-ИЛИ/7И-подача на информационные выходы

ИЛИ-НЕ 42 на момент действия нулевого26.1-26.4 устройства значений сигнапотенциала на R- или §-входе триггера лю-лов с прямых выходов триггеров последующих разрядов), первая группа входов эле- ментов-2И-ИЛИ 8.1-8.3 (запрещена подача сигналов с входов 25.1-25.4 предустанова устройства на инверсные S- входы триггеров последующих разрядов). Первая группа входов третьего элемента 2- 2И-ИЛИ 9.1 закрывается нулевым состояние с выхода элемента ИЛИ 15, вторая группа входов третьего элемента 2-2И- ИЛИ 9.2 закрывается нулевым состоянием функции FiVF2.

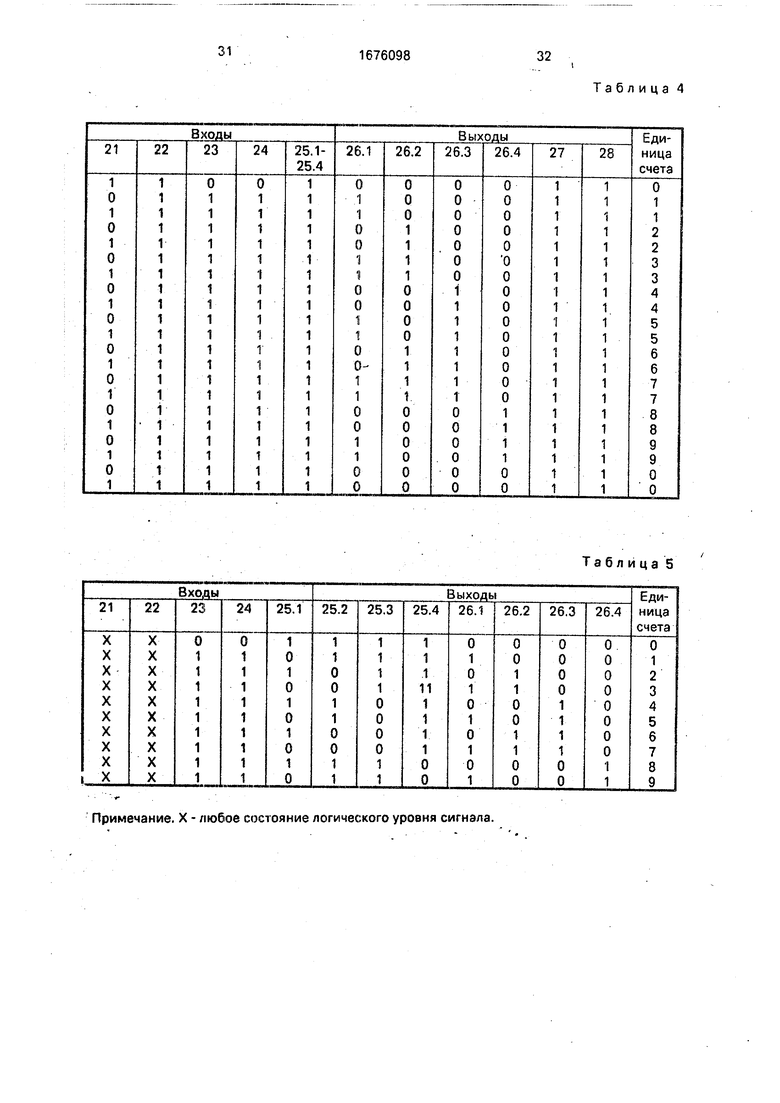

В табл.4 приведено состояние входов и выходов в режиме счета импульсов.

Счет синхроимпульсов, поступающих пои единичном состоянии логического сигнала на входе 22 с синхровхода 21, производится в полном соответствии с состоянием табл.1.

В табл.5 приведены значения состояний счетчика при использовании входов 25.1-25.4 предустанова и исправной работе основных триггеров 6.1-6.4.

При неисправном состоянии одного из триггеров 6.1-6.4 на соответствующем выходе Отказ триггера формируется сигнал логической 1, а на входе Отсутствие отказа - сигнал логического О.

Рассмотрим порядок перестройки логической структуры предлагаемого двоично- десятичного счетчика на примерах, когда произошел отказ триггера 6.1 и 6.3.

При отказе триггера 6.1 на выходе F Отказ этого триггера формируется высо- кий логический уровень сигнала, а на выходе F Отсутствие отказа - сигнал низкого логического уровня. Нулевой сигнал с выхода F триггера 6.1 закрывает первую группу входов элемента 2-2И-ИЛИ 7,1 и приводит к смене состояний сигналов на прямых и инверсных выходах элементов И/И-НЕ 11.1-11.3, на прямых выходах которых будет сформирован сигнал нулевого логического уровня, а на инверсных выходах - высокого логического уровня.

Одновременно с этим высокий логический уровень сигнала, поступая на первый вход элемента ИЛИ 17,1, блокирует возможное воздействие сигнала с прямого выхода отказавшего триггера 6.1 на другие элементы устройства. Нулевыми сигналами с прямых выходов элементов И/И-НЕ 11.1-11.3 закрываются первые группы входов элементов 2-2И-ИЛИ 7.2-7.4 (разрешается передача на информационные выходы 26.1-26.4 устройства значений состояний сигналов с прямых выходов триггеров 6.2- 6.5 последующих разрядов и запрещается передача на эти информационные выходы устройства сигналов с прямых выходов триггеров одноименных разрядов), открываются первые и закрываются вторые группы входов элементов 2-2И-ИЛИ 8.1-8.3 и открывается элемент И 20.4 (разрешается передача сигналов с входов 25.1-25.4 пред- установа устройства на инверсные S-входы триггеров последующих разрядов), открывается первая и закрывается вторая группы входов элемента 2-2И-ИЛИ 9.1, открывается вторая и закрывается первая группы вхо0 дов элемента 2-2И-ИЛИ 9.2, закрывается первая и открывается вторая группы входов элемента 2-2И-ИЛИ 9.3.

Подсчет импульсов, поступающих на первый синхровход 21 устройства произво5 дится по следующей логической ветви предлагаемого двоично-десятичного счетчика: с первого синхровхода 21 устройства через входной элемент И 16 на счетный вход тоиг- гера 6.2. Так как на его R-, Rp-, S-, I-, К-входах0 присутствуют единичные сигналы, то триг- -ер 6,2 работает в счетном режиме. Далее последующие состояния на прямом выходе триггера 5.2 передаются через элементы ИЛИ 17.2, первый 18.2 и второй 19.2 элемен5 ты И на I- и К-входы триггера 6.3. Элементы И 18.3 и 19.3 открыты единичным сигналом с выхода элемента ИЛИ 17.1 и с выхода элемента 2-2И-ИЛИ 9.2, так как на входах его второй группы входов присутствуют еди0 ничные сигналы с инверсного выхода элемента И/И-НЕ 11.1 и с инверсного выхода триггера 6.5. В этом случае при накоплении двоично-десятичным счетчиком девяти импульсов вторая группа входов элемента 25 2И-ИЛИ 9.2 закрывается нулевым сигналом с инверсного выхода триггера 6.5 и после состояния устройства, равного 9, он устанавливается в нулевое состояние, так как запрещен перенос единичного состояния с

0 триггера 6.2 в триггер 6.3. При поступлении пятого импульса на вход 21 устройства триггер 6.4 переходит в единичное состояние, так как на его I- и К- входах присутствует единичный сигнал с выходов первого 18.3 и

5 второго 19.4 элементов И (состояния триггеров 6,2 и 6.3 единичные, а на выходе элемента 2-2И-ИЛИ 9.3 присутствует единичный сигнал). Подобным же образом в единичное состояние при поступлении девятого

0 импульса счета на входе 21 устройства устанавливается триггер 6.5.

При отказе триггера 6.3 на его выходе F Отказ формируется единичный лЈгиче- ский уровень сигнала, а на выходе F От5 сутствие отказа - нулевой логический уровень сигнала. Данный триггер 6.3 исключается из работоспособной структуры двоично-десятичного счетчика следующим образом. Единичный потенциал с выхода отказ F триггера 6.3 поступает на второй

вход элемента ИЛИ 17.2, блокируя тем самым возможное воздействие сигнала с выхода отказавшего триггера на другие элементы устройства, На прямых выходах элементов И/И-НЕ 11.2 и 11.3 формируются нулевые сигналы, а на их инверсных выходах - сигналы высокого логического уровня. В результате этого единичными разрешающими сигналами открыты следующие логические элементы устройства: первые группы входов элементов 7.1 и 7.2 и вторые группы входов элементов 7.3 и 7.4, обеспечивая подачу на информационные выходы устройства 26.1 сигнала с выхода триггера 6.1 на 26.2 - с 6.2, на 26.3 - с 6.4 и на 26.4 - с 6.5; вторые группы входов элементов 8.1 и 8.2 и первая группа входов элемента 8.3, а также элемент 20, обеспечивая при этом подачу сигналов с входов предустанова 25.1, - на инверсный S-вход триггера 6.1, с входа 25.2 - на вход триггера 6.2, с входа 25.3 - на вход 6.4 и с входа 25.4 на вход 6.5.

Открыты первая группа входов элемента 2-2И-ИЛИ 9.1 до момента накопления девятого импульса в полном цикле счета, первая группа входов элемента 2-2И-ИЛИ

9.2в течение всего цикла счета, вторая группа элемента 2-2И-ИЛИ 9.3 в течение всего цикла счета. Одновременно с этим закрываются следующие элементы устройства: вторые группы входов элементов 2-2И-ИЛИ 7.1 и 7.2, первые группы входов элементов

7.3и 7.4, вторые группы входов элементов 2-2И-ИЛИ 8.1 и 8.2 и первая группа входов элемента 8.3, вторые группы входов элементов 9.1 и 9.2 и первая группа входов элемента 2-2И-ИЛИ 9.3.

Подсчет импульсов, поступающих на первый 21 синхровход устройства, производится по аналогичным логическим ветвям, что и в первом примере, состояние входов и выходов полностью соответствует состояниям, приведенным в табл.4.

Замена отказавших второгого и четвертого триггеров (6.2 и 6.4J производится ана- тогично рассмотренным примерам.

Таким образом, в предлагаемом двоично-десятичном счетчике осуществляется автоматическая перестройка логической структуры при отказе одного из разрядов, что создает возможность обеспечения работоспособности устройства автоматики и вычислительной техники на этапе эксплуатации без замены данного устройства и, следовательно, повышает его эксплуатационную надежность.

Формула изобретения

Двоично-десятичный счетчик, содержащий основные и резервный разряды, первые элементы И и ИЛИ счетчика, первый разряд содержит триггер, три элемента 22И-ИЛИ и элемент ИЛИ, второй разряд содержит триггер, три элемента 2-2И-ИЛИ; два элемента И, элемент И/И-НЕ и элемент ИЛИ, третий разряд содержит триггер, три элемента 2-2И-ИЛИ, два элемента И, эле0 мент И/И-НЕ и элемент ИЛИ, четвертый разряд содержит триггер, три элемента И, элемент И/И-НЕ и элемент ИЛИ, резервный разряд содержит триггер и два элемента И, первый и второй синхровходы счетчика

5 соединены соответственно с первым и вторым входами первого элемента И счетчика, выход которого соединен со счетными входами триггеров основных и резервного разрядов, вход установки в О счетчика со0 единен с R-входами триггеров каждого разряда, первый вход предустанова счетчика соединен с инверсным S-входом триггера первого разряда и с вторым входом первой группы входов второго элемента 2-2И-ИЛИ

5 первого разряда, второй,третий и четвертый входы предустанова счетчика соединены соответственно с первым входом второй группы входов второго элемента 2-2И-ИЛИ предыдущего разряда и, кроме

0 четвертого, с вторым входом первой группы входов второго элемента 2-2И-ИЛИ одноименного разряда, четвертый вход предустанова счетчика соединен с вторым входом третьего элемента И четвертого

5 разряда, первый вход которого соединен с инверсным выходом элемента И/И-НЕ и с первым входом второй группы входом первого элемента 2-2И-ИЛИ данного разряда, выходы первого и второго элементов И

0 каждого, кроме первого, разряда соединены соответственно с I- и К-входом триггера данного разряда, выход первого элемента ИЛИ счетчика соединен с первым входом первой группы входов третьего эле5 мента 2-2И-ИЛИ первого разряда, прямой выход триггера первого разряда соединен с первым входом первого элемента ИЛИ данного разряда, выход которого соединен с первым входом первого и второго элемен0 тов И второго разряда, с вторым входом первой группы входов первого элемента 2- 2И-ИЛИ первого разряда, с первым входом первого и второго элементов И третьего и четвертого разрядов, с «етвертым входом

5 первого и с первым входом второго элементов И резервного разряда, прямой выход триггера второго разряда соединен с первым входом первого элемента ИЛИ одноименного разряда, выход которого соединен с вторыми входами первого и второго

элементов И третьего разряда, с вторым входом второй группы входов первого элемента 2-2Й-ИЛИ первого разряда, с вторым входом первой группы входов первого элемента 2-2И-ИЛИ второго разряда, с вторым входом второй группы входов третьего элемента 2-2И-ИЛЙ третьего разряда, с третьим входом первого и с вторым входом второго элементов И четвертого разряда, а также с третьим входом первого элемента И резервного разряда, прямой выход триггера третьего разряда соединен с первым входом первого элемента ИЛИ одноименного разряда, выход которого соединен с вторым входом второй группы входов первого элемента 2-2И-ИЛ И второго разряда, с вторым входом первой группы входов первого, с первым входом второй группы входов третьего элементов 2-2И-ИЛИ третьего разряда, с вторым входом первого элемента И четвертого разряда и с первым входом первого элемента И резервного разряда, прямой выход триггера четвертого разряда соединен с первым входом первого элемента ИЛИ одноименного разряда, выход которого соединен с вторым входом первого элемента И резервного разряда, с вторым входом первой группы входов элемента 2- 2И-ИЛИ четвертого разряда и с вторым входом второй группы входов первого элемента 2-2И-ИЛИ третьего разряда, прямой выход триггера резервного разряда соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ четвертого разряда, выходы второго и третьего элементов 2-2 И- ИЛИ первого разряда соединены соответственно с инверсным S-входом .триггера и с вторым входом первого элемента И второго разряда, выходы второго и третьего элементов 2-2И-ИЛИ второгого разряда соединены соответственно с инверсным S-входом триггера и с третьим входом первого элемента И третьего разряда, выходы второгр и третьего элементов 2-2И-ИЛИ третьего разряда соединены соответственно с инверсным S-входом триггера и с вторым входом второго элемента И четвертого разряда, выход третьего элемента И четвертого разряда соединен с инверсным S-входом триггера резервного разряда, выход элемента И/И-НЕ второго разряда соединен с вторым входом второй группы входов второго элемента 2-2И-ИЛИ первого разряда, с входом первой группы входов третьего элемента 2-2И-ИЛИ, с первым входом первой группы входов первого элемента 2-2И- ИЛИ второго разряда и с первым входом элемента И/И-НЕ третьего разряда, инверсный выход элемента И/И-НЕ второго разряда соединен с первым входом второй

группы входов первого элемента 2-2И- ИЛИ, с первым входом первой группы входов второго элемента 2-2И-ИЛИ и с первым входом второй группы входов третьего элемента 2-2И-ИЛИ второго разряда, прямой выход элемента И/И-НЕ третьего разряда соединен с вторым входом второй группы входов второго элемента 2-2И-ИЛИ второго разряда, с первым входом первой группы

0 входов первого, с входом первой группы входов третьего элемента 2-2И-ИЛИ третьего разряда и с первым входом элемента И/И-НЕ четвертого разряда, инверсный выход элемента И/И-НЕ третьего разряда

5 соединен с первым входом второй группы входов первого и с первым входом первой группы входов второго элементов 2-2И- ИЛИ третьего разряда, прямой выход элемент И/И-НЕ четвертого разряда соединен

0 с первым входом второй группы входов третьего элемента 2-2И-ИЛИ первого разряда, с вторым входом второй группы входов второго элемента 2-2И-ИЛИ третьего разряда и с первым входом первой группы

5 входов элемента 2-2И-ИЛИ четвертого разряда, инверсный выход триггера четвертого разряда соединен с вторым входом второй группы входов третьего элемента 2-2И- ИЛИ первого разряда, инверсный выход

0 триггера резервного разряда соединен с вторым входом первой группы входов третьего элемента 2-2И-ИЛИ первого разряда и с вторым входом второй группы входов третьего элемента 2-2И-ИЛИ второго раз5 ряда, отличающийся тем, что, с целью повышения достоверности функционирования и автоматизации процесса восстановления работоспособности, во втором, третьем и четвертом разрядах до0 лолнительно содержит второй элемент ИЛИ, а также второй элемент И, второй и третий элементы И счетчика, причем триггер каждого, включая и резервный, разряда в своей структуре содержит два элемента

5 И-ИЛИ-НЕ, четыре элемента И, четыре элемента И-НЕ, два элемента НЕ, элемент И/И-НЕ и элемент 7И-И71И/7И-ИЛИ-НЕ. инверсный R-вход триггера каждого разряда соединен с вторым входом первой и с

0 первым входом второй групп входов первого элемента И-ИЛИ-НЕ, с первым входом четвертого элемента И, с первым входом первого элемента И и-с первым входом четвертого элемента И-НЕ, l-вход триггера

5 каждого разряда соединен с третьим входом второй группы входов первого элемента И-ИЛИ-НЕ, с вторым входом элемента И/И-НЕ и с вторым входом третьей группы входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ, вход синхронизации триггера каждого разряда соединен с четвертым входом второй группы входов первого и с первым входом первой группы входов второго элемента И-ИЛИ-НЕ, а также с входом первого элемента НЕ, К-вход триггера каждого разряда соединен с вторым входом первой группы входов второгого элемента И-ИЛИ-НЕ, с первым входом элемента И/И-НЕ с первым входом четвертой группы входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ, инверсный S-вход триггера каждого разряда соединен с четвертым входом первой и с первым входом второй групп входов второго элемента И-ИЛИ-НЕ, с вторым входом четвертого элемента И, с третьим входом второго элемента И и с третьим входом третьего элемента И-НЕ, Rp-вход установки в исходное состояние средств функционального контроля триггера каждого разряда соединен с первым входом седьмой группы входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ соединен с вторым входом второго элемента И и с вторым входом второй группы входов второго элемента И-ИЛИ-НЕ, выход которого соединен с вторым входом первого элемента И и с первым входом первой группы входов первого элемента И-ИЛИ-НЕ, выход первого элемента И соединен с первым входом первого элемента И-НЕ, с третьим входом второй, с вторым входом четвертой и с вторым входом пятой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ,, выход первого элемента НЕ соединен с вторым входом второго и с первым входом второго элементов И-НЕ, с третьим входом первой и с вторым входом второй групп входов элемента 7И- ИЛИ/7И-ИЛИ-НЕ, выход второго элемента И соединен с вторым входом второго элемента И-НЕ, с четвертым входом первой, с первым входом третьей и с вторым входом шестой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ, выход первого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ, с первым входом второго и с первым входом третьего элементов И,выход второго элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ, с вторым входом третьего элемента И и с третьим входом первого элемента И, выход третьего элемента И соединен с входом второго элемента НЕ, с третьим входом третьей, с третьим входом четвертой, с третьим входом пятой и с третьим входом шестой групп входов элемента 7И- ИЛИ/7И-ИЛИ-НЕ, выход второго элемента НЕ соединен с вторым входом первой и с первым входом второй групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ, выход четвертого элемента И соединен с пятыми

входами первой и второй, с четвертыми входами третьей-шестой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ, инверсный выход элемента И/И-НЕ соединен с пятыми входами третьей и четвертой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ, прямой выход элемента И/И-НЕ соединен с пятыми входами пятой и шестой групп входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ, выход

0 третьего элемента И-НЕ является прямым выходом триггера каждого разряда и соединен с третьим входом четвертого элемента И-НЕ, с третьим входом первой группы входов второго элемента И-ИЛИ-НЕ, с первым

5 входом первой и с первым входом пятой групп входов элемента 7И-ИЛИ/7И-ИЛИ- НЕ, выход четвертого элемента И-НЕ является инверсным выходом триггера и соединен с первым входом трет ьего элемен0 та И-НЕ, с вторым входом второй группы входов первого элемента И-ИЛИ-Н.Е, с четвертым входом второй и с первым входом шестой групп входов элемента 7И- ИЛИ/7М-ИЛИ-НЕ, инверсный выход кото5 рого является выходом Отсутствие отказа, прямой выход элемента 7И-ИЛИ/7И-ИЛИ- НЕ является выходом Отказ триггера каждого разряда и соединен с вторым входом своей седьмой группы входов, вход установ0 ки в исходное состояние средств функционального контроля устройства соединен с Rp-входами триггера каждого разряда, выход Отказ триггера первого разряда соединен с вторым входом первого элемента

5 ИЛИ, с первым входом второй группы входов первого и с первым входом первой группы входов второго элементов 2-2И-ИЛИ одноименного разряда, выход Отсутствие отказа триггера первого разряда соединен

0 с первым входом первой группы входов первого элемента 2-2И-ИЛИ первого разряда, с первым входом второго элемента ИЛИ и с первым входом элемента И/И-НЕ второго разряда, выход Отказ триггера второго

5 разряда соединен с вторым входом первого элемента ИЛИ одноименного разряда, выход Отсутствие отказа триггера второгого разряда соединен с вторым входом второго элемента ИЛИ и с вторым входом

0 элемента И/И-НЕ одноименного разряда, выход Отказ триггера третьего разряда соединен с вторым входом первого элемента ИЛИ одноименного разряда и с пер- вым входом первого элемента ИЛИ

5 счетчика, выход Отсутствие отказа триггера третьего разряда соединен с вторыми входами второго элемента ИЛИ и элемента И/И-НЕ одноименного разряда, первый вход второго элемента ИЛИ третьего разряда соединен с прямым выходом эле29

мента И/И-НЕ второго разряда, выход От- каз триггера четвертого разряда соединен с вторым входом первого элемента ИЛИ од- ноименного разряда и с вторым входом первого элемента ИЛИ счетчика, выход Отсутствие отказа триггера четвертого разряда соединен с вторыми входами второго эле.мента ИЛИ и элемента И/И-НЕ одноименного разряде, первый вход второго элемента ИЛИ четвертого разряда соединен с прямым выходом элемента И/И-НЕ третьего разряда, выход Отсутствие отказа триггера резервного разряда соединен с вторым входом второго элемента .ИЛИ л; третьего элемента И счетчика, первые вхо6098

30

ды которых соединены с прямым выходом элемента И/И-НЕ четвертого разряда, выходы вторых.элементов ИЛИ второго, третьего, четвертого разрядов и выход второго элемента ИЛИ счетчика соединены соответственно с первым-четвертым входами соответственно второго элемента И счетчика, выход которого является выходом Отсутствие отказа счетчика, выходы первых элементов 2-2И-ИЛИ первого-четвертого разрядов являются соответствующими первым- четвертым информационным выходом счетчика, выход третьего элемента И является выходом Отсутствие частичного отказа счетчика,

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Счетчик-делитель | 1989 |

|

SU1598169A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

| Двоично-десятичный счетчик | 1986 |

|

SU1370784A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1622946A1 |

| Счетчик-делитель | 1988 |

|

SU1529446A1 |

Изобретение относится к импульсной и вычислительной технике, в частности к импульсным счетчикам с фазоимпульсным представлением информации, и может быть использовано в устройствах промышленной автоматики и вычислительной техники с повышенными характеристиками экономичности и надежности функционирования. Цель изобретения - повышение достоверности функционирования и автоматизации процесса восстановления работоспособности. Двоично-десятичный

Таблица 2

Таблиц а 3Примечание. X - любое состояние логического уровня сигнала.

Таблица 4

Таблица 5

Фиг. 2

:i-с

v

a

HI

У cm а иод ка no -u К-дходам

гт

I L

JTO

хъп

Устанобка по р- ц - вхоЪип

| Интегральные микросхемы | |||

| Справочник./Лод ред | |||

| Б.В | |||

| Тарабрина | |||

| - М.: Радио и связь, 1983, С.239, Авторское свидетельство СССР № 1370784,кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-09-07—Публикация

1989-09-13—Подача