Изобретение относится к вычислительной технике.

Целью изобретения является упрощение устройства.

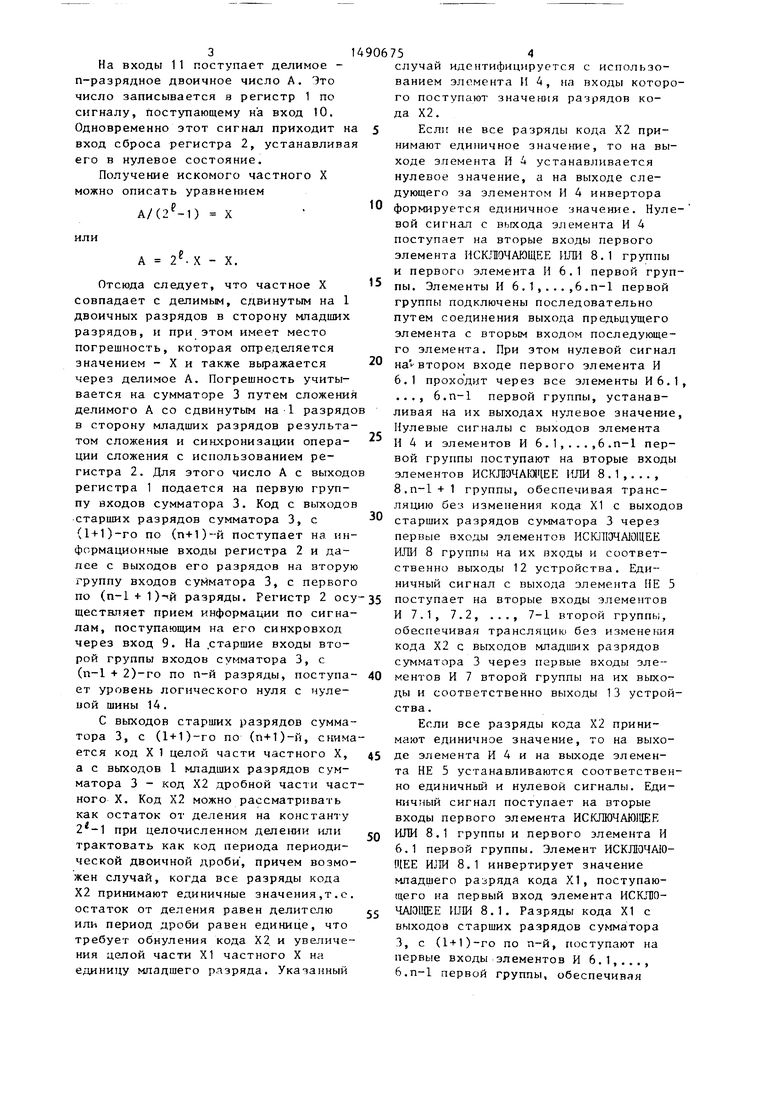

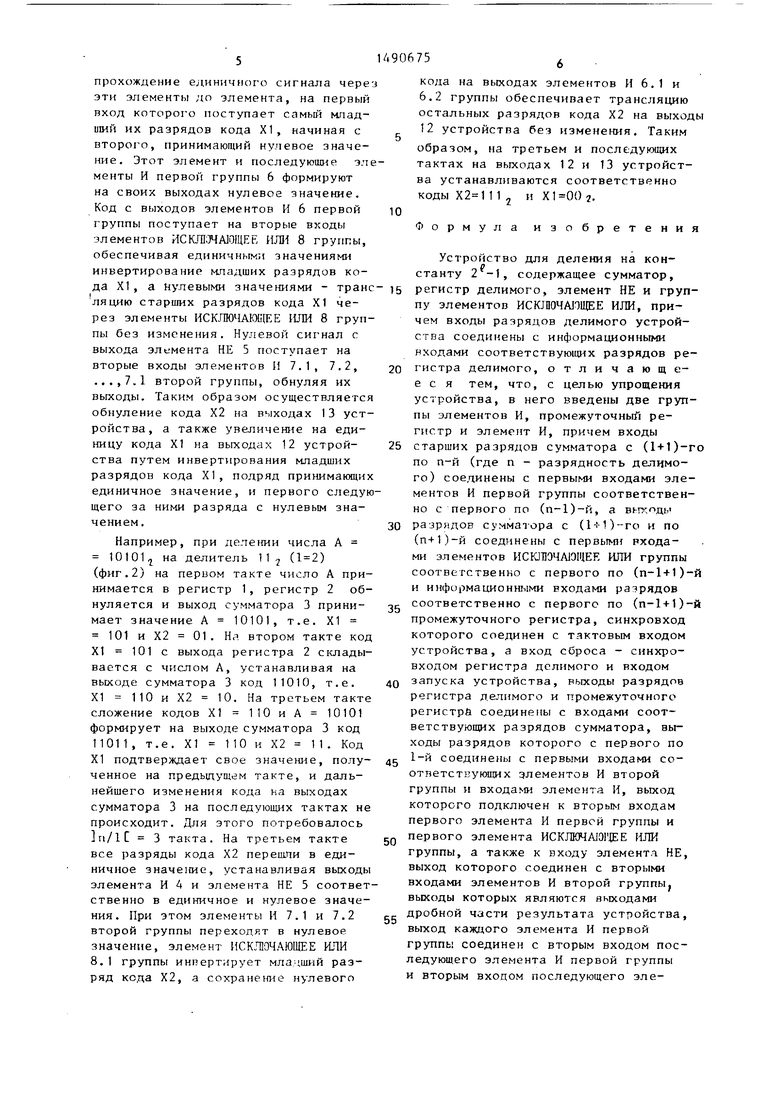

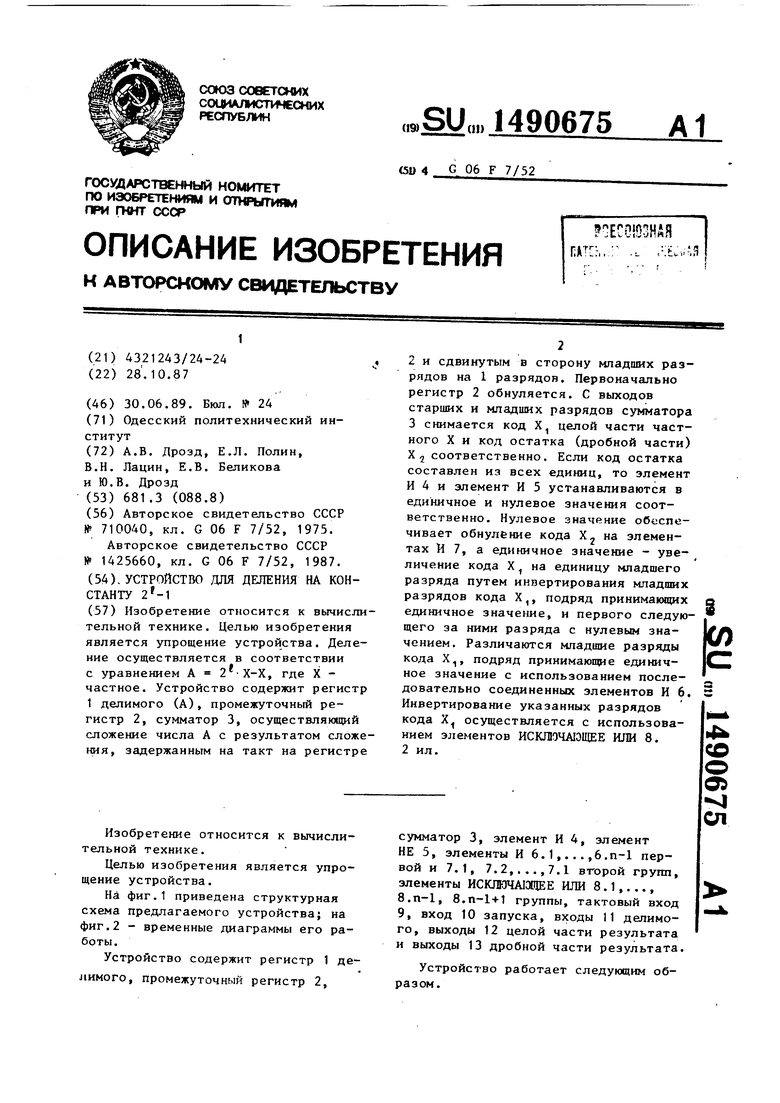

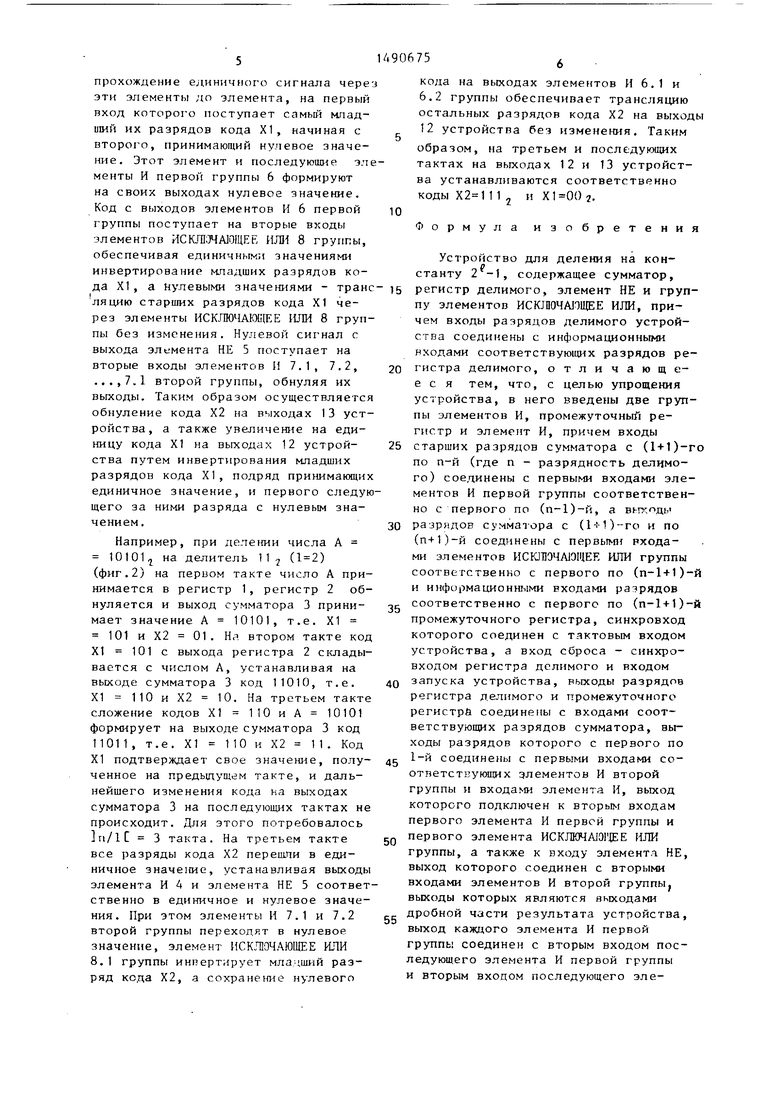

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - временные диаграммы его работы.

Устройство содержит регистр 1 делимого, промежуточный регистр 2,

сумматор 3, элемент И 4, элемент НЕ 5, элементы И 6.1,...,6.п-1 первой и 7.1, 7.2,...,7.1 вгорой групп, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 8.1,..., В.п-1, 8.П-1+1 группы, тактовый вход 9, вход 10 запуска, входы II делимого, выходы 12 целой части результата и выходы 13 дробной части результата.

Устройство работает следующим образом.

На входы 11 поступает делимое - п-разрядное двоичное число А. Это число записывается в регистр 1 по сигналу, поступающему на вход 10. Одновременно этот сигнал приходит на вход сброса регистра 2, устанавливая его в нулевое состояние.

Получение искомого частного X можно описать уравнением

А/(2-1) X

или

А 2. X - X.

Отсюда следует, что частное X совпадает с делимым, сдвинутым на 1 двоичных разрядов в сторону младших разрядов, и при этом имеет место погрешность, которая определяется значением - X и также выражается через делимое А. Погрешность учитывается на сумматоре 3 путем сложения делимого А со сдвинутым на 1 разрядо в сторону младших разрядов результатом сложения и синхронизации операции сложения с использованием регистра 2. Для этого число А с выходо регистра 1 подается на первую группу входов сумматора 3. Код с выходов старших разрядов сумматора 3, с (1+1)-го по (п+1)-й поступает на информационные входы регистра 2 и далее с выходов его разрядов на вторую группу входов сумматора 3, с первого

по (п-1+1) разряды. Регистр 2 осу-35 поступает на вторые входы элементов ществляет прием информации по сигналам, поступающим на его синхровход через вход 9. На .старшие входы второй группы входов сумматора 3, с (п-1 + 2)-го по п-й разряды, поступа- 40 ет уровень логического нуля с нулевой шины 14.

С выходов старших разрядов сумматора 3, с (1+1)-го по (п+1)-й, снимается код X 1 целой части частного X, 45 а с выходов 1 младших разрядов сумматора 3 - код Х2 дробной части частного X. Код Х2 можно рассматривать как остаток от деления на константу при целочисленном делении или трактовать как код периода периодической двоичной дроби , причем возможен случай, когда все разряды кода Х2 принимают единичные значения,т.с. остаток от деления равен делителю 55 или период дроби равен единице, что требует обнуления кода Х2 и увеличения целой части XI частного X на единицу младшего разряда. Указанный

50

И 7.1, 7.2, ..., 7-1 второй группы, обеспечивая трансляцию без изменеьмя кода Х2 с выходов младших разрядов сумматора 3 через первые входы элементов И 7 второй группы на их выходы и соответственно выходы 13 устрой ства .

Если все разряды кода Х2 принимают единичное значение, то на выходе элемента И 4 и на выходе элемента НЕ 5 устанавливаются соответствен но единичный и нулевой сигналы. Единичный сигнал поступает на вторые входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8.1 группы и первого элемента И 6.1 первой группы. Элемент ИСКЛОЧАЮЩЕЕ Ш1И 8.1 инвертирует значение нпадшего разряда кода XI, поступающего на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8.1. Разряды кода XI с выходов старших разрядов сумматора 3, с (1+1)-го по п-й, поступают на первые входы элементов И 6.1,..., 6.п-1 первой группы, обеспечивая

10

в в

15

906754

случай идентифицируется с использованием элемента И 4, на входы которого поступают значен 1Я разрядов кода Х2.

Если не все разряды кода Х2 принимают единичное значение, то на выходе элемента И 4 устанавливается нулевое значение, а на выходе следующего за элементом И 4 инвертора формируется единичное значение. Нуле- вой сигнал с выхода элемента И 4 поступает на вторые входы первого элемента ИСКЛОЧАЮЩЕЕ ПЛИ 8.1 группы и первого элемента П 6.1 первой группы. Элементы И 6 . 1 , . . . ,6 .п-1 первой группы подключены последовательно путем соединения выхода предыдущего элемента с вторым входом последующего элемента. При этом нулевой сигнал на втором входе первого элемента И 6.1 проходит через все элементы И 6.1, ..., 6.п-1 первой группы, устанавливая на их выходах нулевое значение, Нулевые сигналы с выходов элемента Н 4 и элементов И 6 . 1 ,. . . , 6 .п-1 первой группы поступают на вторые входы элементов ИСКЛЭЧАЮ1ЦЕЕ ИЛИ 8.1,..., 8.п-1 + 1 группы, обеспечивая трансляцию без изменения кода XI с выходов старших разрядов сумматора 3 через первые входы элементов ИСКШОЧАЮЩЕЕ ИЛИ 8 группы на их вхдды и соответственно выходы 12 устройства. Единичный сигнал с выхода элемента НЕ 5

20

25

30

поступает на вторые входы элементов

И 7.1, 7.2, ..., 7-1 второй группы, обеспечивая трансляцию без изменеьмя кода Х2 с выходов младших разрядов сумматора 3 через первые входы элементов И 7 второй группы на их выходы и соответственно выходы 13 устройства .

Если все разряды кода Х2 принимают единичное значение, то на выходе элемента И 4 и на выходе элемента НЕ 5 устанавливаются соответственно единичный и нулевой сигналы. Единичный сигнал поступает на вторые входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8.1 группы и первого элемента И 6.1 первой группы. Элемент ИСКЛОЧАЮЩЕЕ Ш1И 8.1 инвертирует значение нпадшего разряда кода XI, поступающего на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8.1. Разряды кода XI с выходов старших разрядов сумматора 3, с (1+1)-го по п-й, поступают на первые входы элементов И 6.1,..., 6.п-1 первой группы, обеспечивая

прохождение единичного сигнала через эти элементы до элемента, на первый вход которого поступает самый младший их разрядов кода Х1, начиная с второго, принимающий нулевое значение. Этот элемент и последующие элементы И первой группы 6 формируют на своих выходах нулевое значение. Код с выходов элементов И 6 первой группы поступает на вторые входы элементов ИСКЛЭТМЭЩЕЕ ИЛИ 8 группы, обеспечивая единичными значениями инвертирование младших разрядов ко

кода на выходах элементов И 6.1 и 6.2 группы обеспечивает трансляцию остальных разрядов кода Х2 на выходы 12 устройства без изменения. Таким образом, на третьем и последующих тактах на выходах 12 и 13 устройства устанавливаются соответственно коды 1 2 и XI 00 2.

Формула изобретения

Устройство для деления на кон„ f , станту 2 -1, содержащее сумматор,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1658149A1 |

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Устройство для деления на константу 2 @ - 1 | 1990 |

|

SU1714596A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Устройство для деления чисел | 1989 |

|

SU1711151A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1741130A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1714594A1 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

Изобретение относится к вычислительной технике. Целью изобретения является упрощение устройства. Деление осуществляется в соответствии с уравнением A=2*L.X-X, где X-частное. Устройство содержит регистр 1 делимого (A), промежуточный регистр 2, сумматор 3, осуществляющий сложение числа A с результатом сложения, задержанным на такт на регистре 2 и сдвинутым в сторону младших разрядов на L разрядов. Первоначально регистр 2 обнуляется. С выходов старших и младших разрядов сумматора 3 снимается код X1 целой части частного X и код остатка (дробной части) X2 соответственно. Если код остатка составлен из всех единиц, то элемент И 4 и элемент И 5 устанавливаются в единичное и нулевое значения соответственно. Нулевое значение обеспечивает обнуление кода X2 на элементах И 7, на единичное значение обеспечивает увеличение кода X1 на единицу младшего разряда путем инвертирования младших разрядов кода X1, подряд принимающих единичное значение, и первого следующего за ними разряда с нулевым значением. Различаются младшие разряды кода X1, подряд принимающие единичное значение с использованием последовательно соединенных элементов И 6. Инвертирование указанных разрядов кода X1 осуществляется с использованием элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8. 2 ил.

да XI, а Нулевыми значениями - транс- 15 регистр делимого, элемент НЕ и груп- ляцию старших разрядов кода XI через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 8 группы без изменения. Нулевой сигнал с выхода элемента НЕ 5 поступает на вторые входы элементов И 7.1, 7.2, 20 ...,7.1 второй группы, обнуляя их выходы. Таким образом осуществляется обнуление кода Х2 на выходах 13 устройства, а также увеличение на единицу кода XI на выходах 12 устрой- 25 ства путем инвертирования младших разрядов кода XI, подряд принимающих единичное значение, и первого следующего за ними разряда с нулевым значением.30 Например, при делении числа А

пу элементов ИСЮГОЧАЮЩЕЕ ИЛИ, причем входы разрядов делимого устройства соединены с информационными входами соответствующих разрядов регистра делимого, отличающееся тем, что, с целью упрощения устройства, в него введены две группы элементов И, промежуточный регистр и элемент И, причем входы старщих разрядов сумматора с ()-го по п-й (где п - разрядность делимого) соединены с первыми входами элементов И первой группы соответственно с первого по (п-1)-й, а вк5ход|,1 разрядов сумматора с (1-1-1)-го и по (п-f1)-й соединены с nepBbiNnf рхода- ми элементов ИСЮБЭЧА ЭЩЕЕ ИЛИ группы соответственно с первого по (п-1+1)-й и информационн 1 ми входами разрядов соответственно с первого по (п-1-ь1)-и промежуточного регистра, синхровход которого соединен с тактовым входом устройства, а вход сброса - синхро- входом регистра делимого и входом запуска устройства, выходы разрядов регистра делимого и промежуточного регистра соединены с входами соответствующих разрядов сумматора, выходы разрядов которого с первого по 1-й соединены с первыми входами соответствующих элементов И второй группы и входами элемента И, выход которого подключен к вторым входам первого элемента И первой группы и первого элемента ИСКЛЮЧА1Э1 |ЕЕ ИЛИ группы, а также к входу элемента НЕ, выход которого соединен с вторыми входами элементов И второй группы, выходы которых являются выходами дробной части результата устройства, выход каждого элемента И первой группы соединен с вторым входом последующего элемента И первой группы и вторым входом последующего эле 10101 на делитель 11 () (фиг.2) на первом такте число А принимается в регистр 1, регистр 2 обнуляется и выход сумматора 3 принимает значение А 10101, т.е. XI 101 и Х2 01. На втором такте код XI 101 с выхода регистра 2 складывается с числом А, устанавливая на выходе сумматора 3 код 11010, т.е. Х1 110 и Х2 10. На третьем такте сложение кодов XI 110 и А 10101 формирует на выходе сумматора 3 код 11011, т.е. XI 110 и Х2 11. Код XI подтверждает свое значение, полученное на предыдущем такте, и дальнейшего изменения кода на выходах сумматора 3 на последующих тактах не происходит. Для этого потребовалось Jri/lC 3 такта. На третьем такте все разряды кода Х2 перешли в единичное значение, устанавливая вькоды элемента И 4 и элемента НЕ 5 соответственно в единичное и нулевое значения. При этом элементы И 7.1 и 7.2 второй группы переходят в нулевое значение, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8.1 группы инвертирует младщий разряд кода Х2, а сохранение нулевого

5 регистр делимого, элемент НЕ и груп- 0 5 0

5

0

5

0

5

пу элементов ИСЮГОЧАЮЩЕЕ ИЛИ, причем входы разрядов делимого устройства соединены с информационными входами соответствующих разрядов регистра делимого, отличающееся тем, что, с целью упрощения устройства, в него введены две группы элементов И, промежуточный регистр и элемент И, причем входы старщих разрядов сумматора с ()-го по п-й (где п - разрядность делимого) соединены с первыми входами элементов И первой группы соответственно с первого по (п-1)-й, а вк5ход|,1 разрядов сумматора с (1-1-1)-го и по (п-f1)-й соединены с nepBbiNnf рхода- ми элементов ИСЮБЭЧА ЭЩЕЕ ИЛИ группы соответственно с первого по (п-1+1)-й и информационн 1 ми входами разрядов соответственно с первого по (п-1-ь1)-и промежуточного регистра, синхровход которого соединен с тактовым входом устройства, а вход сброса - синхро- входом регистра делимого и входом запуска устройства, выходы разрядов регистра делимого и промежуточного регистра соединены с входами соответствующих разрядов сумматора, выходы разрядов которого с первого по 1-й соединены с первыми входами соответствующих элементов И второй группы и входами элемента И, выход которого подключен к вторым входам первого элемента И первой группы и первого элемента ИСКЛЮЧА1Э1 |ЕЕ ИЛИ группы, а также к входу элемента НЕ, выход которого соединен с вторыми входами элементов И второй группы, выходы которых являются выходами дробной части результата устройства, выход каждого элемента И первой группы соединен с вторым входом последующего элемента И первой группы и вторым входом последующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами целой части результата устройства.

| Устройство для деления | 1975 |

|

SU710040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1987 |

|

SU1425660A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-06-30—Публикация

1987-10-28—Подача