рым информационным выходом устройства и подключен через первый элемент задержки к управлякндему входу второго элемента памяти, выход первого блока сравнения соединен с управляющим входом второго элемента памяти, выход которого подсоединен к втором управляющему входу блока контроля регулятора.

2. Устройство по, п. 1, отличающееся тем, что блок управления содержит генератор тактовых импульсов, первый и второй элементы ИЖ, первый и второй дополнительные счетчики импульсов и пятый ключевой элемент, один вход которого объединен со счетным входом первого дополнительного счетчика импульсов и с выходом генератора тактовых импульсов, выход первого дополнительного счетчика импульсов подключен к первому входу первого элемента ИЛИ, второй вход которого является первьш входом блока, а выход является вторь выходом блока и соединен с входами установки первого и второго дополнительных

счетчиков, выход пятого ключевого элемента является первым выходом блока и подключен к первому входу дополнительного счетчика импульсов , выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого является вторым входом блока, а выход соединен с другим входом пятого ключевого элемента.

3. Устройство по п. 1, о т л ичающееся тем, что блок контроля регулятора содержит первый дополнительный сумматор, второй элемент И и третий элемент ИЛИ, выход которого является выходом блока, первьй вход подключен к выходу второго элемента И, второй вход является вторым управляющим входом блока, входы первого дополнительного сумматора и первый вход второго элемента И являются первым и вторым инфорМационным и первым управлякяцим входами блока соответственно, выход первого дополнительного сумматора соединен с вторым входом второго элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления технологическим процессом | 1988 |

|

SU1522238A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Генератор псевдослучайных чисел | 1986 |

|

SU1324091A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТЕХНОЛОгаЧЕСКИМИ ПАРАМЕТРАМИ, содержащее счетчик, датчик технологического параметра, аналого-цифровой преобразователь, первый ключевой элемент, первый блок сравнения и регулятор, выход датчика технологического параметра соединен с информационным входом аналого-цифрового преобразователя, выход первого ключевого элемента подсоединен к входу первого блока сравнения, выход которого подключен к входу регулятора, отличающееся тем, что, с целью повышения точности устройства, в него введены блок управления, второй и третий блоки сравнения, с второго по четвертый ключевые элементы, сумматор, первьй элемент И, блок контроля регулятора, первый элемент задержки, первый и второй элементы памяти, первый вход блока управления и первый управляющий вход блока контроля регулятора являются входом запуска устройства, первый выход блока управления подключен к управляющему входу аналого-цифрового преобразователя и к синхровходу второго блока сравнения, выход которого соединен с управляющим входом второго ключевого элемента и со счетным входом счетчикаJвыход которого подсоединен к управляющему коду третьего ключевого элемента, к второму входу управления и является управляющим выходом устройства, второй выход блока управления соединен с установочным входом второго блока сравнения, с первым входом первого элемента И, с входами сброса счетчика и сумматора и является установочным выходом устройства, выход аналогоцифрового преобразователя соединен с информационньп 1и входами второго ключа и второго блока сравнения, выход второго ключа подключен к входу (Л сумматора, выход которого соединен с информационьдым входом третьего ключа, выход которого подклк)чен к входу третьего блока сравнения, к информационным входам четвертого клю:чевого элемента и первого элемента памяти, выход третьего блока сравнесо ния является первым информационным 05 выходом устройства, соединен с со управляющим входом четвертого ключевого элемента и с вторым входом первого элемента И, выход которого подключен к управляющему входу первого элемента памяти, выход которого и выход четвертого ключевого элемента подключены к первому информационному входу блока контроля регулятора и к второму информационному входу блока контроля регулятора, объединенному с информационным входом четвертого ключевого элемента, вькод блока контроля регулятора подсоединен к управляющему входу первого ключевого элемента, является вто

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления технологическими процессами.

Цель изобретения - повышение точности устройства.

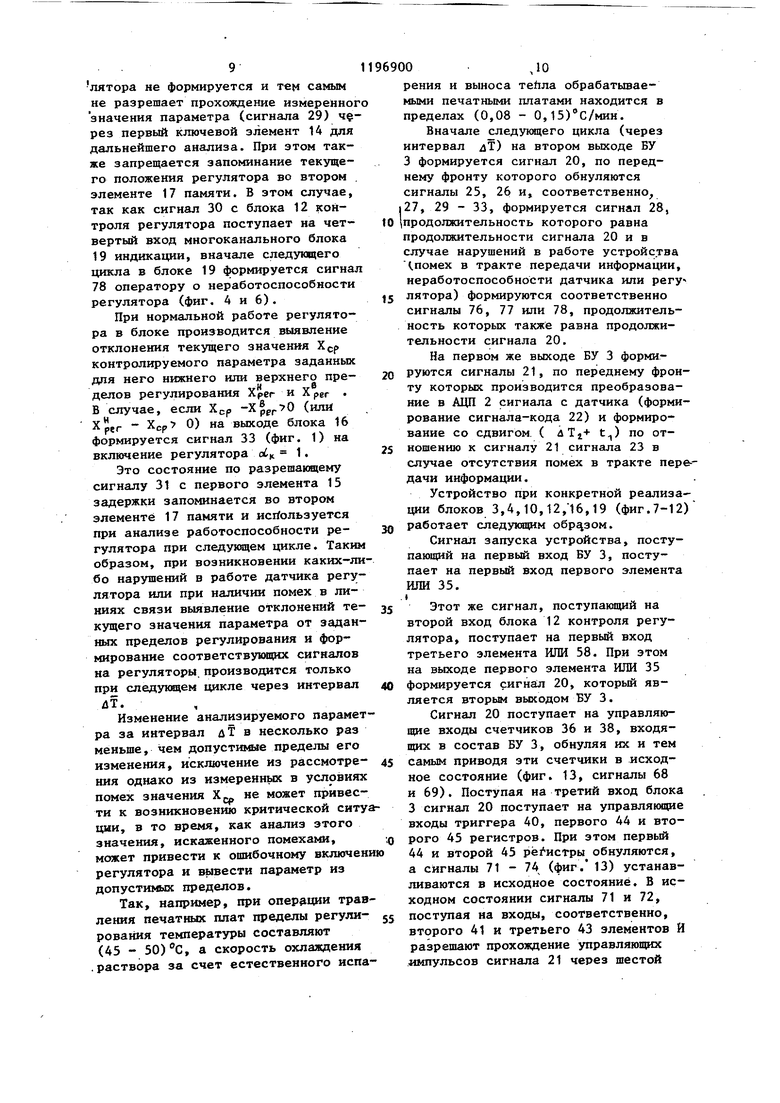

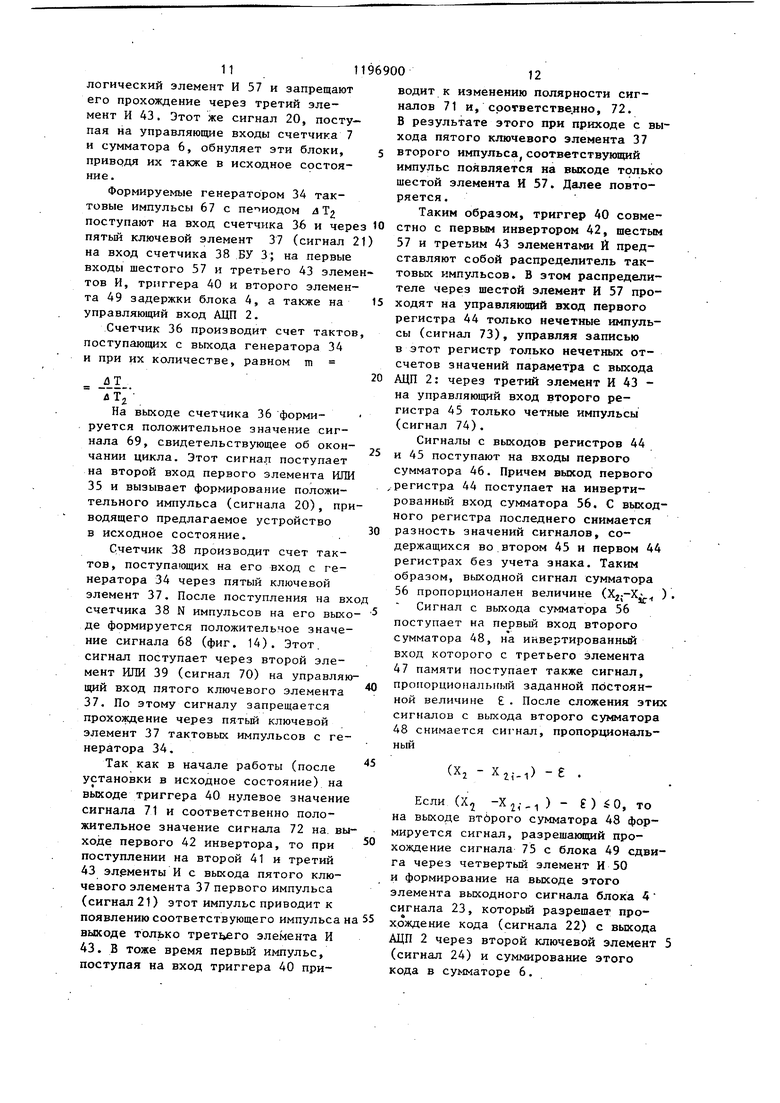

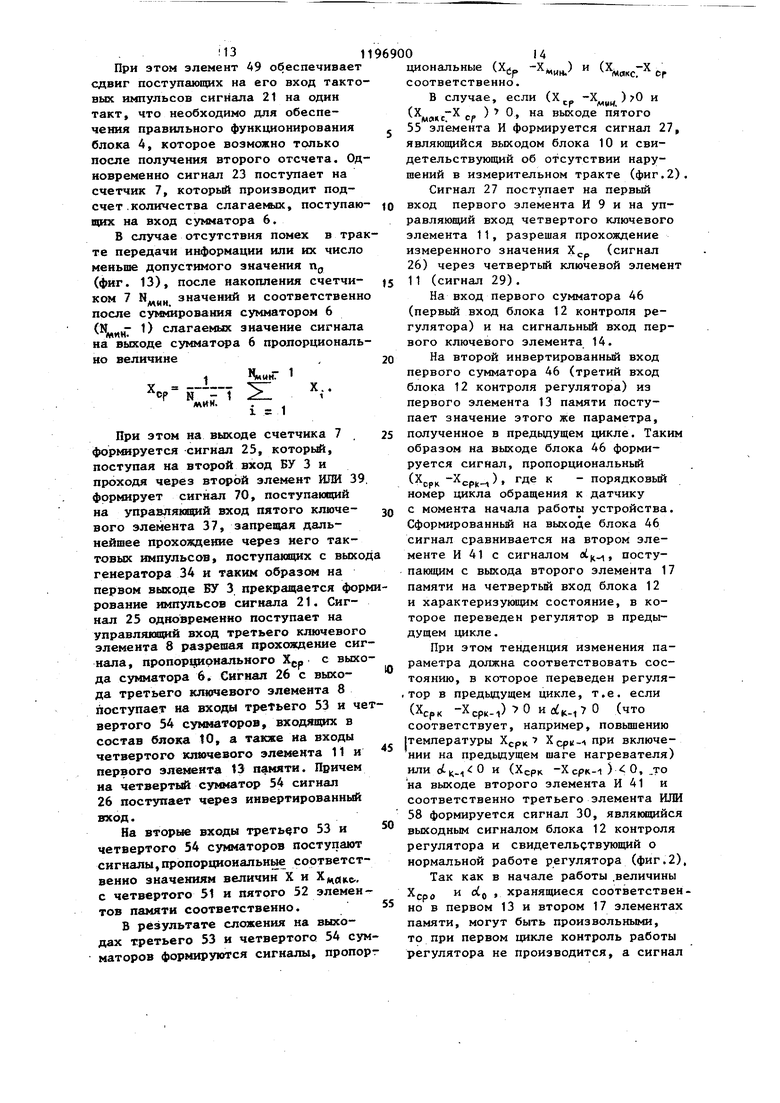

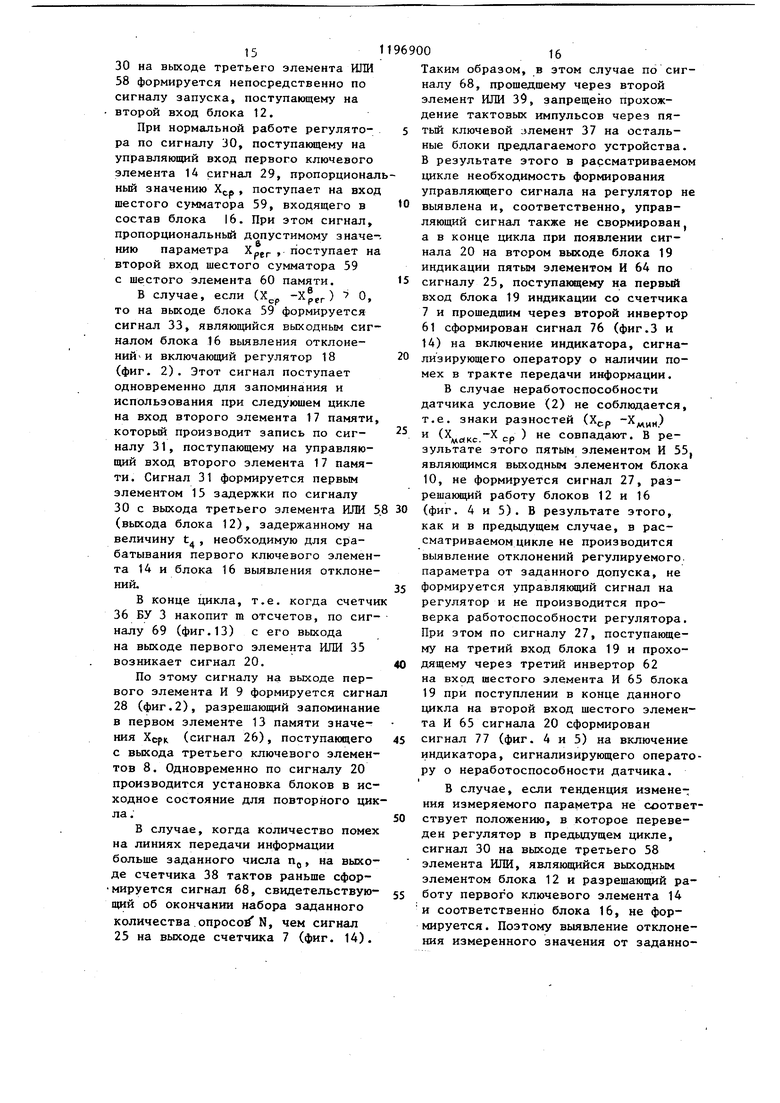

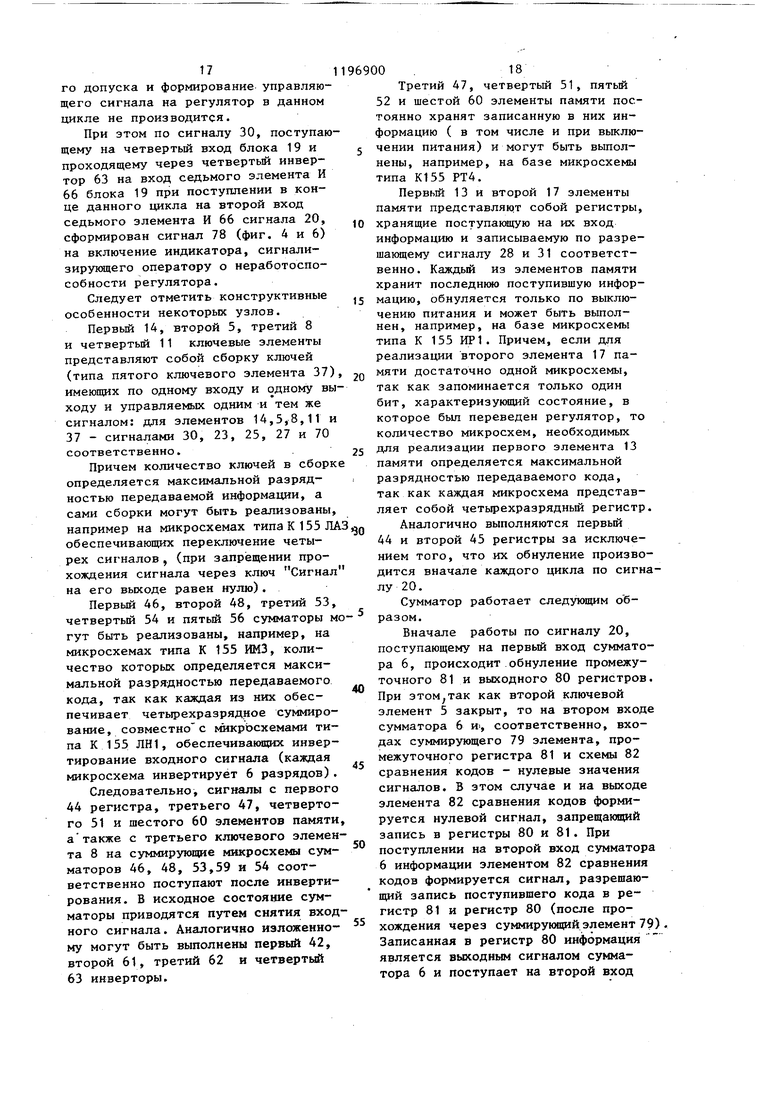

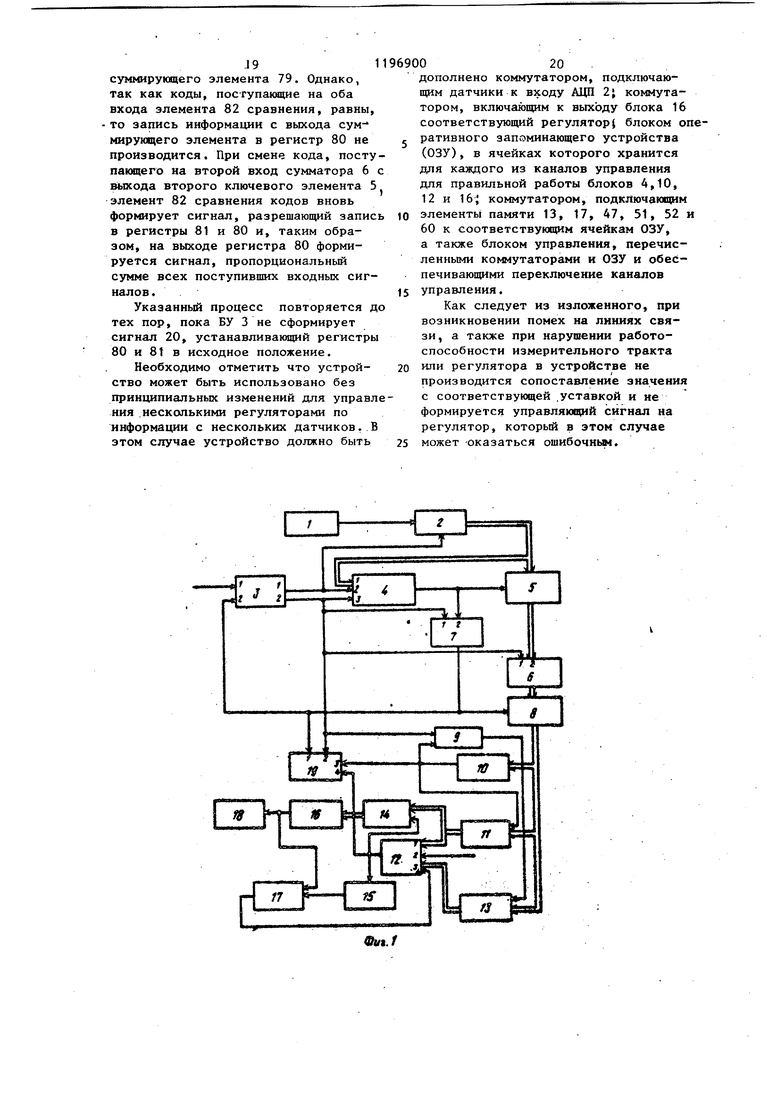

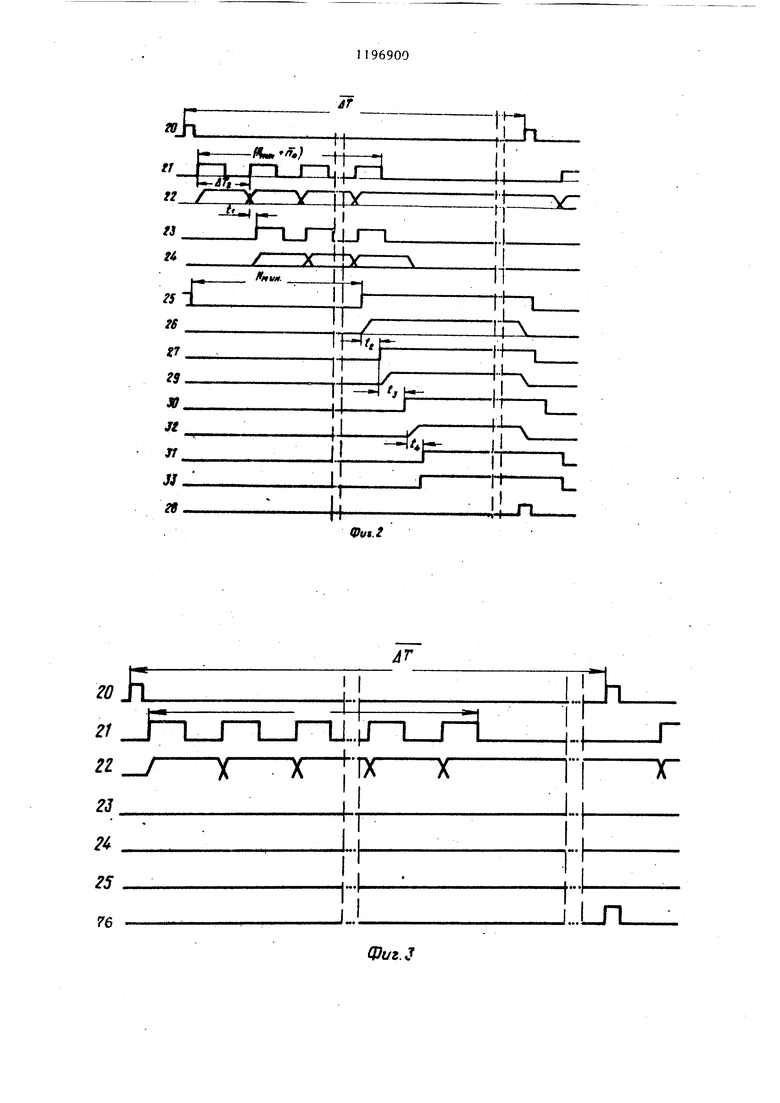

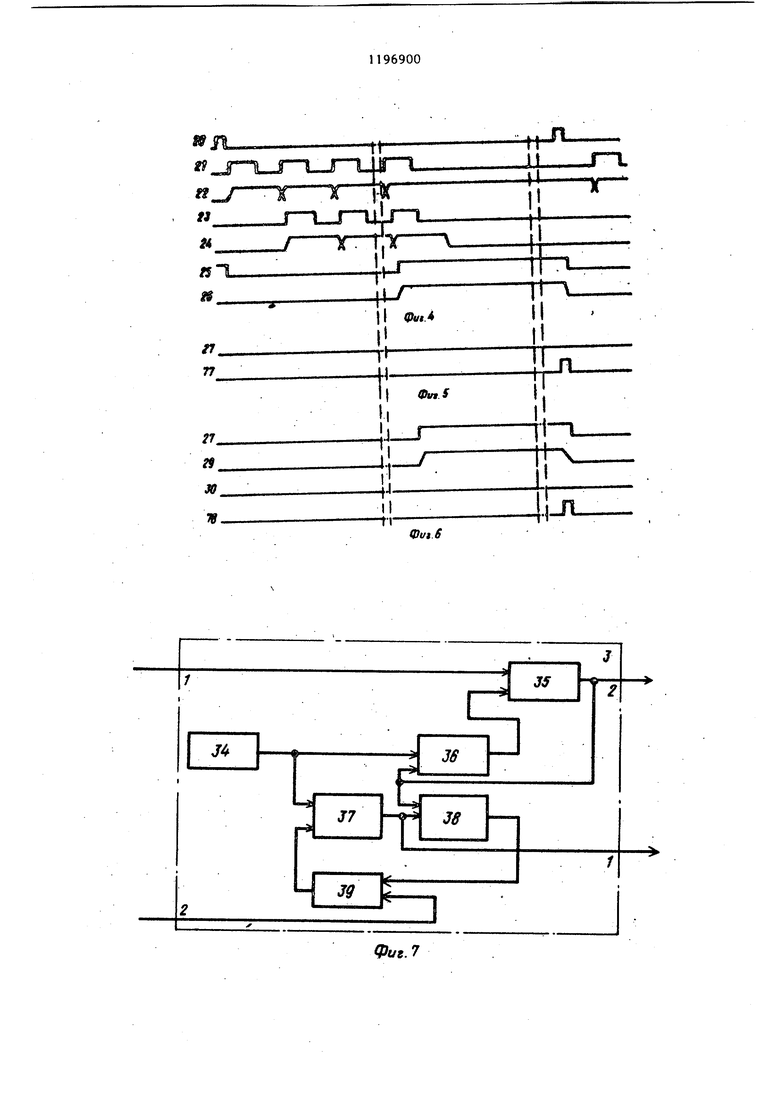

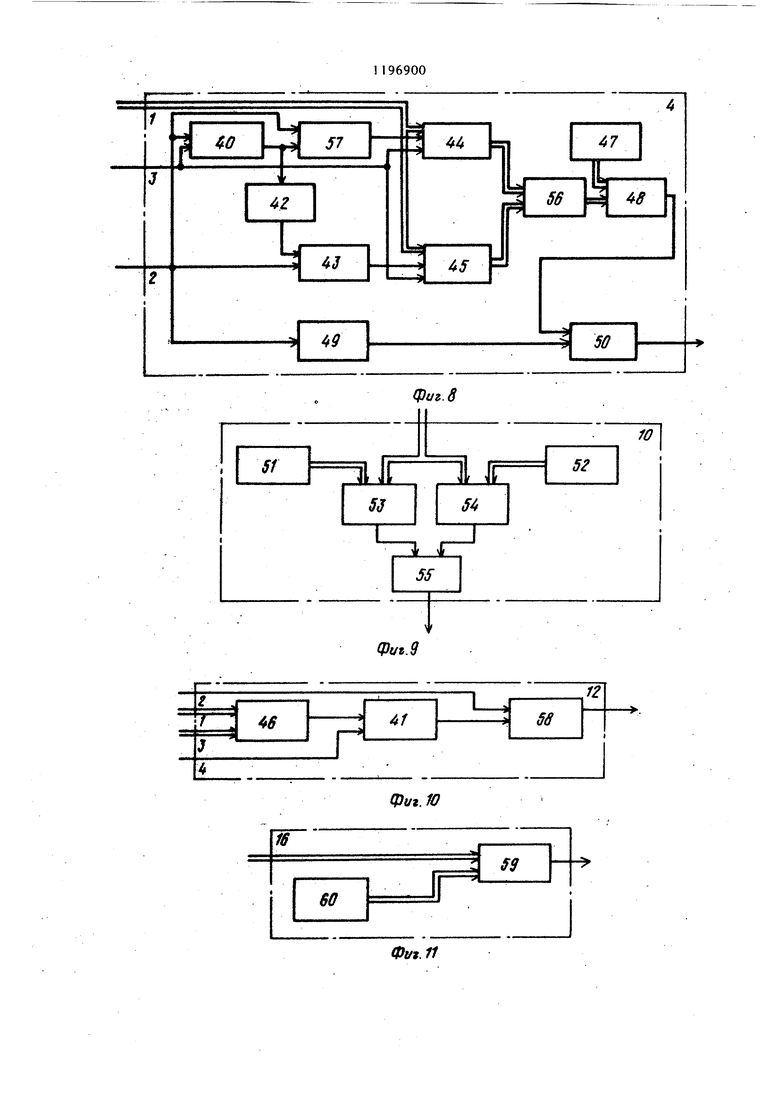

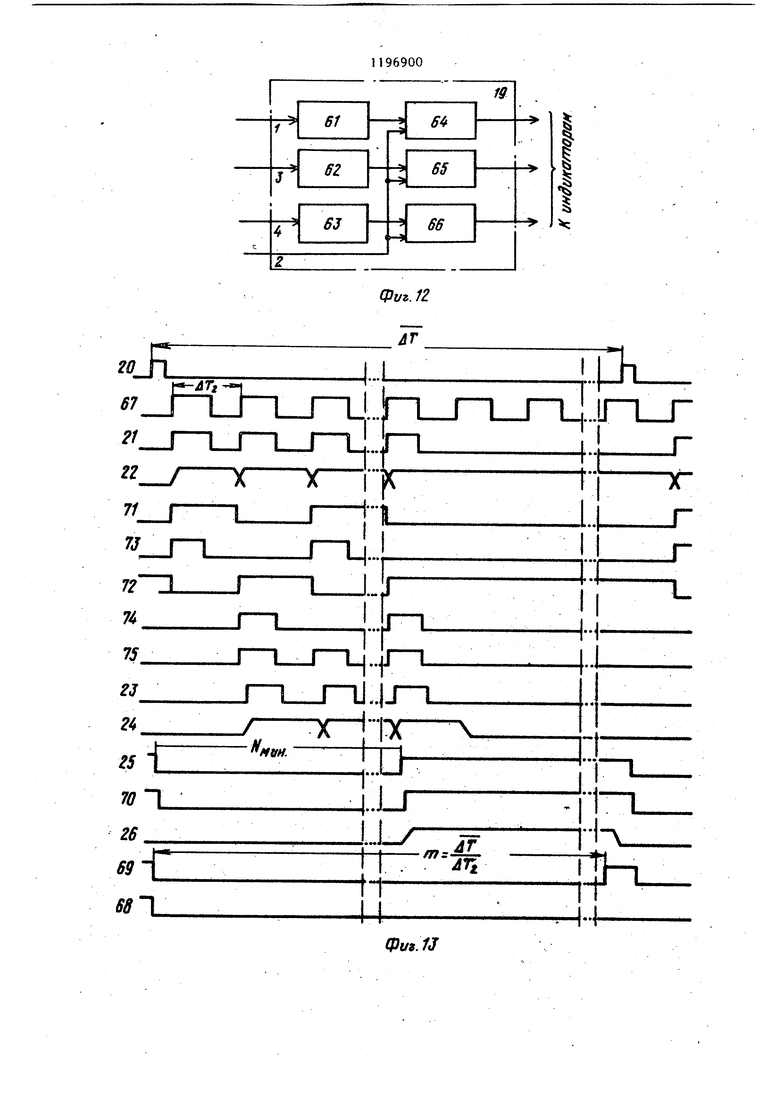

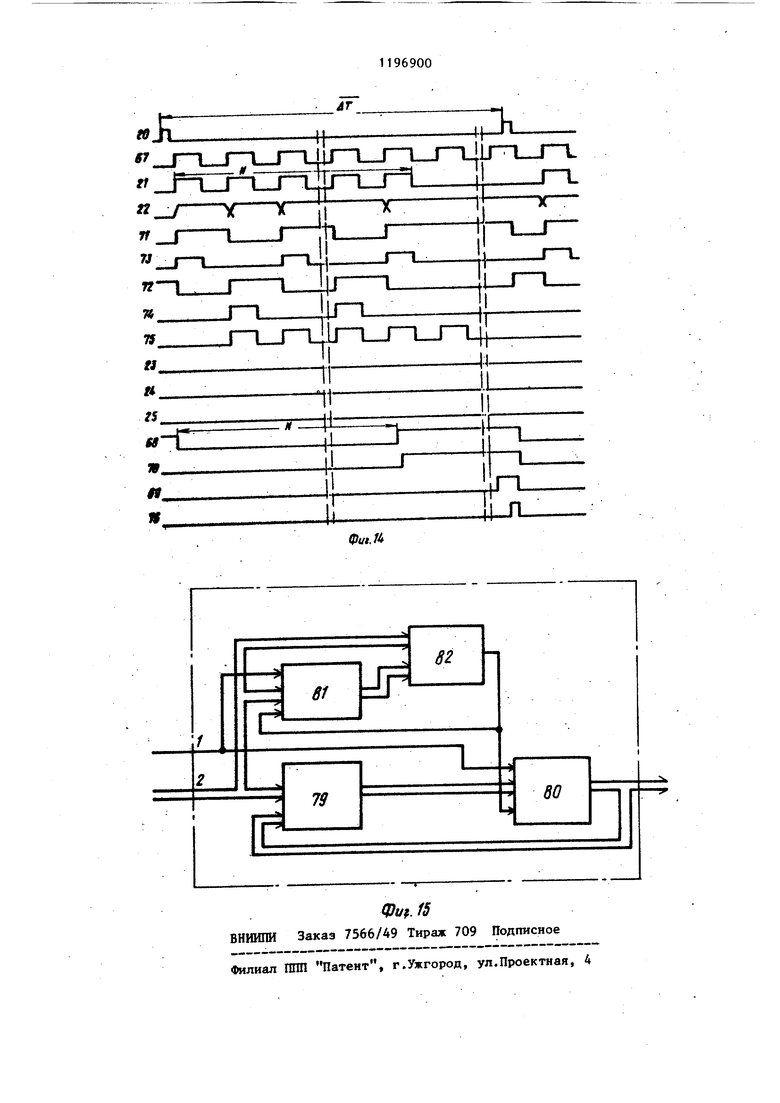

На фиг. 1 изображена схема устройства-, на фиг. 2 - 6 - временные диаграммы; на фиг. 7 -.12 - схемы блока управления, первого и второго блоков сравнения, блока контроля регулятора, третьего блока сравнения многоканального блока индикации соответственно на фиг. 13 и 14 - вре- менные диаграммы на фиг. 15 - схема сумматора.

Устройство содержит датчик технологического параметра (ДТП) 1, аналого-циф|ровой преобразователь (АЦП) 2, блок (БУ) 3 управления, второй блок 4 сравнения, второй ключевой элемент 5, сумматор 6, счетчик 7,

третий ключевой элемент 8, первый элемент И 9, третий блок 10 сравнения, четвертый ключевой элемент 11, блок 12 контроля регулятора, первый элемент 13 памяти, первый ключевой элемент 14, первый элемент 15 задержки, первый блок 16 сравнения, второй элемент 17.памяти, регулятор 18, многоканальньй блок 19 индикации, сигналы 20 - 33 на входах блоков 3,2,4,5,7,8,10,9,11,12,15,14,16, генератор 34 тактовых импульсов, первый элемент ИЖ 35, первый дополнительный счетчик 36 импульсов, пятьй ключевой элемент 37, второй дополнительный счетчик 38 импульсов, второй элемент ИЛИ 39, триггер 40, второй элемент И 41, первый инвертор 42, третий элемент И 43, первьй 44 и второй 45 регистры, первый дополнительный сумматор 46, третий элемент 47 памяти, второй дополнктельный сумматор 48, второй элемент 49 задержки, четвертый элемент И 50, четвертый 51 и пятый 52 элементы памяти, третий 53 и четвертьй 54. дополнительные сумматоры, пятый элемент И 55, пятый дополнительHbBi сумматор 56, шестой элемент И 57 третий элемент ИЛИ 58, шестой дополнительньш сумматор 59, шестой элемент 60 памяти, с второго по четвертый инверторы 61 - 63, с пятого по седьмой элементы И 64 - 66, сигналы 67 - 78 - на выходах блоков элементов 34,38,36,39,40,42,43,49,6 65,66, суммирующий элемент 79, выходной и промежуточный регистры 80 и 81, элемент 82 сравнения кодов. Устройство работает следующим образом. Импульсный сигнал запуска устрой ства поступает на первый вход БУ 3 и второй вход блока 12. При этом блок 3 устанавливается в исходное состояние, а на его втором входе формируется сигнал 20, устанавливаю щий блоки 4, сумматор 6 и счетчик 7 в исходное состояние. Одновременно на первом выходе БУ 3 с интервалом STj формируются импульсы сигнала 2 (фиг. 2), управляющие работой устройства. Мсшая скорость изменения технологических параметров измеряется (например, для химико-гальванических процессов производства печатных плат) минутами и, как правило, импульсный характер помех, возникающих на линиях передачи информации, свидетельствует, что частоты изменения полезного сигнала и помехи разнесены фактически более, чем на порядок. Поэтому для выявления поме поступающих на вход АЦП 2 с датчика 1, сигнал, пропорциональный измеряе мому значению параметра X, через интервал Т опрашивается несколько раз с периодом 4Т2. При этом интервал 4 Т выбирается учетом скорости изменения контролируемого параметра и составляет мин, а ДТ2 - исходя из необходимости статистически достоверной информации, т.е. N 25-30 отсчетов, за время, когда изменение контролируемого параметра соизмеримо с точностью измерения. При практической реализации величина ATj приним ется равной ,2с. Формируемые на первом выходе БУ с интервалом 4 Т управляющие импул 00 сы сигнала 21 поступают на управляющий вход АЦП 2 -и на второй вход блока 4 сравнения смежных отсчетов, син хронизируя их работу. В конце интервала дТ на втором выходе БУ 3 формируется сигнал 20, устанавливающий блоки 3 и 4, сумматор 6, счетчик 7 в исходное состояние и подготавливая их для обработки следующих выборок. Получаемые на выходе АЦД 2 i-e значения Х (сигнал 22) поступают на сигнальный вход второго ключевого элемента 5-и на первьгй вход блока 4. В последнем смежные значения параметра сравниваются между собой, т.е. формируется величина пропорциональная (.1 -Х), i 1,2,...,п, которая сравнивается с заданной постоянной для данного параметра значением , выбираеьым исходя из точности преобразования параметра. Величина принимается эквивалентной двум единицам (шадшего разряда АЦП. 2, В случае, если с задержкой t относительно сигнала 21 (фиг. 2) и определяемой временем работы блока 4 на выходе последнего формируется сигнал 23, поступаю1ций на управляющий вход второго ключевого элемента 5 и разрешающий прохождение измеренного i-ro значения (сигнала 22) параметра с выхода АЦП 2 на вход сумматора 6 (сигнал 24). При этом сигнал 23 (фиг. 2) сдвинут относительно сигнала 21 на интервал дТ , что необходимо для возможности проверки условия (t), которое может быть проведено не ранее, чем . после снятия с выхода АЦП 2 второго отсчета. При этом, выбрав из каждой выборки, содержащей N значений, минимальное количество слагаемых (N ), которое должно быть учтено при определении значения сигнала на выходе датчика 1, сигнал на выходе сумматора 6 после накопления выбранного количества слагаемых пропорционален величине X - -1. ср N мчи. Задаваясь величиной п, допустимого количества опросов сигнала с датчика, при которых не выполняется приведенное условие (1), т.е. существуют помехи на линиях передачи информации, суммарное количество опросов при обращении к датчику в течение одного цикла составляет

N Н„„„-ь п,.

С цепью получения достоверных результатов величина п (0,1-0,15)

В том случае, если помех на линиях передачи информации при опросе датчика не наблюдается или их число не превышает п, то после накопления в сумматоре 6 . значений X. и, соответственно, N импульсов в счет чике 7 на выходе последнего формируется сигнал 25, поступакщий на управлякмций вход третьего ключевого элемента и разрешающий прохождение сигнала пропорционального с выхода сумматора 6 через третий ключевой элемент 8 (сигнал 26) на входы блока 10 четвертого ключевого элемента 11 и первого элемента 13 памяти.

Одновременно сигнал 25 с выхода счетчика 7 поступает на второй вход БУ 3. При этом с первого выхода БУ 3 прекращается формирование управляющих импульсов сигнала к рассматривае мой выборке, т.е.

N-, N - п,,

где - количество опросов, при которых не выполняется условие (1) среди значений X., удовлетворяю1да1х условию (1) .

Причем Пд Пд.

Сигнал 25 с выхода счетчика 7 поступает также на первый вход многоканального блока 19 индикации и используется в момент окончания цикла (при формировании импульсного сигнала 20) для формирования сигнала оператору в случае, если в тракте передачи информации помех больще допустимого значения п.

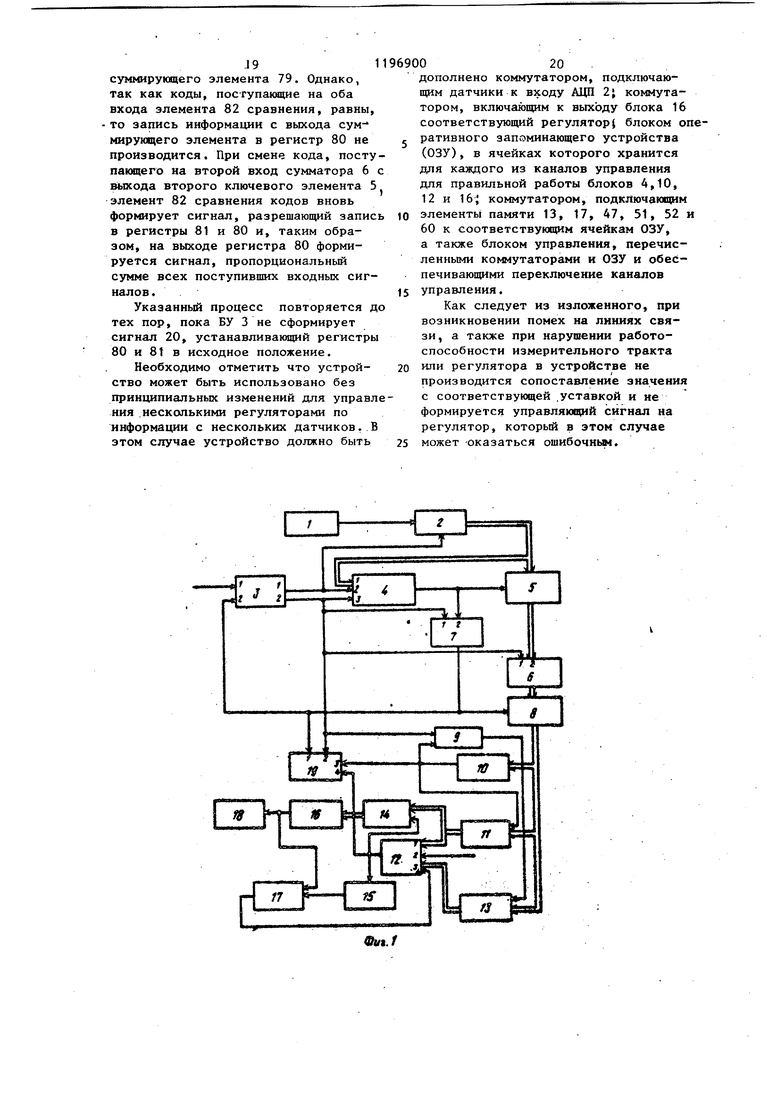

.В том случае, если количество помех в тракте передачи информации больше допустимого значения п, то формирование сигнала 21 с первого выхода ВУ 3,обеспечивакадего формирование выборки из N отсчетов (фиг. 3), на выходе АЦП 2 (сигнала 22) заканчивается раньше, чем на вь ходе счетчика 7 формируется сигнал 25 на управляющий вход третьего ключевого элемента 8, свидетельствующий об окончании накопления в сумматоре 6 слагаемых.

В этом случае накопленное в сумматоре 6 значение не поступает на последующую обработку и обнуляется в начгше следующего цикла по сигналу 20 с второго выхода БУ 3, устанавливающего устройство в исходное состояние.

Одновременно с формированием сигнала 20 и в связи с отсутствием сигнала на выходе счетчика 7, поступающего на первый вход блок 19, в последнем формируется сигнал 76 (фиг. 3) оператору о наличии помех в тракте передачи информации.

При разрешающем сигнале 25 со счетчика 7 на прохождение сигнала с выхода сумматора 6 через третий ключевой элемент 8 (формирование сигнала 26) в блоке 10 производится проверка работоспособности датчка путем сопоставления измеренного значения (сигнала 26) с выхода датчика и сформированного на выходе сумматора 6 с возможными пределами изменения этого параметра

мвис. мин. Р нормальной работ датчика. Значения Х явлются постоянными дпя данного датчика. Эти пределы выбираются с учетом физической природы конкретных измеряемых параметров. Так, например, для датчиков температуры наиблее характерные неисправности проявляются в обрыве цепи либо в коротком замыкании, что приводит к сигналам, соответствующим чрез,мерно высоким, либо низким показа|ниям датчика. Так, например, при рассмотрении химико-гальванических процессов производства печатных плат для датчиков температуры эти значения принимаются равными Х.... (5 - 10)С, Х (100-150) с;

Таким образом, в случае, если

ХСР-З НК) 0

(2) .., ) 0.

с задержкой t относительно поступившего на вход блока 10 сигнала 26 и определяемой временем работ блока 10, на его выходе формируется сигнал, свидетельствукщий о работоспособности датчика, который поступает на управляющий вход четвертого ключевого элемента 11 и тем самым измеренное значение параметра (сигнал 29) поступает на первый ключевой элемент 14 и первый вход блока 12, Сигнал 27 с выходе: блока 10 одновременно поступает на первый элемент И 9 и третий вход блок ч 19. В начале следующего цикла по сигналу 20 с второго выхода БУ 3 на выходе первого элемента И 9 формируется сигнал 28 на первый элемент 13 памяти, переводя его в режим записи. При этом в первом элементе 13 памяти за поминается измеренное в данном цикле значение Xj.p вместо хранимого ра нее значения Хр-.. , полученного в предыдущем цикле. В случае, если одно из условий (2) не выполняется, что свидетельствует о неработоспособности датчика, сигнал 27 формируется и тем сам не разрешается прохождение измеренного значения параметра (сигнал 26) через четвертый ключевой элемент 11 для дальнейшего анализа. При этом также запрещается запоминание измеренного значения параметра в первом элементе 13 памяти. В этом случае, так как сигнал 27 с блока 10 поступает на третий вход блока 19, в начале следующего цикла в последнем формируется сигнал 77 оператору о неработоспособности датчика (фиг. 4 и 5). При нормальной работе датчика в блоке 12 производится анализ работо способности регулятора. С готой цель в нем производится сопоставление измеренного значения параметров Хср (сигнала 29) с значением этого же параметра, полученного в предыдущем цикле, запомненного в первом элемен те 13 памяти и поступающего на тpeти вход блока 12, т.е. формируется сигнал пропорциональный разности )с-1 порядковый номер цикла с момента начала работы устройства. Сигнал, характеризующий знак разности (Хрр,, -XCPK-I) в свою очередь, сравнивается с сигналом . , поступающим с второго элемента 17 памяти на четвертый вход блока 12 и характеризующего состояние, в которое переведен регулятора предьщущем цикле Тенденция изменения параметра должна соответствовать состоянию. в которое переведен регулятор в предыдущем цикле. Таким образом, если ( -Хгрк-1 ) О и. О (что соответствует, например, повышению температуры Х. 7 срк- Р включении в предьщущем цикле нагрев.ателя) или ot. 0 и ( -Хсрк.,,) О, то это свидетельствует о нормальной работе регулятора. При этом на выходе блока 12 контроля регулятора с задержкой tj относительно поступающего на его вход сигнала 29 и определяемой временем работы блока 10, формируется сигнал 30 на управляющий вход первого ключевого элемента 14. Этот сигнал разрешает прохождение измеренного значения Xj.. (сигнала 32) на вход блока 16 для определения наличия отклонения регулируемого параметра от заданных технологических допусков и формирования соответствующего сигнала 33 на регулятор 18. При этом с задержкой t, необходимой для срабатывания первого ключевого элемента 14 и обработки информации в блоке 16, первым элементом 15 задержки по сигналу 30 с блока 12 контроля регулятора формируется сигнал 31, разрешающий произвести запись во второй элемент 17 памяти сигнала 33, характеризукицего состояние в которое переводится регулятор 18, т.е. производится запись величины вместо Ввиду того, что включение регулятора может способствовать уменьшению значения измеряемого параметра (например, при включении установки охлаждения), то в зависимости от тенденции изменения конкретного параметра при включении регулятора для каждого отдельного параметра заранее устанавливается знак of|.i , соответствующий включенному состоянию регулятоТак как при первом цикле (вначале работы) величины X сро и , хранящиеся в первом 13 и втором 17 элементах памяти, соответственно, могут быть произвольными, проверка работоспособности регулятора в первом цикле производится. С этой целью сигнал запуска устройства поступает Hfi второй вход блока 12 контроля регулятора. В случае выявления нарушений в ра ботоспособности регулятора сигнал 30 на выходе блока 12 контроля регулятора не формируется и тем самым не разрешает прохождение измеренног значения параметра (сигнала 29) первый ключевой элемент 14 для дальнейшего анализа. При этом также запрещается запоминание текущего положения регулятора во втором элементе 17 памяти. В этом случае, так как сигнал 30 с блока 12 контроля регулятора поступает на четвертый вход многоканального блока 19 индикации, вначале следукщего цикла в блоке 19 формируется сигнал 78 оператору о неработоспособности регулятора (фиг. 4 и 6). При нормальной работе регулятора в блоке производится выявление отклонения текущего значения контролируемого параметра заданных для него нижнего или верхнего пределов регулирования Хрсг и X per В случае, если Хср Хррг О (или 0) на выходе блока 16 - Хср формируется сигнал 33 (фиг. 1) на включение регулятора о 1. Это состояние по разрешающему сигналу 31 с первого элемента 15 задержки запоминается во втором элементе 17 памяти и исйользуется при анализе работоспособности регулятора при следукяцем цикле. Таким образом, при возникновении каких-ли бо нарушений в работе датчика регулятора или при наличии помех в линиях связи выявление отклонений текущего значения параметра от заданных пределов регулирования и формирование соответствухщих сигналов на регуляторы, производится только при следукидем цикле через интервал ДТ. Изменение анализируемого парамет ра за интервал дТ в несколько раз меньше, чем допустюоде пределы его изменения, исключение из рассмотрения однако из измеренных в условиях помех значения У. не может привести к возникновению критической ситу ции, в то время, как анализ этого значения, искаженного помехами, может привести к ошибочному включен регулятора и вывести параметр из допустимых пределов. Так, например, при операции трав ления печатных плат пределы регулирования температуры составляют (45 - 50)с, а скорость охлаждения . раствора за счет естественного испа 00 рения и выноса тейла обрабатываемыми печатными платами находится в пределах (0,08 - 0,15)С/мин. Вначале следующего цикла (через интервал /iT) на втором выходе БУ 3 формируется сигнал 20, по переднему фронту которого обнуляются сигналы 25, 26 и, соответственно, |27, 29 - 33, формируется сигнал 28, (Продолжительность которого равна продолжительности сигнала 20 и в случае нарушений в работе устройства Чпомех в тракте передачи информации, неработоспособности датчика или регу лятора) формируются соответственно сигналы 76, 77 или 78, продолжительность которых также равна продолжительности сигнала 20. На первом же выходе БУ 3 формируются сигналы 21, по переднему фронту которых производится преобразование в АЦП 2 сигнала с датчика (формирование сигнала-кода 22) и формирование со сдвигом ( dTi+ t) по отношению к сигналу 21 сигнала 23 в случае отсутствия помех в тракте пере-дачи информации. Устройство при конкретной реализащси блоков 3,4,10,12,16,19 (фиг.7-12) работает следуклчим образом. Сигнал запуска устройства, поступающий на первый вход БУ 3, поступает на первый вход первого элемента ИЛИ 35. I Этот же сигнал, поступающий на второй вход блока 12 контроля регулятора, поступает на первый вход третьего элемента ИЛИ 58. При этом на выходе первого элемента ИЛИ 35 формируется сигнал 20, который является вторьш выходом БУ 3. Сигнал 20 поступает на управляющие входы счетчиков 36 и 38, входящих в состав БУ 3, обнуляя их и тем самым приводя эти счетчики в исходное состояние (фиг. 13, сигналы 68 и 69). Поступая на третий вход блока 3 сигнал 20 поступает на управляюпр1е входы триггера 40, первого 44 и второго 45 регистров. При этом первый 44 и второй 45 рёг истры обнуляются, а сигналы 71 - 74 (фиг/ 13) устанавливаются в исходное состояние. В исходном состоянии сигналы 71 и 72, поступая на входы, соответственно, второго 41 и третьего 43 элементов И разрешают прохождение управляющих импульсов сигнала 21 через шестой 11 логический элемент И 57 и запрещают его прохождение через третий элемент И 43. Этот же сигнал 20, посту пая на управляющие входы счетчика 7 и сумматора 6, обнуляет эти блоки, приводя их также в исходное состояние. Формируемые генератором 34 тактовые импульсы 67 с пе иодом аТ поступают на вход счетчика 36 и чер пятый ключевой элемент 37 (сигнал на вход счетчика 38 БУ 3; на первые входы шестого 57 и третьего 43 элем тов И, триггера 40 и второго элемен та 49 задержки блока 4, а также на управляющий вход АЦП 2. Счетчик 36 производит счет такто поступающих с выхода генератора 34 и при их количестве, равном m лтГ На выходе счетчика 36 формируется положительное значение сигнала 69, свидетельствующее об окон чании цикла. Этот сигнал поступает на второй вход первого элемента ИЛ 35 и вызывает формирование положительного импульса (сигнала 20), пр водящего предлагаемое устройство в исходное состояние. Счетчик 38 производит счет тактов, поступающих на его вход с генератора 34 через пятый ключевой элемент 37. После поступления на в счетчика 38 N импульсов на его вых де формируется положительное значе ние сигнала 68 (фиг. 14). Этот, сигнал поступает через второй элемент ИЛИ 39 (сигнал 70) на управля щий вход пятого ключевого элемента 37. По этому сигналу запрещается прохождение через пятый ключевой элемент 37 тактовых импульсов с ге нератора 34. Так как в начале работы (после установки в исходное состояние) на выходе триггера 40 нулевое значени сигнала 71 и соответственно положительное значение сигнала 72 на. в ходе первого 42 инвертора, то при поступлении на второй 41 и третий 43 элементы И с выхода пятого ключевого элемента 37 первого импульса (сигнал 21) этот импульс приводит к появлению соответствующего импульса выходе только третьего элемента И 43. В тоже время первый импульс, поступая на вход триггера 40 при0водит к изменению полярности сигналов 71 и, срответстве.нно, 72. В результате этого при приходе с выхода пятого ключевого элемента 37 второго импульса соответствующий импульс появляется на выходе только щестой элемента И 57. Далее повторяется. Таким образом, триггер 40 совместно с первым инвертором 42, шестым 57 и третьим 43 элементами И представляют собой распределитель тактовых импульсов, В этом распределителе через шестой элемент И 57 проходят на управляющий вход первого регистра 44 только нечетные импульсы (сигнал 73), управляя записью в этот регистр только нечетных отсчетов значений параметра с выхода АЦП 2: через третий элемент И 43 на управляющий вход второго регистра 45 только четные импульсы (сигнал 74). Сигналы с выходов регистров 44 и 45 поступают на входы первого сумматора 46. Причем выход первого регистра 44 поступает на инвертироваиньй вход сумматора 56. С выходного регистра последнего снимается разность значений сигналов, содержащихся во.втором 45 и первом 44 регистрах без учета знака. Таким образом, выходной сигнал сумматора 56 пропорционален величине (X2;-X,j Сигнал с выхода сумматора 56 поступает на первый вход второго сумматора 48, на инвертированный вход которого с третьего элемента 47памяти поступает также сигнал, пропорциональный заданной постоянной величине . После сложения этих сигналов с выхода второго сумматора 48снимается сигнал, пропорциональныйл. - ) Е Если (Х -X2,--i) - f)0, то на выходе второго сумматора 48 формируется сигнал, разрешакйций прохождение сигнала 75 с блока 49 сдвига через четвертый элемент И 50 и формирование на выходе этого элемента выходного сигнала блока 4 сигнала 23, который разрешает прохождение кода (сигнала 22) с выхода АЦП 2 через второй ключевой элемент 5 (сигнал 24) и суммирование этого кода в сумматоре 6. при этом элемент 49 обеспечивает сдвиг поступающих на его вход такто вых импульсов сигнала 21 на один такт, что необходимо для обеспечения правильного функционирования блока 4, которое возможно только после получения второго отсчета. Од новременно сигнал 23 поступает иа счетчик 7, которьА производит подсчет .количества слагаемых, поступаю щих на вход сумматора 6. В случае отсутствия помех в тра те передачи информации или их число меньше допустимого значения п (фиг. 13), после накопления счетчиком 7 Ы„„„ значений и соответственн после суммирования сумматором 6 (N. и 1) слагаемых значение сигнала на выходе сумматсфа 6 пропорциональ но величине Н«инГ 1 .и-. При этом на выходе счетчика 7 формируется сигнал 25, который, поступая на второй вход БУ 3 и проходя через второй элемент ИШ 39 формирует сигнал 70, поступающий на управлямщий вход пятого ключевого элемента 37, запрещая дальнейшее прохождение через него тактовых импульсов, поступающих с выхо генератора 34 и таким образсда на первом выходе ВУ 3 прекр |щается фор рование импульсов сигнала 21. Сигнал 25 одновременно поступает на управлякшснй вход третьего ключевого элемента 8 разрешая прохождение сиг нала, пропор р1рнального Х.. . с выхо да сумматора б. Сигнал 26 с выхода третьего кгвочевого элемента 8 поступает на входы третьего 53 и че вертого 54 сумматоров, входящих в состав блока 10, а также на входы четвертого ключевого элемента 11 и первого элемента 13 памяти. Причем на четвертьй сумматор 54 сигнал 26 поступает через инвертированный На вторые входы третьего 53 и четвертого 54 сумматоров поступают сигналы,пропорциональные соответственно значениям величин X и ,., с четвертого 51 и пятого 52 элемен тов памяти соответственно. В результате сложения на выходах третьего 53 и четвертого 54 сум маторов формируются сигналы, пропор 0 ) и (Х„ -X циональные (Х Макс. сг соответственно. В случае, если (Х . )0 и ( с- ) О, на выходе пятого 55 элемента И формируется сигнал 27, являющийся выходом блока 10 и свидетельствующий об отсутствии нарушений в измерительном тракте (фиг.2). Сигнал 27 поступает на первый вход первого элемента И 9 и на управляющий вход четвертого ключевого элемента 11, разрешая прохождение измеренного значения Х. (сигнал 26) через четвертьй ключевой элемент 11 (сигнал 29). На вход первого сумматора 46 (первый вход блока 12 контроля регулятора) и на сигнальный вход первого ключевого элемента 14. На второй инвертированный вход первого сумматора 46 (третий вход блока 12 контроля регулятора) из первого элемента 13 памяти поступает значение этого же параметра, полученное в предыдущем цикле. Таким образом на выходе блока 46 формируется сигнал, пропорциональный (Xj.p| -ХСРК, ) , где к - порядковый номер цикла обращения к датчику с момента начала работы устройства. Сформированньй на выходе блока 46 сигнал сравнивается на втором элементе И 41 с сигналом flijc-i, поступанядим с выхода второго элемента 17 памяти на четвертый вход блока 12 и характеризующим состояние, в которое переведен регулятор в предыдущем цикле. При этом тенденция изменения параметра должна соответствовать состоянию, в которое переведен регулятор в предыдущем цикле, т.е. если (Хсрк -XCPK-I) О и О (что соответствует, например, повьшению температуры Хсрк при включении на предьщущем шаге нагревателя) HHKcf..0 и (Херк -Xcpn-i ) О, .то на выходе второго элемента И 41 и соответственно третьего элемента ИЛИ 58 формируется сигнал 30, являющийся выходным сигналом блока 12 контроля регулятора и свидетельствующий о нормальной работе регулятора (фиг.2), Так как в начале работы .величины и cio , хранящиеся соответственно в первом 13 и втором 17 элементах памяти, могут быть произвольными, то при первом цикле контроль работы регулятора не производится, а сигнал 30 на выходе третьего элемента ИЛИ 58 формируется непосредственно по сигналу запуска, поступающему на второй вход блока 12. При нормальной работе регулятора по сигналу 30, поступающему на управляющий вход первого ключевого элемента 14 сигнал 29, пропорционал ный значению , поступает на вход шестого сумматора 59, входящего в состав блока 16. При этом сигнал, пропорциональный допустимому значению параметра Хр , поступает на второй вход шестого сумматора 59 с шестого элемента 60 памяти. В случае, если ( ) О, то на выходе блока 59 формируется сигнал 33, являющийся выходным сигналом блока 16 вьивления отклонений и включающий регулятор 18 (фиг. 2). Этот сигнал поступает одновременно для запоминания и использования при следукяием цикле на вход второго элемента 17 памяти которьй производит запись по сигналу 31, поступающему на управляющий вход второго элемента 17 памяти. Сигнал 31 формируется первым элементом 15 задержки по сигналу 30 с выхода третьего элемента ИЛИ (выхода блока 12), задержанному на величину t, необходимую для срабатывания первого ключевого элемен та 14 и блока 16 выявления отклоне ний. В конце цикла, т.е. когда счетч 36 БУ 3 накопит m отсчетов, по сиг налу 69 (фиг.13) с его выхода на выходе первого элемента ИЛИ 35 возникает сигнал 20. По этому сигналу на выходе первого элемента И 9 формируется сигн 28 (фиг.2), разрешающий запоминани в первом элементе 13 памяти значения Хсрк. (сигнал 26), поступающего с выхода третьего ключевого элемен тов 8. Одновременно по сигналу 20 производится установка блоков в ис ходное состояние для повторного ци ла . В случае, когда количество поме на линиях передачи информации больше заданного числа п, на выхо де счетчика 38 тактов раньше сформируется сигнал 68, свидетельствую щий об окончании набора заданного количества опросовN, чем сигнал 25 на выходе счетчика 7 (фиг. 14). 016 аким образом, в этом случае по сигналу 68, прошедшему через второй элемент ИЛИ 39, запрещено прохождение тактовьк импульсов через пятый ключевой ; лемент 37 на остальные блоки дредлагаемого устройства. В результате этого в рассматриваемом цикле необходимость формирования управляющего сигнала на регулятор не выявлена и, соответственно, управляющий сигнал также не свормирован, а в конце цикла при появлении сигнала 20 на втором выходе блока 19 индикации пятым элементом И 64 по сигналу 25, поступаницему на первый вход блока 19 индикации со счетчика 7 и прошедшим через второй инвертор 61 сформирован сигнал 76 (фиг.З и 14) на включение индикатора, сигнализирующего оператору о наличии помех в тракте передачи информации. В случае неработоспособности датчика условие (2) не соблюдается, т.е. знаки разностей (Xj-p Xдд,н.) и (.акс. ср совпадают. В результате этого пятым элементом И 55, являющимся выходным элементом блока 10, не формируется сигнал 27, разрешакмций работу блоков 12 и 16 (фиг. 4 и 5). В результате этого, как и в предыдущем случае, в рассматриваемом цикле не производится выявление отклонений регулируемого, параметра от заданного допуска, не формируется управляющий сигнал на регулятор и не производится проверка работоспособности регулятора. При этом по сигналу 27, поступающему на третий вход блока 19 и проходящему через третий инвертор 62 на вход шестого элемента И 65 блока 19 при поступлении в конце данного цикла на второй вход шестого элемента И 65 сигнала 20 сформирован сигнал 77 (фиг. 4 и 5) на включение индикатора, сигнализирующего оператору о неработоспособности датчика. В случае, если тенденция изменения измеряемого параметра не соответствует положению, в которое переведен регулятор в предыдущем цикле, сигнал 30 на выходе третьего 58 элемента ИЛИ, являющийся выходным элементом блока 12 и разрешающий работу первого ключевого элемента 14 и соответственно блока 16, не формируется. Поэтому выявление отклонения измеренного значения от заданного допуска и формирование управляющего сигнала на регулятор в данном цикле не производится. При этом по сигналу 30, поступаю щему на четвертый вход блока 19 и проходящему через четвертьй инвертор 63 на вход седьмого элемента И 66 блока 19 при поступлении в конце данного цикла на второй вход седьмого элемента И 66 сигнала 20, сформирован сигнал 78 (фиг. 4 и 6) на включение индикатора, сигнализирукяцего оператору о неработоспособности регулятора. Следует отметить конструктивные особенности некоторых узлов. Первьй 14, второй 5, третий 8 и четвертый 11 ключевые элементы представляют собой сборку ключей (типа пятого ключевого элемента 37) имеющих по одному входу и одному вы ходу и управляе1Ф1х одним и тем же сигналом: для элементов 14,5,8,11 и 37 - сигналами 30, 23, 25, 27 и 70 соответственно.. Причем количество ключей в сборк определяется максимальной разрядностью передаваемой информации, а сами сборки могут быть реализованы, например на микросхемах типа К 155 ЛА обеспечивающих переключение четырех сигналов , (при запрещении прохождения сигнала через ключ Сигнал на его выходе равен нулю). Первый 46, второй 48, третий 53, четвертый 54 и пятый 56 сумматоры м гут быть реализованы, например, на микросхемах типа К 155 ИМЗ, количество которых определяется максимальной разрядностью передаваемого кода, так как каждая из них обеспечивает четырехразрядное суммирование, совместнос 1 шкрЪсхемами типа К 155 ЛН1, обеспечиваницих инвертирование входного сигнала (каждая микросхема инвертирует 6 разрядов). Следовательно, сигналы с первого 44 регистра, третьего 47, четвертого 51 и шестого 60 элементов памяти атакже с третьего ключевого элемен та 8 на суммирующие микросхемы сумматоров 46, 48, 53,59 и 54 соответственно поступают после инвертирования. В исходное состояние сумматоры приводятся путем снятия вход ного сигнала. Аналогично иэложенно му могут быть выполнены первый 42, второй 61, третий 62 и четвертый 63 инверторы. Третий 47, четвертый 51, пятый 52 и шестой 60 элементы памяти постоянно хранят записанную в них информацию ( в том числе и при выключении питания) и могут быть выполнены, например, на базе микросхемы типа К155 РТ4. Первый 13 и второй 17 элементы памяти представляют собой регистры, хранящие поступакнцую на их вход информацию и записываемую по разрешающему сигналу 28 и 31 соответственно. Каждый из элементов памяти хранит последнюю поступившую информацию, обнуляется только по выключению питания и может быть выполнен, например, на базе микросхемы типа К 155 ИР 1. Причем, если для реализации второго элемента 17 памяти достаточно одной микросхемы, так как запоминается только один бит, характеризующий состояние, в которое был переведен регулятор, то количество микросхем, необходимых для реализации первого элемента 13 памяти определяется максимальной разрядностью передаваемого кода, так как каждая микросхема представляет собой четырехразрядный регистр. Аналогично выполняются первый 44 и второй 45 регистры за исключением того, что их обнуление производится вначале каждого цикла по сигналу 20. Сумматор работает следукицим образом. Вначале работы по сигналу 20, поступающему на первый вход сумматора 6, происходит обнуление промежуточного 81 и выходного 80 регистров. При как второй ключевой элемент 5 закрыт, то на втором входе сумматора 6 и, соответственно, входах суммирующего 79 элемента, промежуточного регистра 81 и схемы 82 сравнения кодов - нулевые значения сигналов. В этом случае и на выходе элемента 82 сравнения кодов формируется нулевой сигнал, запрещающий запись в регистры 80 и 81. При поступлении на второй вход сумматора 6 информации элементом 82 сравнения кодов формируется сигнал, разрещающий запись поступившего кода в регистр 81 и регистр 80 (после прохождения через суммирующий элемент 79) . Записанная в регистр 80 информация является выходным сигналом сумматора 6 и поступает на второй вход суммирующего элемента 79. Однако, так как коды, посгупакмдие на оба входа элемента 82 сравнения, равны, то запись информации с выхода сум- мирующего элемента в регистр 80 не производится. При смене кода, посту пающего на второй вход сумматора 6 вькода второго ключевого элемента 5 элемент 82 сравнения кодов вновь формирует сигнал, разрешающий запис в регистры 81 и 80 и, таким образом, на выходе регистра 80 формируется сигнал, пропорциональный сумме всех поступивших входных сигналов. Указанный процесс повторяется д тех пор, пока БУ 3 не сформирует сигнал 20, устанавливающий регистры 80 и 8t в исходное положение. Необходимо отметить что устройство может быть использовано без принципиальных изменений для управл ния .несксшькими регуляторами по информации с нескольких датчиков. В этом случае устройство должно быть 020 дополнено коммутатором, подключающим датчики к входу АЦП 2; коммутатором, включающим к выходу блока 16 соответствующий регуляторj блоком оперативного запоминающего устройства (ОЗУ), в ячейках которого хранится для каждого из каналов управления для правильной работы блоков 4,10, 12 и 16; коммутатором, подкЛючаю1цим элементы памяти 13, 17, 47, 51, 52 и 60 к соответствующим ячейкам ОЗУ, а также блоком управления, перечисленными коммутаторами и ОЗУ и обеспечивающими переключение каналов управления. Как следует из изложенного, при возникновении помех на линиях связи, а также при нарушении работоспособности измерительного тракта или регулятора в устройстве не производится сопоставление значения с соответствующей .уставкой и не формируется управлякяций сигнал на регулятор, который в этом случае может оказаться ошибочным.

Фиг.

Фаг. 7

ВО

Фиг.д

Фиг.Ю

S3

Фог. 11

flDw./J

| Способ анодирования алюминия | 1968 |

|

SU452630A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и регулирования технологических параметров | 1977 |

|

SU611214A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-07-13—Подача