113

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей форм информации.

Цель изобретения - расширение функциональных возможностей путем генерации различных форм выходного аналогового сигнала.

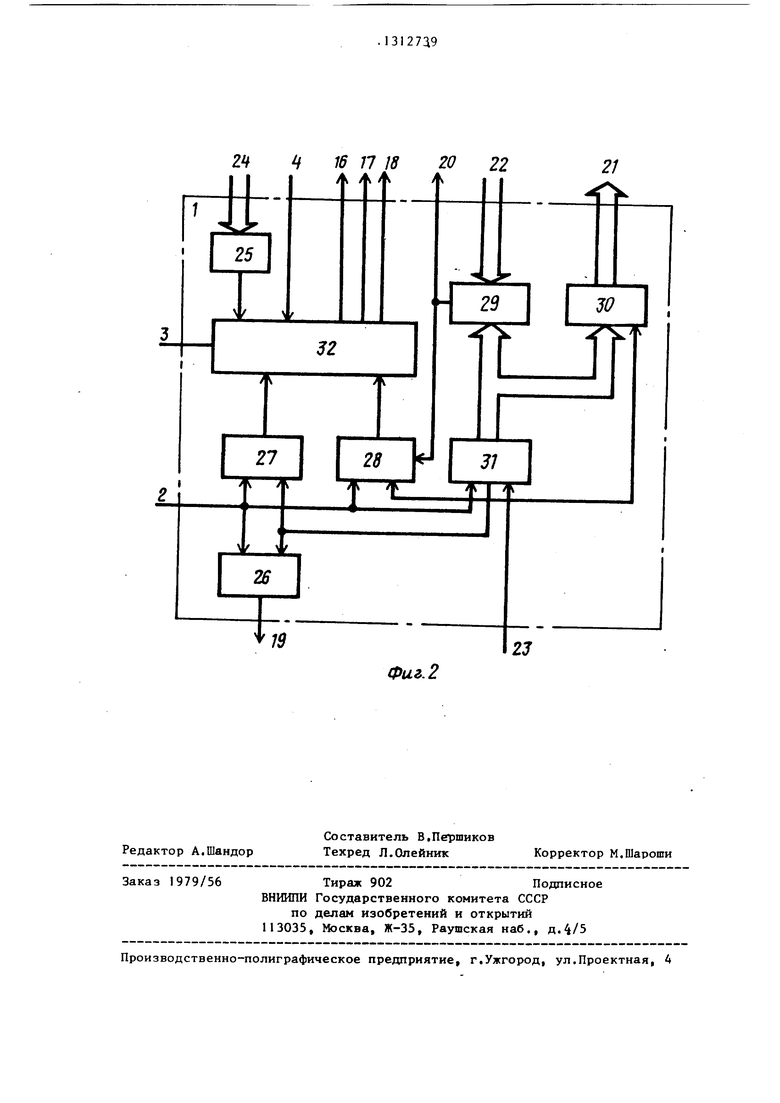

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока управления.

Устройство цифроаналогового преобразования содержит блок 1 управления, первый управляющий вход 2, информационный вход 3, второй управляющий вход 4, блок 5 коммутации, первый 6 и второй 7 коммутаторы, реверсивный счетчик 8, блок 9 регистров, блок 10 синтеза кодов, блок 11 цифровых схем сравнения, аналоговый запоминающий блок I2, цифроанало- говый преобразователь (ЦАП) 13, выходную шину 14 устройства, блок 15 сравнения, при этом блок 1 управления имеет выходы с первого по пятый 16-20, шестые выходы 21, первый и второй входы, являющиеся соответственно первым управляющим входом 2 и информационным входом 3 устройства, третьи входы 22, четвертый вход 23, пятые входы 24 и шестой вход, являющийся вторым управляющим входрм 4 устройства.

Блок 1 управления (фиг.2) выполнен на первом 25 и втором 26 элементах ИЛИ, первом 27 и втором 28 триггерах, мультиплексоре 29, демульти- плексоре 30, счетчике 31 и распределителе 32 импульсов. I

Блок 15 сравнения осуществляет

сравнение аналоговьк сигналов А1 на выходе ЦАП 13 и А2 на выходе блока 12, причем сигнал Y на его выходе подчиняется соотношению

.{0.

Ь,

если А1 7/ А2, если А1 А2,

ЦАП 13 - п-разрядный цифроаналоговый преобразователь, построенный

БСК-,

Ч

О, если i i п - m,

(СТ| i m-n+г 2 |Чт-п42

Работа устройства начинается с процесса самоповерки. При этом опре2

на основе избыточного измерительного кода.

Блок 11 состоит из m цифровых схем сравнения и осуществляет сравнение на равенство содержимого группы разрядов реверсивного счетчика 8 с кодовыми комбинациями с выхода блока 5. В случае равенства содержимого группы из (п - m i) младших разрядов счетчика 8 и кодовой комбинации на выходе блока 5 блок I1 вырабатывает сигнал Z,- 1 .

Сигнал X на втором управляющем входе 4 определяет режим работы устройства. При X 1 устройство вьфа- батывает линейно нарастающий аналоговый сигнал, при X О происходит генерация линейно падающего сигнала. При зтом комбинации кодов БК на

выходе блока 5 определяются следующим логическим выражением:

БKj РГ. X + (100...0) X,

где РГ,- - содержимое i-ro регистра

блока 9.

Первый коммутатор 6 передает на выход содержимое одного из регистров блока 9, Номер i подключаемого регистра определяется единичным уровнем сигнала Z блока 11, т.е. логическая функция,реализуемая первым коммутатором 6, может быть описана логическим выражением

Pr,-Z, ч- РГ2- Zi -ь...- РГ. Z.

Второй коммутатор 7 передает, в зависимости от режима работы устройства, на вход счетчика 8 содержимое одного из регистров блока 9 (при

X 0) или блока 10 (при X I).

Блок 10 синтеза кодов формирует кодовую комбинацию, записываемую в счетчик 8 в режиме генерации линейно нарастающего сигнала, после появления на выходе счетчика 8 переходной кодовой комбинации. Кодовая комбинация для записи в счетчик 8 формируется по содержимому счетчика 8 и выходному сигналу Z. блока 11,причем ее i-й разряд формируется следующим образом:

... Z, е ели i п - m.

деляются переходные кодовые комбинации К,-. Переходная кодовая комбина3,1312739

ция является одной из форм представления входной цифровой величины, для которой выходная аналоговая величина А1 ЦАП 13 соответствует заданной цифровой величине с точностью до младшего кванта. Переходная кодовая комбинация К| соответствует аналоговой величине Л1; на выходе преобразователя, значение которой определяется cлeдyюI им образом:

10

А1,- Qi - Q,,

где Q- - реальный вес 1-го разряда

ЦАП 13; Q - вес младшего разряда.

Определение переходных кодовых комбинаций начинается с разряда, вес которого бтличается от двоичного веса. Так,для I-кода Фибоначчи с младшими разрядами ... 8, 5, 3, 2, 1 определение переходных кодовых комбинаций должно производиться с 3-го разряда.

Самоповерка устройства начинается при поступлении сигнала на первый уп равляющий вход 2, Число-импульсный код, поступающий на информационный вход 3, начинает поступать на вход

прямого счета счетчика 8, I

При включении поверяемого разряда счетчика 8 блок 1 переводит блок 12 в режим хранения аналоговой величины А1 с выхода ЦАП 13, соответствующий весу контролируемого разряда, а входные импульсы начинают про

ходить на вход обратного счета счет- 1. Устройство цифроаналогового

чика 8 до момента срабатьшания блокапреобразования, содержащее блок уп)5 сравнения. Изменения сигнала Yравления, первый вход которого являна выходе блока 15 из О в 1 про- Qется первой управляющей шиной, вто- исходят в момент равенства содержимого счетчика 8 переходной кодовой комбинации поверяемого разряда и вызывают запись этой комбинации в

соответствующий регистр блока 9,ПЬс- входам записи прямого счета, обратноле этого аналогично определяются пе-го счёта и обнуления реверсивного

реходные кодовые комбинации для еле-счетчика, выходы которого подключедующих разрядов,ны к соответствующим первым входам

После определения всех переход-блока цифровых схем сравнения, перных комбинаций устройство переходит Qвым входам блока синтеза кодов, инрой вход является входной информационной шиной, первый, второй, третий и четвертый выходы блока управления подключены соответственно к

к непосредственному преобразованию.

Преобразуемый число-импульсный код поступает на информационный вход 3 устройства. Счетчик 8 осущеформационным входам блока регистров, третьим входом блока управления и входам цифроаналогового преобразователя, выход которого является выходствляет преобразование входных счет- ной шиной устройства и подключен к

ных импульсов в рабочий код, в ре-информационному входу аналогового

зультате чего на выходе ЦАП 13 появ-запоминающего блока и первому входу

ляется аналоговый сигнал, величинаОлока сравнения, второй вход которокоторого пропорциональна количеству/о подключен к выходу аналогового

0

0

5

импульсов, поступающих на вход устройства. Причем, в зависимости от сигнала на входе 4 счетчик 8 может работать как в режиме прямого, так и обратного счета. При этом в режиме прямого счета соответствующая группа разрядов счетчика постоянно сравнивается с содержимым каждого из регистров блока 9, а в процессе обратного счета - с кодовыми комбинациями вида 10...О, т.е. соответствующими включению i-ro старшего разряда и вьжлюченным более младшим разрядом. Если после поступления очередного

5 счетного импульса блок 11 выработал сигнал Z 1, то счетчик 8 переводится в режим записи. В режиме генерации линейно нарастающего сигнала в счетчик 8 записывается формируемый блоком 10 код, аналоговый эквивалент которого точно на величину младшего кванта больше выходной аналоговой величины ЦАП 13 на данном такте, В режиме генерации линейно падакя;его сигнала в счетчик записывается i-переходная кодовая комбинация из блока 9, аналоговый эквивалент которой точно на величину младшего кванта меньше выходной аналого0 вой величины ЦАП 13,

Затем счетчик переходит в режим прямого либо обратного счета до следующего срабатывания блока 11,

5 Формула изобретения

ется первой управляющей шиной, вто-

рой вход является входной информационной шиной, первый, второй, третий и четвертый выходы блока управления подключены соответственно к

формационным входам блока регистров, третьим входом блока управления и входам цифроаналогового преобразователя, выход которого является выход513

запоминающего блока, выход подключен к четвертому входу блока управления, пятый выход которого подключен к уп- равляюшему входу аналогового запоминающего блока, шестые выходы подключены к соответствующим управляющим входам блока регистров, пятые входы блока управления объединены с соответствующими вторыми входами блока (интеза кодов и подключены к соответствующим выходам блока цифровых схем сравнения, о тличающее- с я тем, что, с целью расширения функциональных возможностей за счет генерации различных форм выходного аналогового сигнала, в него введены первый и второй коммутаторы и блок коммутации, выходы которого подключены к соответствующим вторым входам блока цифровых схем сравнения, управляющий вход объединен с управляющим входом второго коммутатора, шестым входом блока управления и является второй управляющей шиной, информационные входы блока коммутации подключены к соответствующим выходам блока регистров и объединены с соответствующими информационными входами первого коммутатора, управляющие входы которого подключены к соот ветствующим выходам блока цифровых схем сравнения, а выходы подключены к соответствующим первым информацион ным входам второго коммутатора,вторые информационные входы которого подключены к соответствующим выходам блока синтеза кодов, а выходы подклю чены к соответствукяцим информацион- ньп входам реверсивного счетчика.

2, Устройство по п.1, о т л и - чающе е с я тем, что блок управ ления вьшолнен на первом и втором

27396

элементах ИЛИ, первом и втором триггерах, мультиплексоре, демультиплек- соре, счетчике, распределителе импульсов, информационный вход которо5 го является вторым входом блока управления, первый управляющий вход подключен к выходу первого элемента ИЛИ, входы которого являются пятыми входами блока управления, второй уп 0 равляющий вход распределителя импульсов является шестым входом блока управления, первый, второй и третий выходы распределителя импульсов являются соответственно первым, вто15 рым и третьим выходами блока управления, третий и четвертый управляющие входы раслределителя импульсов подключены соответственно к выходам первого и второго триггеров, первые

20 входы которых объединены с первым входом счетчика и первым входом второго элемента ИЛИ и являются первым входом блока управления, второй вход первого триггера объединен с вторым

входом второго элемента ИЛИ и подключен к выходу переполнения счетчика, второй вход которого объединен с вторым входом второго триггера, информационным входом демультиллек30

сора и является четвертым входс м

блока управления, вьгходы разрядов счетчика подключены к соответствую.- щим управляющим входам демультиплек- сора и мультиплексора, информационные входы которого являются третьими входами блока управления, выход подключен к третьему входу второго триггера и является пятым выходом блока управления, при этом выход второго

элемента ИЛИ является четвертым вы- ходом, а выходы демультиплексора - шестыми выходами блока управления.

2 Ц 16 17 8 20 22

21

Редактор А.Шандор

Составитель В.Першиков Техред Л.Опейник

Заказ 1979/56

Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фиг.2

Корректор М.Шароши

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197078A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221755A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при преобразовании число-импульсного кода в аналоговую величину, Цель изобретения - расширение функциональных возможностей путем генерации различных форм выходного сигнала. Устройство содержит блок I управления, первый управляющий вход 2, информационный вход 3, второй управляющий вход 4, блок 5 коммутации, первый 6 и второй 7 коммутаторы, реверсивный счетчик 8, блок 9 регистров, блок 10 синтеза кодов, блок 11 цифровых схем сравнения, аналоговый запоминающий блок 12,цифроаналоговый преобразователь 13,построенный на основе избыточного измерительного кода, выходную шину 14, блок 15 сравнения. Введение блока 5, коммутаторов 6,7 и второго управляющего входа 4 обеспечивает возможность генерации устройством как линейно нарастающего, так и линейно падающего аналоговых сигналов в зависимости от сигнала на входе 4. Использование избыточных измерительных кодов и наличие режима самопот верки обеспечивают высокую точность преобразования. 1 з.п.ф-лы, 2 ил. с (Л С со ISD со :О

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| - М.: Энергия, 1975, с.292, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221755A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-23—Публикация

1985-09-19—Подача