Известны устройства з.множения, оперирующие с полноразрядными десятичными числами. В известных устройствах сложным для реализации является десятичное умножение, если применяются методы ускорения этой операции, иснользующие кратные множимого.

Целью изобретения является экономия оборудования.

Предлагаемое устройство отличается от известных тем, что десятичное умножение выполняется путем прибавления кратных множимого - удвоенного и (или) упятеренлого - без их предварительной заготовки, а лиШь введением специальных коррекций дри сложении. При таком ностроении схемы устройства не требуются специальные регист-ры для хранения кратных множимого.

Сущность изобретения заключается в том, что один вход схемы формирования сигнала двоичного сложения тетрад соединен с шиной сигнала двоичного сложения, другой ее вход соединен с выходом первой схемы «НЕ, с первым .входом схемы формирования сигнала двоичного сложения тетрад со сдвигом влево на один разряд и с входом схемы формирования сигнала двоичного сложения тет рад со сдвигом влево на три разряда; третий вход схемы формирования сигнала двоичного сложения тетрад соединен со вторым входом

2

схемы формирования сигнала двоичного сложения тетрад со сдвигом влево на один разряд, с одним входом схемы анализа тетрад и выходом регистра множимого; выход схемы формирования сигнала двоичного сложения тетрад Подключен к перво.му входу накапливающего сумматора частичных произведений, второй вход которого связан с выходом схемы формирования сигнала двоичного

тетрад со сдвигом влево на один разряд, третий вход которой соединен с шиной сигнала двоичного сложения со сдвигом влево на один разряд и с первыми входами первой, второй и третьей схем «И, вторые

входы которых и первые входы четвертой пятой, шестой, седьмой и восьмой схем «И и вход первой схемы «НЕ подключены к шине сигнала формирования коррекции; третьи вхолчы первой и второй схем «И нодключены к одному из выходов схемы анализа тетрад, дрзгой выход которой соединен с четвертым входом первой схемы «И и вторым входом шестой схемы «И, третий выход схемы анализа тетрад подсоединен к четвертому

входу второй схемы «И и к третьему входу третьей схемы «П, выходы первой и второй схем «И соединены со входами первой схемы «ИЛИ, выход которой подключен к третьему входу накапливающего сумматора частичных произведений, четвертый вход которого подсоединен к выходу схемы формирования сигнала двоичного сложения тет;рад со сдвигом вле1во на три -разряда, второй вход которой подключен ж шине регистра множимого предшествующей тетрады, и третий вход соединен со вторы.мн входами пятой, седьмой и восьмой схем «И, со входом второй схемы «НЕ и с шиной сигнала двоичного сложения со сдвигом влево на три разряда; второй вход четвертой схемы «И и третий вход пятой схемы «И подключены к четвертому выходу схемы анализа тетрад, пятый выход которой подсоединен к четвертому входу пятой схемы выход последней соединен с первым входом второй схемы «ИЛИ, второй, третий и четвертый входы которой подсоединены соответственно к выходам третьей, четвертой и шестой схем выход второй схемы «ИЛИ подключен к пятому входу -накапливающего сумматора частичных произведений, шестой вход которого соединен с выходом восьмой схемы выход второй схемы «НЕ соединен .с третьими входами четвертой и шестой схем «И, четвертые входы третьей и шестой схем «И подключены к шестому выходу cxej мы анализа тетрад, седьмой выход которой соединен с третьими входами седьмой и восьмой схем восьмой выход схемы анализа тетрад соединен с четвертым входом восьмой схемы «И, девятый выход схемы анализа тетрад подключен к четвертому входу седьмой схемы «И, выход которой соединен с седьмым входом накапливающего сумматора частичных произведений, выход последнего подключен к другому входу схемы анализа тетрад.

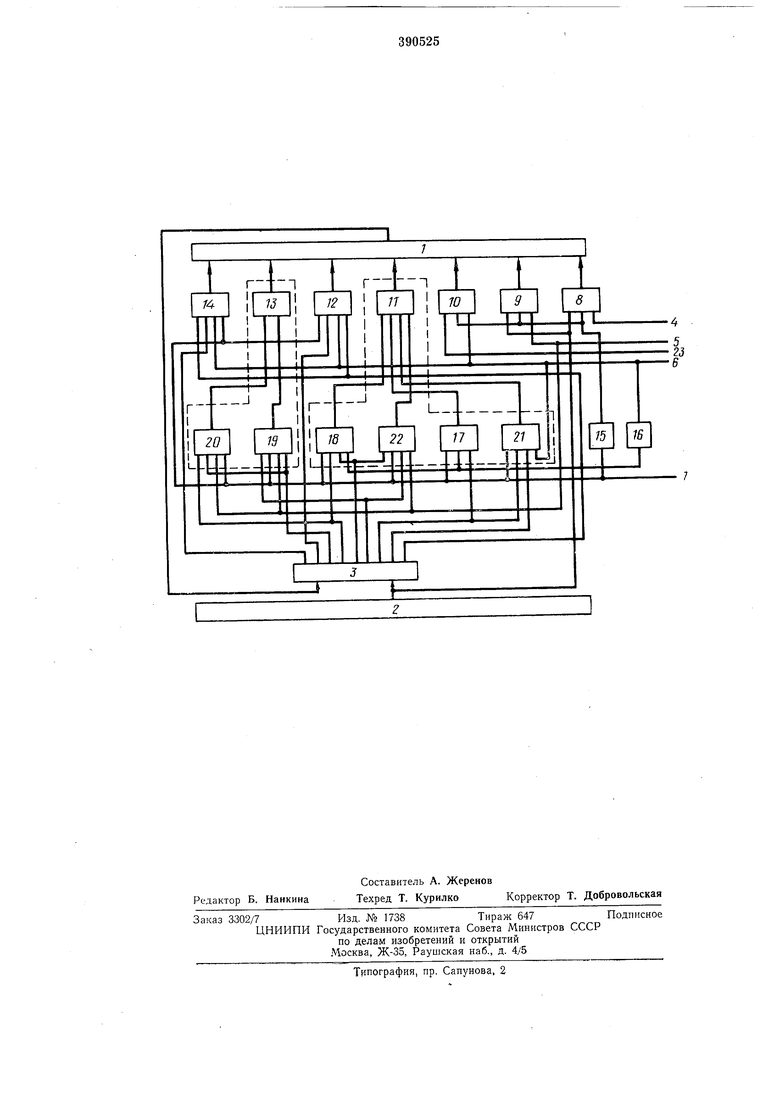

На чертеже представлена схема устройства на одну тетраду.

Устройство содержит накапливающий сумматор / частичных произведений, регистр множимого 2, схему 3 анализа тетрад, шинусигнала двоичного сложения, шину 5 сигнала двоичного сложения со сдвигом влево на один разряд, шину 6 сигнала двоичного сложения со сдвигом влево на три разряда, шину 7 сигнала формирования коррекции, схему S формирования сигнала двоичного сложения тетрад, схему 9 формирования сигнала двоичного сложения тетрад со сдвигом влево на один разряд, схему 10 формирования сигнала двоичного сложения тетрад со сдвигом влево на три разряда, схему «ИЛИ /У формирования коррекции на «6, схему «И /2 формирования коррекции на «5, схему «ИЛИ 13 формирования коррекции на «12, схему «И 14 формирования коррекции на «11, схемы «НЕ 15 и 16 (инверторы коррекции), схемы «И 17-22, шину 23 регистра множимого предшествующей тетрады.

Схемы и блоки коррекции служат для формирования правильной десятичной суммы после двоичного сложения.

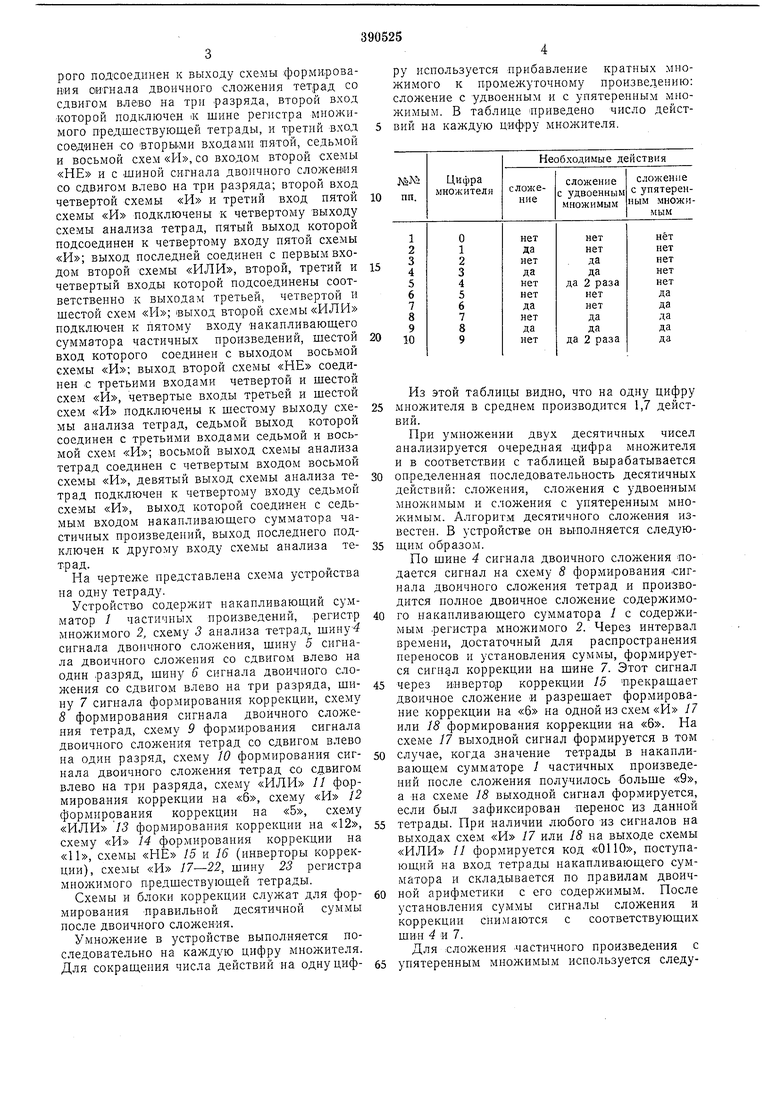

Умножение в устройстве выполняется последовательно на каждую цифру множителя. Для сокращения числа действий на одну цифру используется прибавление кратных множимого к промежуточному произведению: сложение с удвоенным и с упятеренным множимым. В таблице приведено число дейстВИЙ на каждую цифру множителя.

Из этой таблицы видно, что на одну цифру

множителя в среднем производится 1,7 действий.

При умножении двух десятичных чисел анализируется очередная .цифра множителя и в соответствии с таблицей вырабатывается

определенная последовательность десятичных действий: сложения, сложения с удвоенным множимым и сложения с упятеренным множимым. Алгоритм десятичного сложения известен. В устройстве он выполняется следующим образом.

По шине 4 сигнала двоичного сложения Подается сигнал на схему 8 формирования сигнала двоичного сложения тетрад и производится полное двоичное сложение содержимого накапливающего сумматора 1 с содержимым регистра множимого 2. Через интервал времени, достаточный для распространения переносов и установления суммы, формируется сигнал коррекции на щине 7. Этот сигнал

через инвертор коррекции /5 прекращает двоичное сложение и разрешает формирование коррекции на «6 на одной из схем «И П или 18 формирования коррекции на «6. На схеме /7 выходной сигнал формируется в том

случае, когда значение тетрады в накапливающем сумматоре 1 частичных произведений после сложения получилось больше «9, а на схеме 18 выходной сигнал формируется, если был зафиксирован перенос из данной

тетрады. При наличии любого из сигналов на выходах схем «И П или 18 на выходе схемы «ИЛИ 11 формируется код «ОНО, поступающий на вход тетрады накапливающего сумматора и складывается по правилам двоичной арифметики с его содержимым. После

установления суммы сигналы сложения и

коррекции снимаются с соответствующих

шин .

Для сложения -частичного произведения с

упятеренным мнолсимым используется следующая закономерность: двоичные разряды 8, 4, 4 к-й тетрады множимого складываются с раз-рядами 4, 2, 1 (к-1)-й тетрады частичного произведения по правилам двоичной арифметики: разряд 1 /с-й тетрады указывает, нужно ли прибавлять код «5 в эту тетраду, и это учитывается при кор-рекции сложения.

Правила коррекции суммы после двоичного сложения таковы:

тетрада, где сумма получилась больше «9 и разряд 1 тетрады множимого равен нулю, корректируется на

тетрада, в которой разряд тетрады множимого равен «1, корректируется на «5, если сумма получилась меньше пяти, или корректируется на «11, если сумма получилась больше пяти.

Для сложения с упятеренным множимым по шине 6 сложения со сдвигом влево на три разряда подается сигнал на схему 10 сложения тетрад со сдвигом влево на три разряда, которая пропускает содержимое регистра множимого 2 на накапливаюший сумматор 1 частичных произведений таким образом, что 8, 4, 2 разряды (к-1)-й тетрады поступают по шине 23 младшей тетрады в 4, 2, 1 разря-, ды к-й тетрады, и организует полное двоичпое сложение вышеуказанных тетрад в накапливающем сумматоре.

Сигнал по шине сложения 6 поступает также на схемы коррекции па , на 14, на схему «И 21 и на схему «НЕ 16, выход которой блокирует коррекцию на «6 на схемах «И 17 и 18. После установления суммы подается сигнал по шине 7 сигнала формирования коррекции, который блокирует сложение иа схеме 10 и разрешает формирование коррекции на схемах 14, 12 и 21. На схеме 21 выходной сигнал формируется в том случае, когда первый разряд тетрады множимого равен «О и получившееся значение тетрады иа.капливающего сумматора после сложения больше «9. Выход схемы 21 соединен со схемой «ИЛИ 11, формируюидей сигнал коррекции па «6. На схеме «И 12 выходной сигнал образуется в том случае, когда первый разряд тетрады множимого равен «1 и получившееся значение тетрады накапливающего сумматора -после сложения меньше «5. Выходной сигнал схемы 12 в виде кода «0101 поступает на вход тетрады сумматора / и складывается с его содержимым по правилам двоичной арифметики.

На схеме 14 выходной сигнал вырабатывается в том случае, когда первый разряд тетрады множимого равен «Ь и получившееся значение тетрады сумматора 1 после сложения больше или равно «5. Выходной сигнал в виде кода «1011 -поступает на вход тетрады сумматора и складывается с его содержимым по правилам двоичной арифметики. После установления суммы при коррекции сигналы сложения с унятеренным м.ножимым и Коррекции по шинам б и 7 снимаются.

Для сложения частичного произведенИЯ с удвоенным множимым используется закономерность: двоичные разряды 8, 4, 2, 1 к-й тетрады множимого складываются с разрядом 1 (к-1)-й тетрады и с разрядами 8, 4, 2 к-й тетады частичного произведения по правилам двоичной аррифметики, тем самым осуществляется сложение со сдвигом на один разряд влево.

Правила коррекции суммы после двоичного сложения таковы:

-тетрада, где сумма получилась больше или 1равной «4, и тетрада множимого больше или равной «8, корректируется на

- тетрада, где сумма -получилась больили равной «4 и при двоичном сложении был зафиксирован перенос, корректируется на

-тетрада, где сумма получалась больше «9, Корректируется на

-тетрада, где сумма лолучилась меньше «4 и -при двоичном сложении был зафиксирован перенос, корректируется на

-тетрада, где сумма получилась меньше «4, и тетрада -множимого больше или равна 8, корректируется на «6.

Для сложения с удвоенным множимым по шине 5 сложения со сдвигом па один разряд

влево подается сигнал на схему 9 формирования сигнала двоичного сложения тетрад со сдвигом влево на один разряд. Формируется сигнал полного двоичного сложения таким образом, что разряды 8, 4, 2, 1 к-й тетрады

множимого складываются с разрядом 1 (к-1)-й тетрады и с разрядами 8, 4, 2 к-й тетрады накапливающего сумматора /. Этот же сигнал поступает па схему «И 22 формирования коррекции на «6 и на схемы «И

19 и 20 формирования коррекции на «12. После установления суммы подается сигнал коррекции по шине 7. который блокирует сложение .с удвоенным множНЛ1ым и разрешает формирование коррекции на схемах

«И 17-20, 22. На схеме 17 выходной сигнал образуется в том случае, когда получившееся значение тетрады накопительного сумматора после сложения больше «9. На схеме 18 выходной сигнал формируется в том случае,

когда при сложении с удвоенным М ожимым был заф)иксирован перенос и получившееся значение тетрады -накопительного сумматора меньше «4. На схеме 22 выходной сигнал образуется в том случае, когда получившееся

значение тетрады накопительного сумматора / после сложения с удвоенным множимым меньше «4, а тетрада множимого больше или равна «8.

С выходов схем 17, 18 и 22 сигналы через

схему // в виде кода «ОНО поступают на вход сумматора /.

На схеме совпадения 19 выходной сигнал появляется в том случае, когда значение тетрады сумматора / после сложения с удвоенным множимым больше или равно «4, а соответствующая тетрада множимого больше или равна «8.

На схеме «И 20 выходной сигнал формируется в том .случае, когда при сложении с )двоенным множимым был зафиксирован перенос из соответствующей тетрады накопительного сумматора / и его зн-ачение больше или равно «4.

С выходов схем 19, 20 сигналы через схему «ИЛИ 13 в виде кода «1100 поступают на вход тетрады сумматора /, где производится обычное сложение с его содержимым. После установления суммы при коррекции сигнал сложения со сдвигом на один разряд влево и сигналы коррекции снимаются с шин 5 и 7.

Предмет и з о -б р е т е и и я

Устройство для умножения десятичных чисел, содержащее накапливающий сумматор частичных Произведений, регистр множимого, схему анализа тетрад, схему формирования сигнала двоичного сложения тетрад, схему формирования сигнала двоичного сложения тетрад со сдвигом влево на один разряд, схему формирования сигнала двоичного сложения тетрад со сдвигом влево на три разряда, схемы формирования коррекции на пять, «а шесть, на одиннадцать и на двенадцать, выполненные на логических элементах «И, «ИЛИ, «НЕ, отличающееся тем, что, с целью экономии оборудования, один вход схемы формирования сигнала двоичного сложения тетрад соединен с шиной сигнала двоичного сложения, другой ее вход соединен с выходом «ервой схемы «НЕ, с первым входом схемы формирования сигнала двоичного сложения тетрад со сдвигом влево на один разряд и с первым входом схемы формирования сигнала двоичного сложения тетрад со сдвигом влево на три разряда; третий вход схемы формирования сигнала двоичного сложения тетрад соединен со вторым входом схемы формирования сигнала двоичного сложения тетрад со сдвигом влево на один разряд, с одним входом схемы анализа тетрад и вььходом регистра множимого; выход схемы формирования сигнала двоичного сложения тетрад подключен к первому входу накапливающего сумматора частичных нроизведений, второй вход которого связан с выходом схемы формирования сигнала двоичного сложения тетрад со сдвигом влево на один разряд, третий вход которой соединен с щиной сигнала двоичного сложения со сдвигом

влево на один разряд и с первыми входами первой, второй и третьей схем «И, вторые входы которых и первые входы четвертой, пятой, шестой, седьмой и восьмой схем «И и

вход первой схемы «НЕ подключены к шине сигнала формирования коррекции; третьи входы первой и второй схем «И подключены к одному из выходов схемы анализа тетрад, другой выход которой соединен с четвертым входом первой схемы «И и вторым входом шестой схемы «И, третий выход схемы анализа тетрад иодсоедипен к четвертому входу второй схемы «И и к третьему входу третьей схемы выходы первой и

второй схем «И соединены со входами первой схемы «ИЛИ, выход которой подключен к третьему входу накапливающего сумматора частичных произведений, четвертый вход которого подсоединен к выходу схемы формирования сигнала двоич-ного сложения тетрад со сдвигом влево на три разряда, второй вход которой подключен к шине регистра множимого предшествующей тетрады, а третий вход соединен со вторыми входами пятой, седьмой

и восьмой схел1 «И, со входом второй схемы «НЕ и с шиной сигнала двоичного сложения со сдвигом влево на три разряда; второй вход четвертой схемы «И и третий вход пятой схемы «И подключены к четвертому выходу

схемы анализа тетрад, пятый выход которой подсоединен к четвертому входу пятой схемы выход последней соединен с первым входом второй схемы «ИЛИ, второй, третий и четвертый входы которой подсоединены соответственно к выходам третьей, четвертой и шестой схем выход второй схемы «ИЛИ подключен к пятому входу накапливающего сумматора частичных произведений, шестой вход которого соединен с выходом

восьмой схемы выход второй схемы «НЕ соединен с третьими входами четвертой и шестой схем «И, четвертые входы третьей и шестой схем «И подключены к шестому выходу схемы анализа тетрад, седьмой

выход которой соединен с третьими входамн седьмой и восьмой схем восьмой выход схемы анализа тетрад соединен с четвертым входом восьмой схемы «И, девятый выход схемы анализа тетрад подключен к четвертому входу седьмой схемы «И, выход которой соединен с седьмым входом накапливающего. с Мматора частичных произведений, выход посотедиего подключен к другому входу схемы анализа тетрад., ., - .

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU669352A1 |

| Устройство для умножения | 1982 |

|

SU1157542A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Устройство для умножения двоично- десятичных чисел | 1977 |

|

SU748409A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

Даты

1973-01-01—Публикация