°3.1580366

триггеров, группу 14 элементов ИЛИ, /тве группы 16, 17 элементов И и мультиплексор 18. Анализатор обеспечивает за один цикл контроля получение сигнатур)- первого порядка и m сигнатур

в

второго порядка для последовательностей, образованных разложением исходной последовательности по системе функций Радемахера. 1 ил. 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1989 |

|

SU1714602A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

Изобретение относится к вычислительной технике и может использоваться для тестого диагностирования цифровых объектов. Анализатор содержит два счетчика, первый триггер, первую группу триггеров, первую группу элементов И и мультиплексор. С целью увеличения быстродействия и повышения достоверности контроля, анализатор содержит группу элентов ИЛИ, два элемента И, вторую группу элементов И, вторую группу триггеров, второй, третий и четвертый триггер, две группы блоков памяти. 1 ил.

Изобретение относится к вычисли- , тельной-технике и может использоваться для тестового диагностирования цифровых объектов.

Цель изобретения - увеличение бы- стродействия и повышение достоверное ти контроля.

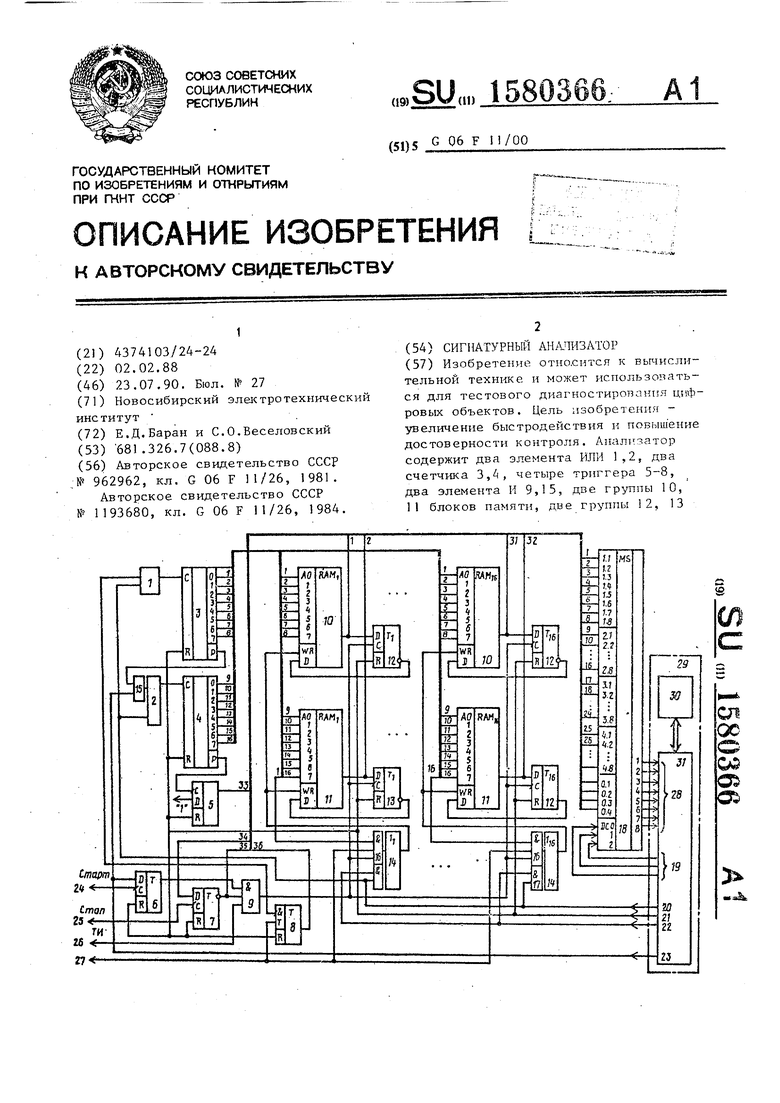

На чертеже представлена схема сигнатурного анализатора.

Сигнатурный анализатор содержит первый 1 и второй 2 элементы ИЛИ, первый 3 и второй 4 счетчики, первый 5, второй 6, третий 7, четвертый 8 триггеры, второй И 9, первую группу 10 блоков памяти, вторую группу 11 блоков памяти, первую 12 и вторую 13 группы триггеров, группу элементов ИЛИ 14, первый элемент.И 15, первую 16 и вторую 17 группы элементов -И, мультиплексор 18, группу 19 входов задания режима, вход 20 записи/считывания, вход 21 сброса, вход 22 задания режима, вход 23 разрешения, вход 24 старт, вход 25 стоп, тактовый 26 и информационный 27 входы, группа 28 информационных выходов анализатора. t Контроллер 29, ЭВМ 30, интерфейсный блок 31.

Рассматривается принцип действия анализатора, выделив при этом в про

цедуре получения сигнатур три режима: подготовку к работе (очистку памяти); определение четности числа векторов фиксированного вида, на которые попадают единичные символы контролируемой последовательности; суммирование векторов.

На этапе подготовки к работе контроллер 29 подает на вход элемента И 15 и на D-вход триггера 6 сигнал . О, запрещая тем самым восприятие внешних сигналов Старт, Стоп, Синхр, а на вход всех элементов И 17 подает сигнал разрешения очистки блоков 10 и 11 памяти.

Кроме того,контроллер 29 по группе выходов режима устанавливает на управляющих входах мультиплексора 18 код 000 для считьюания в контроллер

5

„ 5

0

5

0

5

0

5

через нулевой канал мультиплексора слова состояния анализатора- -вьгходных сигналов триггеров 5-8. Одновременно контроллер 29 подает на входы сброса R-счетчиков З и 4, а также всех триггеров (5-8, 12 и 13) сигнал Сброс, после чего формирует импульсы очистки блоков памяти. Эти импульсы с выхода контроллера 29 проходят через элементы 1 и 2 на входы синхронизации счетчиков 3 и 4 соответственно, а через элементы 17 и 14 на входы записи WR соответствующих блоков 10 и 11 памяти. При этом во все ячейки всех блоков 10 и 11 памяти с выходов триггеров 12 и 13 записывается 1. По окончании записи в последнюю 2 2-ю ячейку блоков памяти импульс переполнения счетчика 4 поступает на С-вход триггера 5 и устанавливает его в 1. Сигналом с выхода триггера 5 контроллер 29 через нулевой канал мультиплексора 18 информируется об окончании первого цикла. При этом контроллер прекращает формирование импульсов очистки памяти, восстанавливает сигнал О на входе элементов 17 и подает сигнал Сброс, установки триггеров и счетчиков в исходное состояние.

В начале второго цикла контроллер 29 подает 1 на D-вход триггера 6 и на вход элемента И 15. При этом вход счетчика 4 через элемент ИЛИ 2 и элемент И 15 соединяется с выходом переполнения счетчика 3, вход которого через элемент ИЛИ 1 и элемент И 9 соединяется с тактовым входом анализа-. тора. Анализатор переходит в режим ожидания внешних управляющих сигналов,, а контроллер следит за состоянием триггеров 5-8 через нулевой канал мультиплексора 18.

Формирование сигнатуры начинается

с приходом сигнала Старт, по которому триггер 6 устанавливается в 1, открывается элемент И 9, импульсы с

тактового входа анализатора через элемент И 9 и элемент ИЛИ 1 проходят на

, вход счетчика 3, кроме того, импульсы с выхода элемента И 9 поступают на тактовые входы всех триггеров 12 и 13 и на входы всех элементов И 16. На другие входы этих элементов приходят символы контролируемой последовательности с входа 27 устройства и сигналы с соответствующих выходов счетчиков 3 и 4.

В процессе счета импульсов контролируемой последовательности опрашиваются соответствующие ячейки всех блоков 10 и 11. Если на некотором такте символ контролируемой последовательности равен }«. 1 , то откроются те элементы И 16, на первые входы которых с, выходов счетчиков 3 или 4 поступают сигналы a i; 1 . Очевидно, что а 1 для тех выходов счетчиков, для которых двоичная запись номера такта i содержит 1 в j-м разряде.

При этом в начале каждого 1-го такта импульсом синхронизации в триггеры 12 и Э обеих групп триггеров записываются коды, хранящиеся в соответствующих ячейках памяти блоков 10 и 11 .В конце 1-го такта коды с инверсных выходов триггеров 12 и 13 переписываются в соответствующие ячейки блоков 10 и 11. Таким образом, если -и. О, то код в соответствующих ячейках сохраняется без изменения, если же v. 1 , то код в этих ячейках инвертируется. Понятно, что если при опросе некоторой ячейки блока 10 или 11 символ контролируемой последовательности единице четное число раз, то в этой ячейке сохраняется код, записанный в первом цикле работы (т.е. 1), если нечетное число раз - то код инвертируется (О), т.е. происходит определение четности числа векторов фиксированного вида (младших и старших байтов кода номера такта), на которые попадают единичные символы контролируемой последовательности.

Кроме того, в течение второго цикла триггер 8 определяет четность числа единиц для всей контролируемой последовательности.

С приходом импульса Стоп от объекта контроля триггер 7 устанавливается в 1, при этом закрывается элемент И 9, а сигналом от триггера 7 через нулевой канал мультиплексора 18 контроллер 29 информируется о завершении второго цикла работы. Кроме того, в контроллер через нулевой канал

0

5

0

5

0

5

0

5

0

мультиплексора 18 поступают сигналы от триггера 5, который устанавливается в 1, если длина контролируемой последовательности N; 2т, от тршгера 6 - для информации контроллера о зависании, если на анализатор не пришел сигнал Старт, от триггера 8 контроля четности числа единиц в последовательности.

Перед началом третьего цикла контроллер 29 подает сигнал О на вход элементов И 17, на D-вход триггера 6 и на вход элемента И 15. При этом блокируется запуск анализатора сигналом Старт и запись в блоки 10 и 11 памяти, а также разрывается связь между счетчиками 3 и 4.

Затем контроллер 29 устанавливает на управляющих входах мультиплексора 18 код 001, подготавливая к чтению через первый канал мультиплексора 1 8 из блоков 10 и 11 памяти соответствующих векторов младших четырех сигнатур (с первого ранга по четвертый), подает сигнал установки в О всех счетчиков и триггеров анализатора и формирует импульсы опроса ячеек блоков 10 и II памяти.

Далее на каждое состояние счетчиков 3 и 4 (которые работают синхронно) производится считывание содержимого опрашиваемых блоков памяти и, если считываемые биты равны О, то соответствующие вектора младших (старших) байтов соответствующей сигнатуры суммируются по модулю два с ранее полученной суммой векторов младших (старших) байтов. После опроса последних 2m -x ячеек блоков памяти первых четырех сигнатур, контроллер устанавливает на управляющих входах мультиплексора 18 код 010 для чтения из блоков 10 и 11 памяти через второй канал мультиплексора 18 соответствующих векторов для формиро- вания сигнатур ранга с пятого по восьмой и т.д.

Таким образом, получают все 16 сигнатур второго порядка. Сигнатура первого порядка образуется присвоением каждому разряду сигнатуры значения соответствующего разряда сигнатуры второго порядка соответствующего ранга.

Так, 16-й разряд сигнатуры первого порядка совпадает с 16-м разрядом сигнатуры второго порядка ранга 16Ч 15-й разряд сигнатуры первого порядка сов715

njflaer с 15-м-разрядом сигнатуры вто- poiо порядка ранга 15 и т.д.

Таким образом, для получения сигнатуры первого порядка и всех шестнадцати сигнатур второго порядка в предлагаемом анализаторе требуется всего один цикл контроля. Программная обработка не требует многократного

Понятно, что содержимое ячеек бл ков 10 и 11, адреса которых не указ /ны в таблице, не изменяется в проце

повторения запуска объекта испытаний, Q се формирования сигнатур, поскольку

что повышает достоверность контроля.

Выполнение счетчика номеров тактов в виде двух т/2-разрядных счетчиков позволяет в 2 2 раз уменьшить продолжительность цикла очистки и каждо- ° го цикла опроса блоков памяти, что дополнительно повышает быстродействие анализатора. Очевидно, что счетчик может быть выполнен и как четыре т/4- разрядных счетчика, при этом целесо- 2 образно использовать деление вектора номера такта соответственно на четыре части и блоки памяти с произвольной выборкой одного из 2 слов и т.п.2

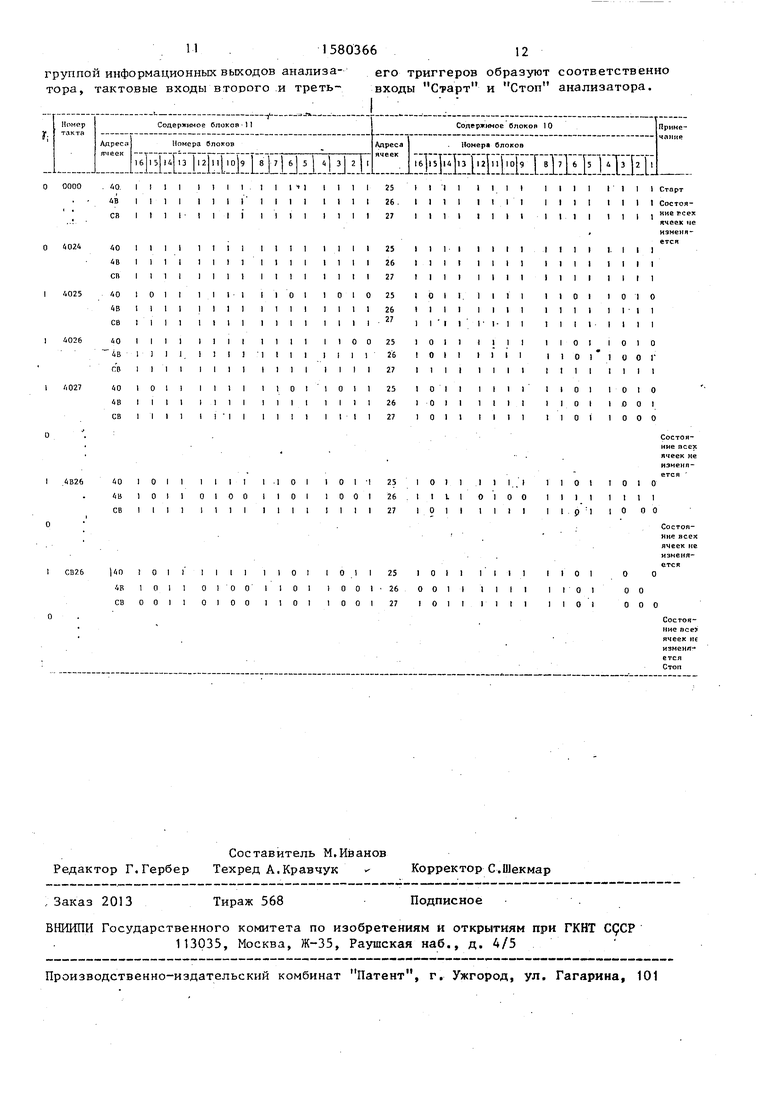

В таблице приведен пример формирования сигнатур второго порядка всех рангов для двоичной последовательности, символы которой -у| равны единице на тактах с номерами 4025Н, 4026Н, 3 4027Н, 4В26Н, СВ26Н (здесь и далее номера даны в шестнадцатиричном Н или двоичном В кодах), на остальных тактах т О,

В рассматриваемом примере (т 16) , старший и младший байты сигнатур формируются независимо, поэтому в таблице рассматриваются только те ячейки

блоков 10 и И, адреса которых совпа- (0010 0111)В (00100100) В |24Н.

дают соответственно со старшими и младшими байтами номеров тактов, на которых -у. О, а именно в блоках 10 (младший байт) - ячейки с адресами 25Н, 26Н и 27Н в блоках 11 (старший байт) - ячейки с адресами 40Н, 4ВН и СВН.

Как видно из таблицы, на нулевом такте (но Окончании цикла подготовки) содержимое всех ячеек блоков 10 и 11 равно единице. Пока у. О, т.е. по такт с номером 4024Н включительно состояние ячеек не изменяется. На такте номер 4025Н проинвертируется содержимое ячеек с адресом 40Н тех блоков I „ испытуемого устройства сигнатуры

и ячеек с адресом 25Н тех блоков 10, для которых соответствующие двоичные компоненты вектора номера такта не равны нулю, э. именно микросхемы 15,6,

сравнивают с полученными для заве исправного аналогичного устройств Если сигнатуры совпадают, делаетс вывод об отсутствии ошибок в конт

8

3 и 1. Аналогична, на такте номер 4026 проинвертируется содержимое ячеек с адресом аОН микросхем 15,6,3 и 2 блоков 1 и ячеек с адресом 25И микросхем 5,6,3 и 2 блоков 10 и т.д.

Понятно, что содержимое ячеек блсг- ков 10 и 11, адреса которых не указа- /ны в таблице, не изменяется в процес се формирования сигнатур, поскольку

в рассматриваемой последовательности не встречаются символы у.1 на так- тах, номера которых в старшем и младшем байтах отличаются от указанных в таблице.

| При считывании опрашиваются все /ячейки блоков 10 и 11 и суммируются по модулю два коды адресов тех ячеек соответствующих микросхем, в которых записан О. Так, например, для сигнатуры ранга 16 рассматриваются ячейки микросхем 16, в которые записан О : в блоке 1 1 - в ячейке с адресом СВН, следовательно, старший байт сигнатуры равен СВН; в блоке 10 - в ячейке с адресом 26Н, следовательно, младший байт сигнатуры равен 26Н.

Для сигнатуры ранга 15 рассматриваются ячейки микросхем 15. В этих микросхемах 0м записан: в ячейках блока 11 с адресами 40Н, 4ВН и СВН, следовательно, старший байт сигнатуры (0100 0000)В©(0100 101 1)В® (1100 1011)В (1100 0000)В СОН.

В микросхеме 15 (блок 10) О записан в ячейках с адресами 25Н, 26Н и 27Н, поэтому младший байт сигнатур ры равен (0010 0101)В©(0010 0110)В©

,f5

В целом сигнатура ранга 15 равна S1 С024Н.

Опрашивая остальные микросхемы, аналогично получают сигнатуры второго порядкаг

S14 ООООН, S13 ООООН; Sn 8000H

I14

о 11

ООООН; S 8000Н, S3 8000Н; S8 « ООООН; S7 JOOOH; S6 C024H; S 5 ООООН; S4 - ООООН; S3 C024H; S 8000H; Sf 0002H. i

Сигнатура первого порядка

S C024H.

Полученные в процессе контроля

сравнивают с полученными для заведомо исправного аналогичного устройства. Если сигнатуры совпадают, делается вывод об отсутствии ошибок в контро

91

лируемых двоичных последовательностях и,следовательно, об исправности контролируемого объекта.

Предлагаемое устройство реализовано в виде модуля программоуправляемо го сигнатурного анализатора и входит в состав автоматизированной системы контроля и диагностики. Модуль выполнен в интерфейсе микроэвм Электроника-60 и содержит около 80 микросхем серий К555, К155 и К531. При реализации анализатора с подобными же характеристиками с использованием принципа, на основе которого выполнено известное устройство, потребуется свыше 200 микросхем.

Объем программ формирования сигнатур, включая управление анализатором на всех циклах работы, составляет около 300 команд на языке ассемблера

микроЭВМ Электроника-60, время отработки программы - около 15 мс, собственно цикл сбора информации об объекте контроля равен N/f, где N - длин контролируемой последовательности, f - тактовая частота работы объекта (f 1 О МГц) .

Формула из .обретен и я

Сигнатурный анализатор, содержащий два счетчика, первый триггер, первую группу триггеров, первую группу элементов И и мультиплексор, входы сброса 35 счетчика и первого триггера объединены и образуют вход сброса анализатора, первые входы элементов И первой группы объединены и образуют информаров первой п второй групп, третьи входы элементов II первой группы, пе вый вход первого элемента ИЛИ и так товый вход четвертого триггера объе динены v подключены к выходу второг элемента И, первый вход которого со динен с D-входом третьего триггера подключен к выходу второго триггера второй вход второго элемента И соед нен с инверсным выходом третьего тр гера, третий вход второго элемента является тактовым входом анализатор второй вход первого элемента ИЛИ со динен с первым входом второго элеме та ИЛИ, с первыми входами элементов И второй группы и образует вход зап си-считывания анализатора, вторые вх ды элементов И второй группы объеди нены и образуют вход задания режима анализатора, вькоды 1-х элементов И первой и второй групп соединены с вх дами 1-х элементов ИЛИ группы, выхо которых соединены с входами записи 1-х блоков памяти первой и второй , групп, где ,m, , входы сброс триггеров первой и второй групп, вх ды сброса второго, третьего и четве того триггеров объединены и подключ ны к входу сброса анализатора, инфо мационные входы с первого по четвер тый первой группы мультиплексора со динены с выходами первого, второго, третьего и четвертого триггеров, вы ход переполнения первого счетчика соединен с первым входом первого эл мента И, второй вход которого соеди нен с D-входом второго триггера и о разует вход разрешения анализатора, выход первого элемента SI соединен с

ционный вход анализатора, вторые вхо-40 вторым входом второго элемента ИЛИ,

ды j-x элементов И первой группы подключены к выходам j-x разрядов первого счетчика, где j I,n, n - разрядность первого и второго счетчиков, отличающийся -.ем, что, с целью увеличения быстродействия и повышения достоверности контроля, он I содержит группу элементов ИЛИ, двз

элемента ИЛИ, два элемента И, вторую группу элементов И, вторую группу триггеров, второй, третий и четвертый триггеры, две группы блоков памяти, причем вторые входы (j+n)-x элементов И первой группы соединены с j-ми выходами второго счетчика, группа уп равляющих входов мультиплексора образует группу входов задания режима анализатора, тактовые входы тригге45

50

,- 55

выходы первого и второго элементов ИЛИ соединены с тактовыми входами с ответственно первого и второго счет чиков, выход переполнения второго счетчика соединен с тактовым входом первого триггера , разрядные выходы первого и второго счетчиков соедине ны с адресными входами блоков памяти соответственно первой и второй групп информационные выхбды и входы 1-х бл ков памяти первой и второй групп сое динены с D-входами и инверсными выхо дами 1-х триггеров соответственно пе вой и второй групп, информационные входы второй группы мультиплексора соединены с выходами соответствующих блоков памяти первой и второй групп, группа выходов мультиплексора являетс

10

10

0

5

0

5

ров первой п второй групп, третьи входы элементов II первой группы, первый вход первого элемента ИЛИ и тактовый вход четвертого триггера объединены v подключены к выходу второго элемента И, первый вход которого соединен с D-входом третьего триггера и подключен к выходу второго триггера, второй вход второго элемента И соединен с инверсным выходом третьего триггера, третий вход второго элемента И является тактовым входом анализатора, второй вход первого элемента ИЛИ соединен с первым входом второго элемен-. та ИЛИ, с первыми входами элементов И второй группы и образует вход записи-считывания анализатора, вторые входы элементов И второй группы объединены и образуют вход задания режима анализатора, вькоды 1-х элементов И первой и второй групп соединены с входами 1-х элементов ИЛИ группы, выходы которых соединены с входами записи 1-х блоков памяти первой и второй , групп, где ,m, , входы сброса триггеров первой и второй групп, входы сброса второго, третьего и четвертого триггеров объединены и подключены к входу сброса анализатора, информационные входы с первого по четвертый первой группы мультиплексора соединены с выходами первого, второго, третьего и четвертого триггеров, выход переполнения первого счетчика соединен с первым входом первого элемента И, второй вход которого соединен с D-входом второго триггера и образует вход разрешения анализатора, выход первого элемента SI соединен с

0 вторым входом второго элемента ИЛИ,

45

0

5

выходы первого и второго элементов ИЛИ соединены с тактовыми входами соответственно первого и второго счетчиков, выход переполнения второго счетчика соединен с тактовым входом первого триггера , разрядные выходы первого и второго счетчиков соединены с адресными входами блоков памяти соответственно первой и второй групп, информационные выхбды и входы 1-х блоков памяти первой и второй групп соединены с D-входами и инверсными выходами 1-х триггеров соответственно первой и второй групп, информационные входы второй группы мультиплексора соединены с выходами соответствующих блоков памяти первой и второй групп, группа выходов мультиплексора является

И1580366

группой информационных выходов анализатора, тактовые входы второго и третьСоставитель М.Иванов Редактор Г.Гербер Техред А.Кравчук Корректор С.Шекмар

Заказ 2013

Тираж 568

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

12

его триггеров образуют соответственно входы Старт и Стоп анализатора.

Подписное

| Сигнатурный анализатор | 1981 |

|

SU962962A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сигнатурный анализатор | 1984 |

|

SU1193680A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-02-02—Подача