вый и второй входы второго элемента И-НЕ, второй вход первого элемента И-НЕ и второй вход третьего элемента И являются соответственно входами с четвертого по седьмой блока, входами которого с восьмого по одиннадцатый являются соответственно входы с первого по четвертый четвертого элемента И, выходы первого, третье го и второго элементов И, первого элемента И-НЕ и четвертого элемента И являются соответственно выходами с первого по пятый блока, трети вход второго элемента И подключен к выходу второго элемента И-НЕ.

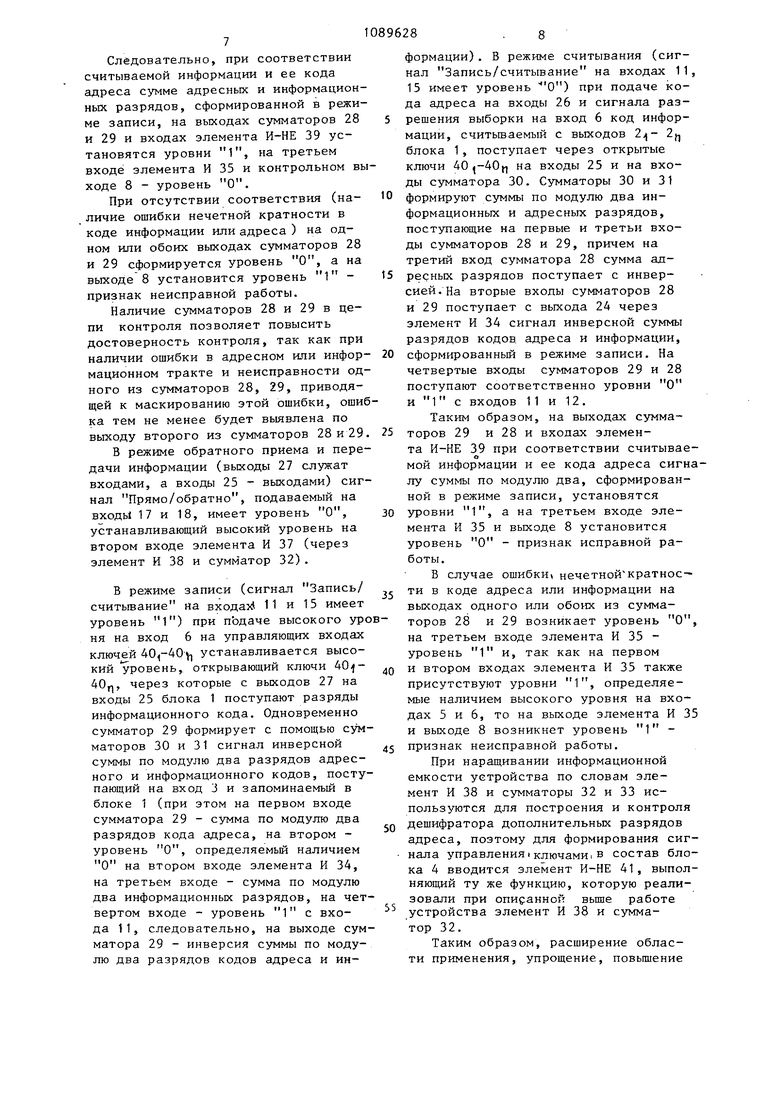

3. Устройство по п. 2, отличающееся тем, что логический блок содержит третий элемент Ивькод которого подключен к второму входу третьего элемента И, первый вход соединен с вторым входом первого элемента И, а второй вход является седьмым входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство с самоконтролем | 1984 |

|

SU1274005A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1989 |

|

SU1633497A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с контролем | 1988 |

|

SU1508287A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля хода микропрограмм | 1987 |

|

SU1430959A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1520599A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| ИМПУЛЬСНЫЙ КОДОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2248607C1 |

1. ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ, УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК, содержащее блок памяти и сумматоры по модулю два с первого по шестой, , причем первые входи первого и. второго сумматоровПО модулю два соединены соответственно с выходами третьего и четвертого сумматоров по модулю два, входы которых подключены соответственно к информационным выходам и к адресным входам блока памяти, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности передачи информации в двух направлениях, повышения достоверности контроля и упрощения устройства, в него введены ключи, логический блок и элемент НЕ, причем первый выход логического блока соединен с вторыми входами первого и второго сумматоров по модулю два, третий вход первого и выход четвертого сумматоров по модулю два подключены соответственно к вькоду и к входу элемента НЕ, первый, второй и третий входы логического блока соединены соответственно с контрольным выходом и соуправляющими входами блока памяти, четвертый вход логического блока и контрольный вход блока памяти подключены к выходу второго сумматора по модулю два, пятый и шестой входы логического блока подключены соответственно к выходу первого сумматора по модулю два и к выходу третьего и третьему входу второго сумматоров по модулю два, второй выход логического блока соединен с управляющими входами ключей, входы которыхподключены к информационным входам блока памяти, а выходы соединены с информационными выходами блока памяти и являются информационными выходами устройства, управляющие входы блока памяти и седьмой вход логического блока являются управляющими входами устройства-, а третий и четвертый выходы логического блока - контрольными выходами устройства, входы с восьмого по одиннадцатый логического блока, четвертые входы первого и второго сумматоров по модулю два, первые и вторые входы пятого и шестого сумматоров по модулю два являются входами коммутации устройства, выходами коммутации которого являются пятый выход логического блока и выходы пятого и шестого сумматоров по модулю два. 2. Устройство по п. 1, отличающееся тем, что логический блок содержит элементы И и элементы И-НЕ, причем первый вход первого элемента И является первым входом блока, первые входы второго и третьего элементов И и первого элеме.н,та И-НЕ объединены и являются вторь входом блока, вторые входы первого и второго элементов И объединены и являются третьим входом блока, пер

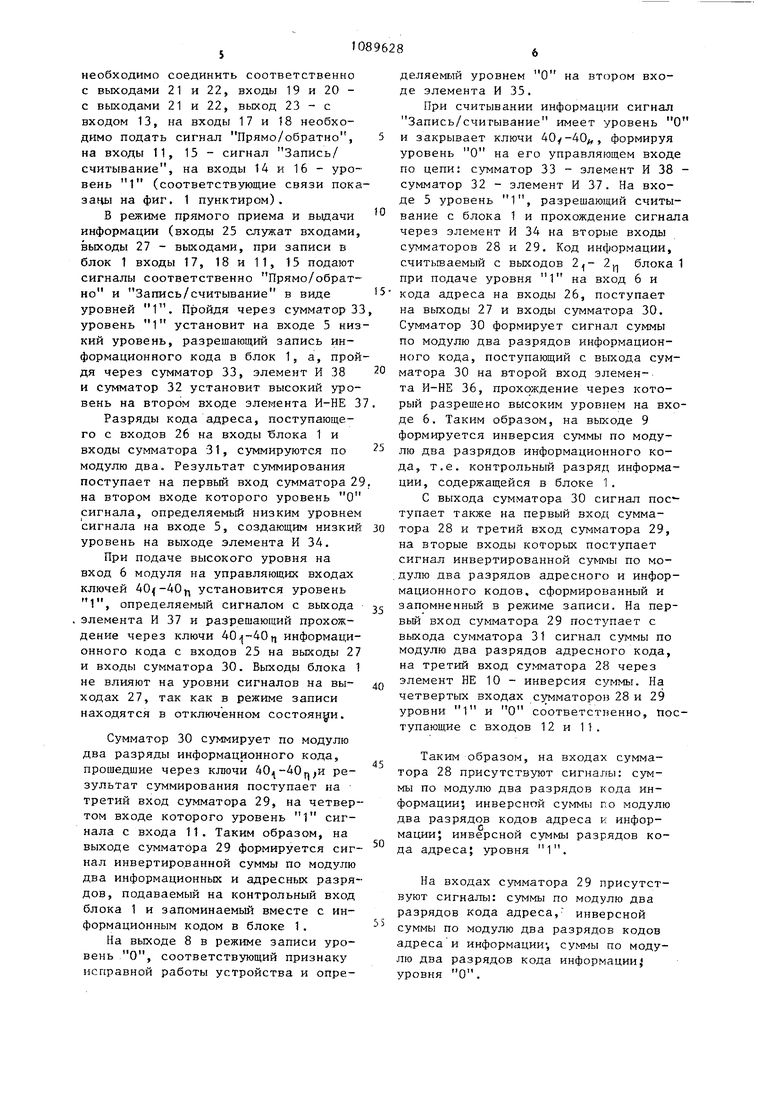

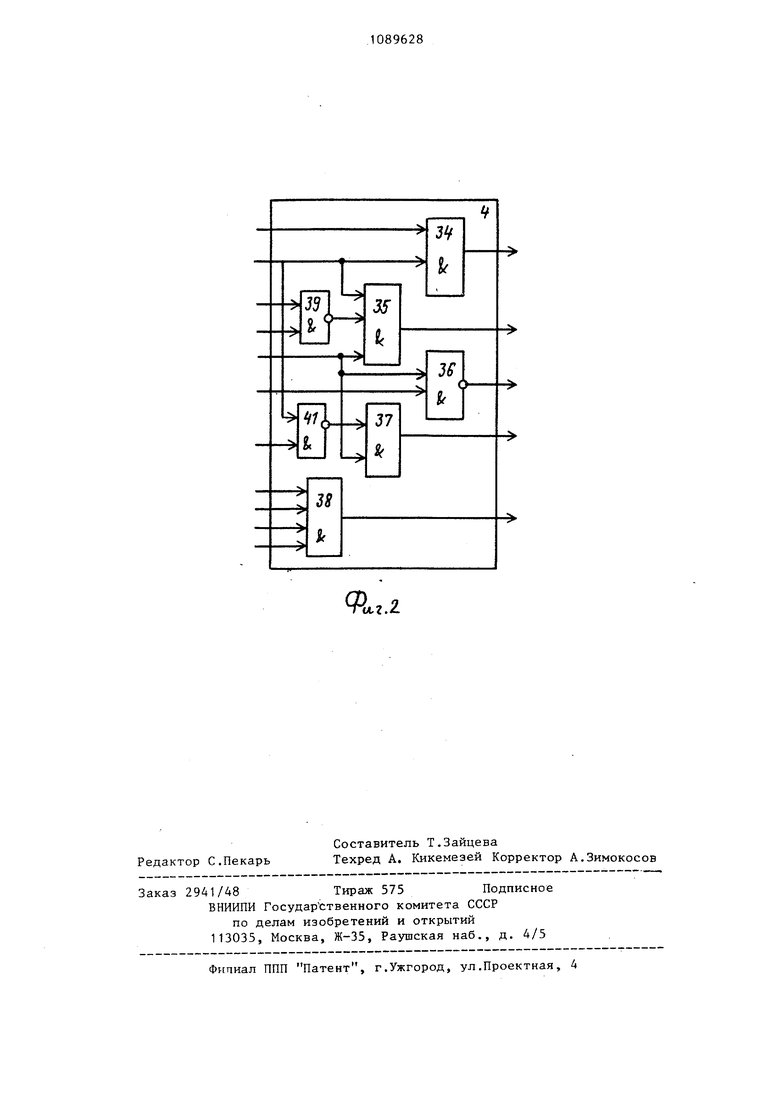

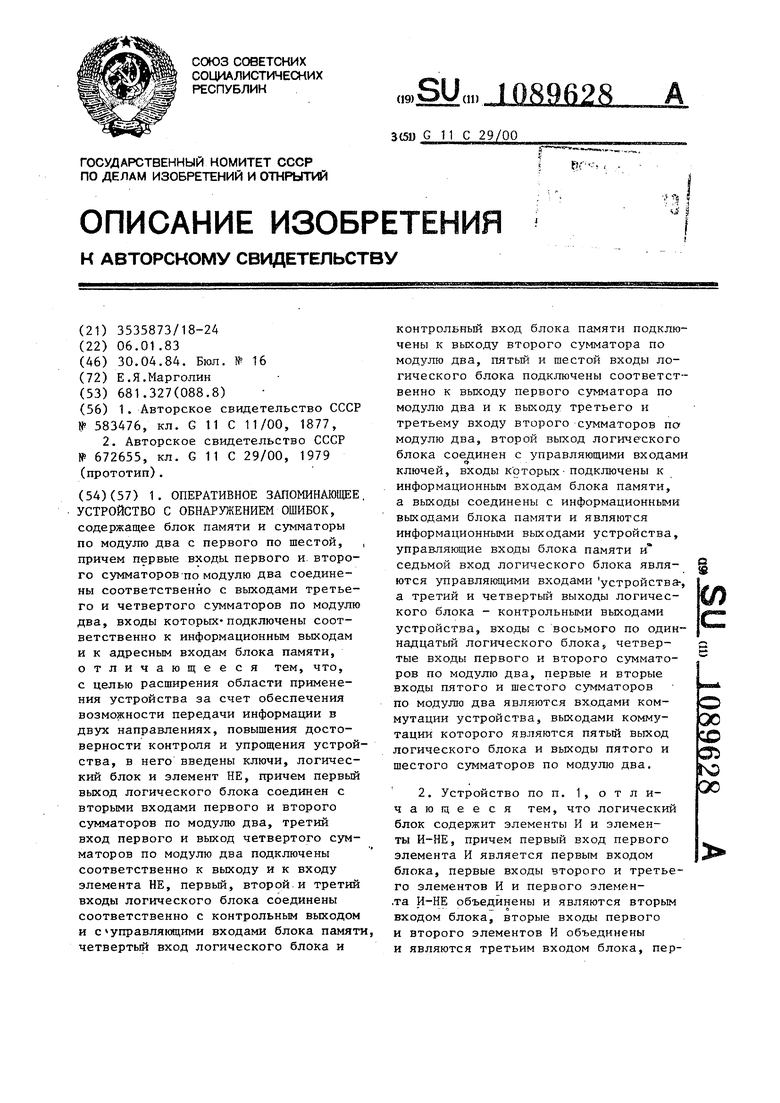

Изобретение относится к вычислительной технике и может быть использовано при построении оперативных запоминающих устройств (ОЗУ) с контролем. Известно оперативное, запоминающее устройство с обнаружением ошибок содержащее накопитель, элементы И или ИЛИ, входную и выходную группы элементов И, содержащее по два элемента И на разряд накопителя, а также блоки формирования адресов записи и считывания и блок сравнения . Недостатки известного устройствасложность, возникающая из-за больщого количества элементов И., и отсутствие возможности обнаружения ошибок как в адресном, так и в информационном тракте. Наиболее близким техническим решением к изобретению является оперативное запоминающее устройство с обнаружением ошибок, содержащее нако питель, входной, вьЕХодной и адресный регистры, четыре блока сверток по мо дулю два и сумматорыпо модулю два, счетчики и вычитатель, блок синхронизации, выходы которого подключены к управляющим входам счетчиков, соединенных с выходами сумматоров по мо дулю два, причем входы первого и вто рого сумматоров по модулю два подклю чены соответственно к информационным выходам и к адресным входам накопителя 2 . Недостатками известного устройства являются невозможность передачи информации в прямом и обратном напра лениях контроля информации при передаче ее от выхода к входу формирования контрольного разряда, необходимого для контроля информации в последующих каскадах обработки и построения дополнительных блоков, необходимьк при модульном наращивании информационной емкости по числу слоев и разрядов, что ограничивает область применения устройства, низкая достоверность контроля, поскольку контрольный сигнал формируется только после считывания всей информации из накопителя и не обеспечивается контроль дополнительного оборудования-, необходимого при наращивании информационной емкости, а также сложность устройства. Цель изобретения - расширение области применения устройства за счет обеспечения возможности передачи информации в двух направлениях, поБ1 Щ1ение достоверности контроля и упрощение устройства Поставленная цель достигается тем, что в оперативное запоминающее устройство с обнаружением ошибок, содержащее блок памяти и сумматоры по модулю два с первого по шестой, причем первые входы первого и второго сумматоров по модулю два соединены соответственно с вьгходами третьего и четвертого сумматоров по модулю два, входы которых подключены соответственно к информационным выходам и к адресным входам блока памяти, введены ключи, логический блок и элемент НЕ, причем первый выход логического блока соединен с вторыми входами первого и второго сумматоров по модулю два, третий вход первого и выход четвертого сумматоров по модулю два подключен соответственно к вы ходу и к входу элемента НЕ, первый второй и третий входы логического блока соединены соответственно с контрольным выходом и с управляющими входами блока памяти четвертый вход логического блока и контрольный вход блока памяти подключены к выходу второго сумматора по модулю два, пятый и шестой входы логического блока подключены соответственно к выходу первого сумматора по модулю два и к выходу третьего и третьему входу второго сумматоров по модулю два, второй выход логического блока соединен с управляющими входами ключей входы которых подключены к информационным входам блока памяти, а выходы соединены с информационными выходами блока памяти и являются инфор мационными выходами устройства, управляющие входы блока памяти и седьмой вход логического блока являются управляющими входами устройства, а третий и четвертый выходы логического блока - контрольными выходами устройства, входы с восьмого по одиннадцатый логиче ского блока,четвертые входы первого и вт орого сумматоров по модулю два, первые и вторые входы пятого и шестого сумматоров по модулю два являются входами коммутации устройства, выходами ком мутации которого являются пятый выход логического блока и выходы пято го и шестого сумматоров по модулю два. Логический блок содержит элементы И и элементы И-НЕ, причем первый вход первого элемента И являетс первым входом блока, первые входы второго.и третьего элементов И и пе вого элемента И-НЕ объединены и являются вторым входом блока, вторые входы первого и второго элементов И объединены и являются третьим входо блока, первый и второй входы второг элемента И-НЕ, второй вход первого элемента И-НЕ и второй вход третьего элемента И являются соответствен но входами с четвертого по седьмой блока, входами которого с восьмого по одиннадцатый являются соответственно входы с первого по четвертый четвертого элемента И, выходы перво ГО, третьего и второго элементов И, первого элемента И-НЕ и четвертого элемента И являются соответственно выходами с первого по пятый блока, третий вход второго элемента И подключен к выходу второго элемента ИНЕ. Логический блок содержит третий элемент И-НЕ, выход которого подключен к второму входу третьего элемента И, первый вход соединен с вторым входом первого элемента И, а второй вход является седьмым входом блока. На фиг. 1 представлена функциональная схема предлагаемого устройства/ на фиг. 2 - функциональная схема ВТОГО варианта выполнения логического блока. Устройство содержит (фиг. 1) блок 1 памяти с информационными выходами 2t) (где П - целое число) и контрольным входом 3, логический блок 4. На фиг. 1 обозначены управляющие входы 5-7 с первого по третий, контрольные выходы 8, 9 устройства, элемент НЕ 10, входы 11-20 коммутации, выходы 21-23 коммутации устройства, контрольный выход 24 блока памяти, информационные 25 и адресные 26 входы и информационные выходы 27 устройства. Устройство содержит также сумматоры 28-33 по модулю два с первого по шестой. Логический блок содержит (см. фиг. 1) nepBbDi 34 и второй 35 элементы И, первьй элемент И-НЕ 36, третий 37 и четвертый 38 элементы И и второй элемент И-НЕ 39. Устройство содержит также ключи 40(-40г) . Во втором варианте выполнения логический блок содержит также (см. фиг. 2) третий элемент И-НЕ 41. Устройство работает следующим образом. В том случае, когда отсутствует необходимость в наращивании информационной емкости устройства, сумматоры 32 и 33 (см. фиг. 1) используются для инвертирования и формирования сигнала управления ключами совместно с элементом И 38, и для обеспечения необходимой полярности сигналов на выходах сумматоров 28 и 29 в режимах записи и считьшания используется сумматор 33. В соответствии с этим входы 5 и 7 необходимо соединить соответственно с выходами 21 и 22, входы 19 и 20 с выходами 21 и 22, выход 23 - с входом 13, на входы 17 и 18 необходимо подать сигнал Прямо/обратно, на входы 11, 15 - сигнал Запись/ считывание, на входы 14 и 16 - уровень 1 (соответствующие связи пока заны на фиг. 1 пунктиром). В режиме прямого приема и выдачи информации (входы 25 служат входами, выходы 27 - выходами, при записи в блок 1 входы 17, 18 и 11, 15 подают сигналы соответственно Прямо/обратно и Запись/считывание в виде уровней 1. Пройдя через сумматор 3 уровень 1 установит на входе 5 низ кий уровень, разрешающий запись информационного кода в блок 1, а, прой дя через сумматор 33, элемент И 38 и сумматор 32 установит высокий уровень на втором входе элемента И-НЕ 3 Разряды кода адреса, поступающего с входов 26 на входы Ълока 1 и входы сумматора 31, суммируются по модулю два. Результат суммирования поступает на первый вход сумматора 2 на втором входе которого уровень О сигнала, определяемый низким уровнем сигнала на входе 5, создающим низкий уровень на выходе элемента И 34, При подаче высокого уровня на вход 6 модуля на управляющих входах ключей 40(-40|, установится уровень 1, определяемый сигналом с выхода , элемента И 37 и разрешающий прохождение через ключи 40,|-40ц информационного кода с входов 25 на выходы 2 и входы сумматора 30, Выходы блока не влияют на уровни сигналов на выходах 27, так как в режиме записи находятся в отключенном состоянии. Сумматор 30 суммирует по модулю два разряды информационного кода, прошедшие через ключи результат суммирования поступает на третий вход сумматора 29, на четвер том входе которого уровень 1 сигнала с входа 11, Таким образом, на выходе сумматора 29 формируется сиг нал инвертированной суммы по модулю два информационных и адресных разря дов, подаваемый на контрольный вход блока 1 и запоминаемый вместе с информационным кодом в блоке 1. На выходе 8 в режиме записи уровень О, соответствующий признаку исправной работы устройства и опре1деляемыи уровнем на втором входе элемента И 35. При считывании информации сигнал Запись/считывание имеет уровень О и закрывает ключи 40у-40,, формируя уровень О на его управляющем входе по цепи: сумматор 33 - элемент И 38 сумматор 32 - элемент И 37. На входе 5 уровень 1, разрешающий считывание с блока 1 и прохождение сигнала через элемент И 34 на вторые входы сумматоров 28 и 29. Код информации. считьЕваемый с вькодов 2 блока 1 при подаче уровня 1 на вход 6 и кода адреса на входы 26, поступает на выходы 27 и входы сумматора 30, Сумматор 30 формирует сигнал суммы по модулю два разрядов информационного кода, поступающий с выхода сумматора 30 на второй вход элемента И-НЕ 36, прохождение через который разрешено высоким уровнем на входе 6. Таким образом, на выходе 9 формируется инверсия суммы по модулю два разрядов информационного кода, т.е. контрольный разряд информации, содержащейся в блоке 1. С выхода сумматора 30 сигнал поступает также на первый вход сумматора 28 и третий вход сумматора 29, на вторые входы которых поступает сигнал инвертированной суммы по модулю два разрядов адресного и информационного кодов, сформированный и запомненный в режиме записи. На первьй вход сумматора 29 поступает с выхода сумматора 31 сигнал суммы по модулю два разрядов адресного кода, на третий вход сумматора 28 через элемент НЕ 10 - инверсия суммы. На четвертых входах сумматоров 28 и 29 уровни 1 и О соответственно, поступающие с входов 12 и 11. Таким образом, на входах сумматора 28 присутствуют сигналы: суммы по модулю два разрядов кода информации; инверсной суммы по модулю два разрядов кодов адреса и информации; инверсной суммы разрядов кода адреса; уровня 1. На входах сумматора 29 присутствуют сигналы: суммы по модулю два разрядов кода адреса, инверсной суммы по модулю два разрядов кодов адресаи информации-, суммы по модулю два разрядов кода информацииj уровня О. Следовательно, при соответствии считываемой информации и ее кода адреса сумме адресных и информацион ных разрядов, сформированной в режи ме записи, на выходах сумматоров 28 и 29 и входах элемента И-НЕ 39 установятся уровни 1, на третьем входе элемента И 35 и контрольном в ходе 8 - уровень О. При отсутствии соответствия (наличие ошибки нечетной кратности в коде информации или адреса ) на одном или обоих выходах сумматоров 28 и 29 сформируется уровень О, а на выходе 8 установится уровень 1 признак неисправной работы. Наличие сумматоров 28 и 29 в цепи контроля позволяет повысить достоверность контроля, так как при наличии ошибки в адресном или инфор мационном тракте и неисправности од ного из сумматоров 28, 29, приводящей к маскированию этой ошибки, оши ка тем не менее будет вьивлена по выходу второго из сумматоров 28 и 29 В режиме обратного приема и пере дачи информации (выходы 27 служат входами, а входы 25 - выходами) сиг нал Прямо/обратно, подаваемый на входь 17 и 18, имеет уровень О, устанавливающий высокий уровень на втором входе элемента И 37 (через элемент И 38 и сумматор 32). В режиме записи (сигнал Запись/ считьгоание на входа 4 11 и 15 имеет уровень 1) при подаче высокого ур ня на вход 6 на управляющих входах ключей 40,-40у, устанавливается высокий ypoBeHb, открывающий ключи , через которые с выходов 27 на входы 25 блока 1 поступают разряды информационного кода. Одновременно сумматор 29 формирует с помощью сум маторов 30 и 31 сигнал инверсной суммы по модулю два разрядов адресного и информационного кодов, посту пающий на вход 3 и запоминаемый в блоке 1 (при этом на первом входе сумматора 29 - сумма по модулю два разрядов кода адреса, на втором уровень О, определяемый наличием О на втором входе элемента И 34, на третьем входе - сумма по модулю два информационных разрядов, на чет вертом входе - уровень 1 с входа 11, следовательно, на выходе сум матора 29 - инверсия суммы по модулю два разрядов кодов адреса и информации). В режиме считывания (сигнал Запись/считывание на входах 11, 15 имеет уровень О) при подаче кода адреса на входы 26 и сигнала разрешения выборки на вход 6 код информации, считьюаемый с выходов 2 блока 1, поступает через открытые ключи 40 -40fj на входы 25 и на входы сумматора 30. Сумматоры 30 и 31 формируют суммы по модулю два информационных и адресных разрядов, поступающие на первые и третьи входы сумматоров 28 и 29, причем на третий вход сумматора 28 сумма адресных разрядов поступает с инверсией. На вторые входы сумматоров 28 и 29 поступает с выхода 24 через элемент И 34 сигнал инверсной суммы разрядов кодов адреса и информации, сформированный в режиме записи. На четвертые входы сумматоров 29 и 28 поступают соответственно уровни О и 1 с входов 11 и 12. Таким образом, на выходах сумматоров 29 и 28 и входах элемента И-НЕ 39 при соответствии считываемой информации и ее кода адреса сигналу суммы по модулю два, сформированной в режиме записи, установятся уровни 1, а на третьем входе элемента И 35 и выходе 8 установится уровень О - признак исправной работы. В случае ошибки, нечетнойкратнос- ти в коде адреса или информации на выходах одного или обоих из сумматоров 28 и 29 возникает уровень О, на третьем входе элемента И 35 уровень 1 и, так как на первом и втором входах элемента И 35 также присутствуют уровни 1, определяемые наличием высокого уровня на входах 5 и 6, то на выходе элемента И 35 и выходе 8 возникнет уровень 1 признак неисправной работы. При наращивании информационной емкости устройства по словам элемент И 38 и сумматоры 32 и 33 используются для построения и контроля дешифратора дополнительных разрядов адреса, поэтому для формирования сигнала управления ключами в состав блока 4 вводится элемент И-НЕ 41, выполняющий ту же функцию, которую реализовали при описанной вьш:е работе устройства элемент И 38 и сумматор 32. Таким образом, расширение области применения, упрощение, повышение

оперативности и достоверности контроля достигается за счет того, что формирование и запоминание контрольного разряда кодов адреса и информации производится с использованием отключенного состояния выходов , блока 1 в режиме записи на том же I оборудовании, на котором осуществляется и выработка сигнала, характеризующего исправность устройства и двунаправленная передача и хранение информации, причем при увеличении информационной емкости наращивание контрольного оборудования происходит без дополнительных аппаратурных затрат.

и.1

.4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Буферное запоминающее устройство | 1976 |

|

SU583476A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с обнаружением ошибок | 1977 |

|

SU672655A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-04-30—Публикация

1983-01-06—Подача