1

Изобретение относится к радиотехнике и может использоваться в системах фазовой автоподстройки частоты для слежения за фазой колебания. Цель изобретения уменьшение зо- щ,1 нечувствительности при одновременном уменьшении импульсных помех в выходном сигнале.

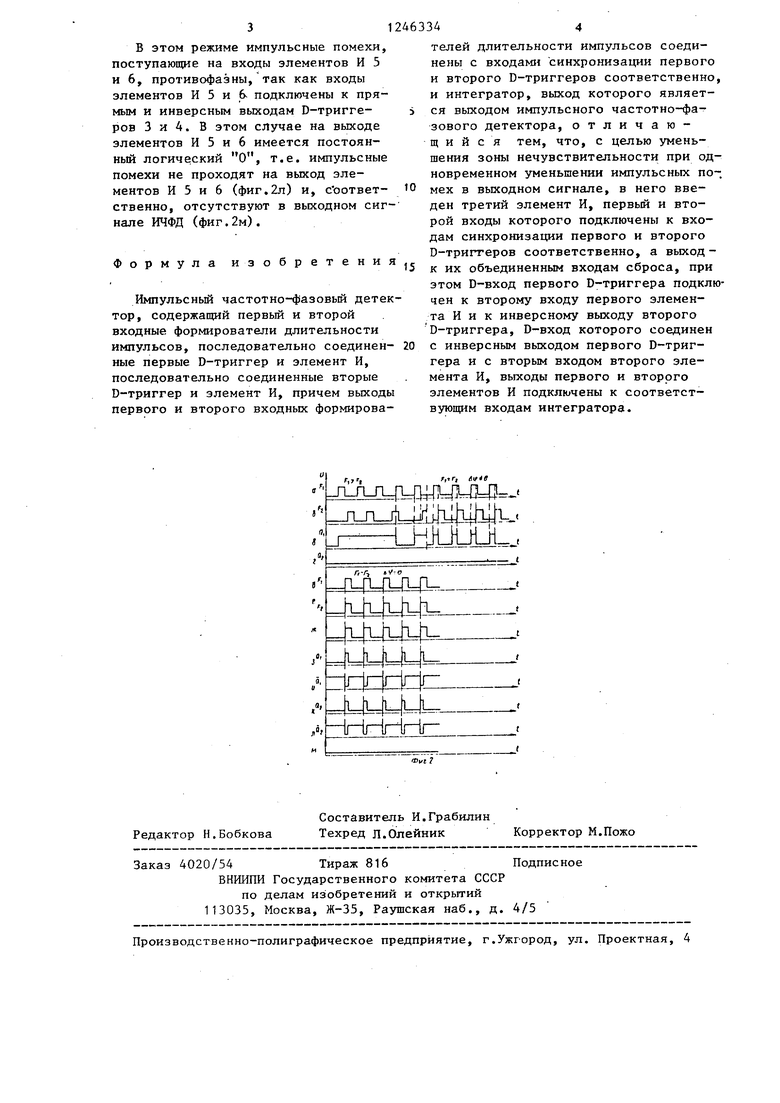

На фиг.1 приведена структурная электрическая схема предлагаемого импульсного частотно-фазового-детектора; на фиг.2 - диаграммы,, поясняющие его работу.

Импульсный частотно-фазовый детектор (ИЧФД) содержит первый и второй входные формирователи 1 и 2 длительности импульсов, первый и второй D-триггеры 3 и 4, первый 5, второй 6, третий 7 элементы И и интегратор 8.

ИЧФД работает следующим образом. На первый вход ИЧФД поступает аналоговый сигнал с частотой F , а на второй вход - с частотой F,j, причем F, р2. После формирователей 1 и 2 имеются соответственно две импульсные последовательности частотой F, (фиг.2а) и частотой F (фиг.2б). В исходном положении на выходах D- триггеров 3 и 4 уровни напряжения на прямых выходах соответствуют логическому О, тогда первый же импульс, поступающий с формирователя 1 им- .пульсов, переключит D-триггер 3 в

ТГёрвый же импульс на входе D-три гера 3 после сброса переключает D- триггер 3 в единичное состояние.Цик повторяется. Ввиду симметричности схемы при F, Fj ИЧФД работает аналогичным образом, только соответственно D-триггер 4 переключается теперь в единичное состояние, а D-три гер 3 удерживается в нулевом состоя нии.

10

t5

20

25

30

Таким образом, при неравенстве частот на выходе одного из D-тригг ров постоянно имеется логический |на выходе другого - информационный сигнал с частотной расстройкой. Эт информационный сигнал проходит чер элементы И 5 и 6 на интегратор 8 и далее на выход ИЧФД.

В сл;учае равенства частот (фиг. б) 5 т„е. при F F , когда и

, где Г- длительность им пульса на вьпсоде входных формиров телей 1 и 2, Т - период следования

импульсов Т -, на одном из выход

D-триггеров (в данном случае на вы ходе. D-триггера 3) формируется импульсная последовательность, пропо циональная разности фаз входных им пульсньп последовательностей (фиг. а на выходе другого D-триггера име ется постоянный логический О. Пр

единичное состояние (фиг.2в), в кото- 35 2ff; й в случае равенства частот

ром он находится до момента совпадения импульсов на входах элемента И 7, а Б-триггер 4 постоянно находится в нулевом состоянии (фиг.2г), так как на Б входе D-триггера 4 в момент прихода входных импульсов имеется постоянный логический О.

В момент совпадения импульсов на входах элемента И 7 на его выходе формируется импульс сброса, который устанавливает D -триггеры 3 и 4 в ну. левое состояние, т.е. формирование импульса сброса осуществляется без участия D-триггеров 3 и 4, которые в этом случае не вносят задержку в цепь формирования импульса сброса, позволяя тем самьм осуществлять работу ИЧФД на более высоких частотах. Таким образом, исключение времени задержки D-триггеров 3 и 4 при формировании импульса сброса приводит к увеличению быстродействия ИЧФД.

F,. F,

40

45

50

35

на выходе ИЧФД формируется но из двух э кстремальных значений выходного напряжения в зависимости от знака фазового рассогласования. Изменяя длительность импульсов, по cтyпaющ tx с выхода входных формиро вател:ей 1 и 2, можно получать нео§ димый; раствор дискриминационной ха рактеристики ИЧФД.

В сл5 чае F F при нулевом сдвиге фаз йч О (фиг.2д5 е) D-три геры 3 и 4 одновременно начинают п реключаться в единичное состояние (фиг.2з,к), но на выходе элемента И 7 одновременно формируются импул сы сброса (фиг.2ж), которые сбрасы вают D-триггеры 3 и 4 в нулевое со тояние. Таким образом при F F и &ч о на вь0содах D-триггеров 3 4 одновременно формируются узкие импульсы, которые в данном случае при Fj Fj и йЧ О являются им- пульсв ЧИ помехи.

.

463342

ТГёрвый же импульс на входе D-триг- гера 3 после сброса переключает D- триггер 3 в единичное состояние.Цикл повторяется. Ввиду симметричности схемы при F, Fj ИЧФД работает аналогичным образом, только соответственно D-триггер 4 переключается теперь в единичное состояние, а D-триггер 3 удерживается в нулевом состоянии.

10

Таким образом, при неравенстве частот на выходе одного из D-тригге- ров постоянно имеется логический О, |на выходе другого - информационный сигнал с частотной расстройкой. Этот информационный сигнал проходит через элементы И 5 и 6 на интегратор 8 и далее на выход ИЧФД.

В сл;учае равенства частот (фиг.2а, б) 5 т„е. при F F , когда и

, где Г- длительность импульса на вьпсоде входных формирователей 1 и 2, Т - период следования

импульсов Т -, на одном из выходов

D-триггеров (в данном случае на выходе. D-триггера 3) формируется импульсная последовательность, пропорциональная разности фаз входных им- пульсньп последовательностей (фиг.2в), а на выходе другого D-триггера имеется постоянный логический О. При

F,. F,

на выходе ИЧФД формируется одно из двух э кстремальных значений выходного напряжения в зависимости от знака фазового рассогласования. Изменяя длительность импульсов, по- cтyпaющ tx с выхода входных формиро- вател:ей 1 и 2, можно получать нео§ко- димый; раствор дискриминационной характеристики ИЧФД.

В сл5 чае F F при нулевом сдвиге фаз йч О (фиг.2д5 е) D-триггеры 3 и 4 одновременно начинают переключаться в единичное состояние (фиг.2з,к), но на выходе элемента И 7 одновременно формируются импульсы сброса (фиг.2ж), которые сбрасывают D-триггеры 3 и 4 в нулевое состояние. Таким образом при F F и &ч о на вь0содах D-триггеров 3 и 4 одновременно формируются узкие импульсы, которые в данном случае при Fj Fj и йЧ О являются им- пульсв ЧИ помехи.

В этом режиме импульсные помехи, поступающие на входы элементов И 5 и 6, противофазны, так как входы элементов И 5 и 6- подключены к прямым и инверсным выходам D-тригге- ров 3 и А. В этом случае на выходе элементов И 5 и 6 имеется постоянный логический О, т.е. импульсные помехи не проходят на выход элементов И 5 и 6 (фиг,2л) и, с оответ- ственно, отсутствуют в выходном сигнале ИЧФД (фиг.2м).

Формула изобретения

Импульсный частотно-фазовый детектор, содержащий первый и второй входные формирователи длительности импульсов, последовательно соединенные первые D-триггер и элемент И, последовательно соединенные вторые D-триггер и элемент И, причем выходы первого и второго входных формироваРедактор Н.Бобкова

Составитель И.Грабилин Техред Л.Олейник

Заказ 4020/54Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

телей длительности импульсов соединены с входами синхронизации первого и второго D-триггеров соответственно, и интегратор, выход которого являет- ся выходом импульсного частотно-фазового детектора, отличающийся тем, что, с целью уменьшения зоны нечувствительности при одновременном уменьшении импульсных по-.

мех в выходном сигнале, в него введен третий элемент И, первый и второй входы которого подключены к входам синхронизации первого и второго D-тригтеров соответственно, а выход к их объединенным входам сброса, при этом D-вход первого D-триггера подключен к второму входу первого элемента И и к инверсному выходу второго D-триггера, D-вход которого соединен

с инверсным выходом первого D-триггера и с вторым входом второго элемента И, выходы первого и второго элементов И подключены к соответствующим входам интегратора.

Корректор М.Пожо

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1285558A1 |

| Цифровой частотно-фазовый компаратор | 1985 |

|

SU1248025A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Импульсный частотно-фазовый детектор | 1985 |

|

SU1312718A1 |

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

| Формирователь разностной частоты импульсных последовательностей | 1984 |

|

SU1265985A1 |

| Преобразователь последовательности импульсов в прямоугольный импульс | 1987 |

|

SU1499457A1 |

Изобретение относится к радиотехнике. Цель изобретения - уменьшение зоны нечувствительности при одновременном уменьшении импульсных помех в выходном сигналеЧ Устройство содержит два входных формирователя длительности импульсов 1 и 2, два D-триггера 3 и 4, три элемента И 5, 6 и 7 и интегратор 8. В момент совпадения импульсов на входах элемента И 7 и на его выходе формируется импульс сброса, который устанавливает D-триггеры 3 и 4 в нулевое состояние. Таким образом, формирование импульса сброса осуществляется без участия D-триггеров 3 и 4, которые в этом случае не вносят задержки в цепь формирования импульса сброса. Цель достигается введением элемента И 7. 2 ил. . с $ W ю 4ib О 00 09 4 Фиг.1

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 4105947, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1986-07-23—Публикация

1983-10-28—Подача