Изобретение относится к вычислительной технике и может быть использовано в специализированных и универсальных вычислительных устройствах и является усовершенствованием известного устройства по авт.св. 1041085.

Целью изобретения является расширение функциональных возможностей за счет реализации операции вычитания.

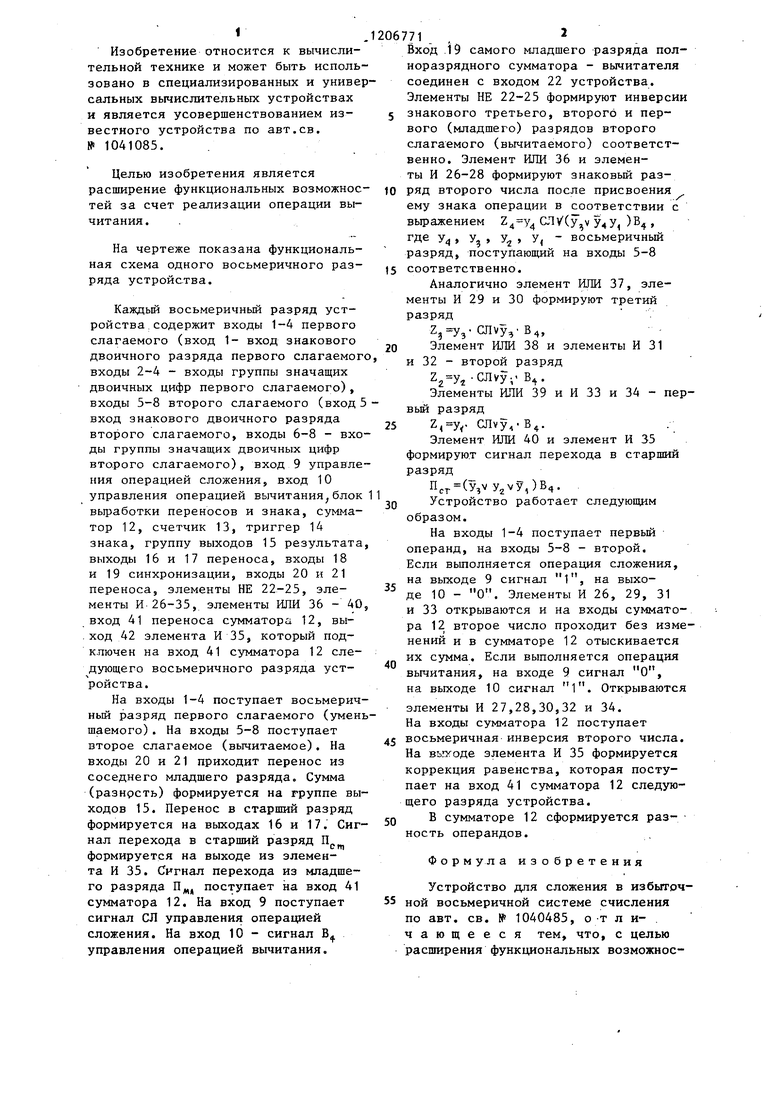

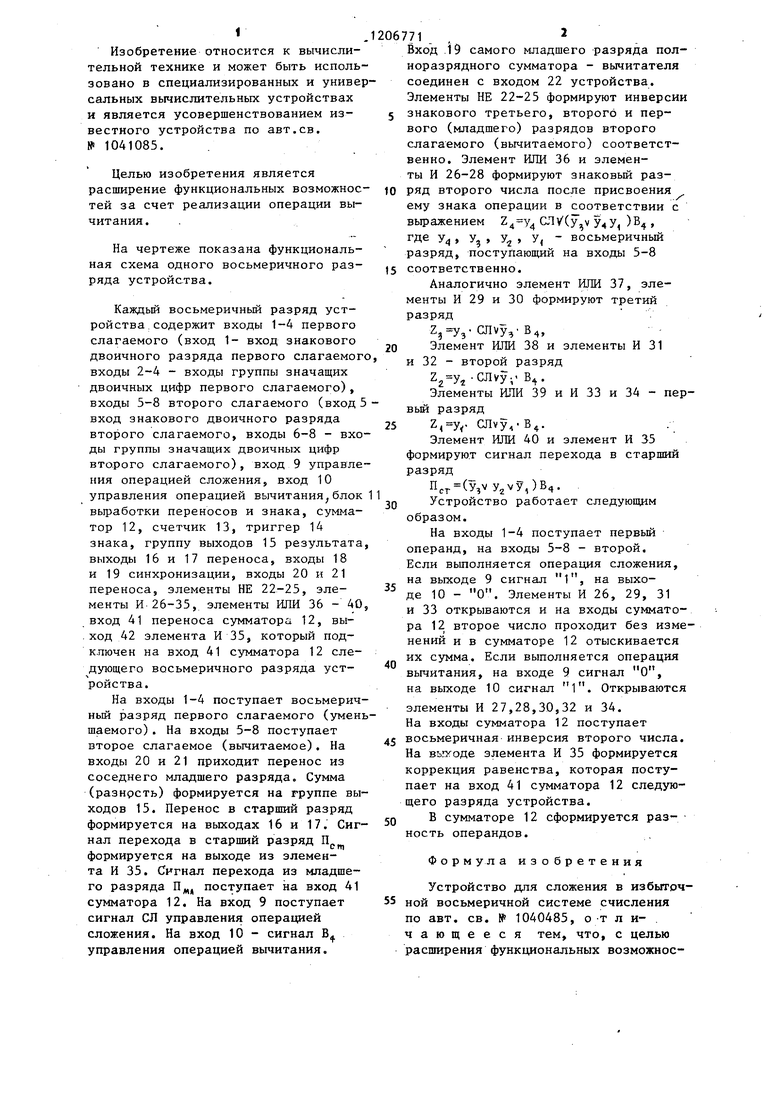

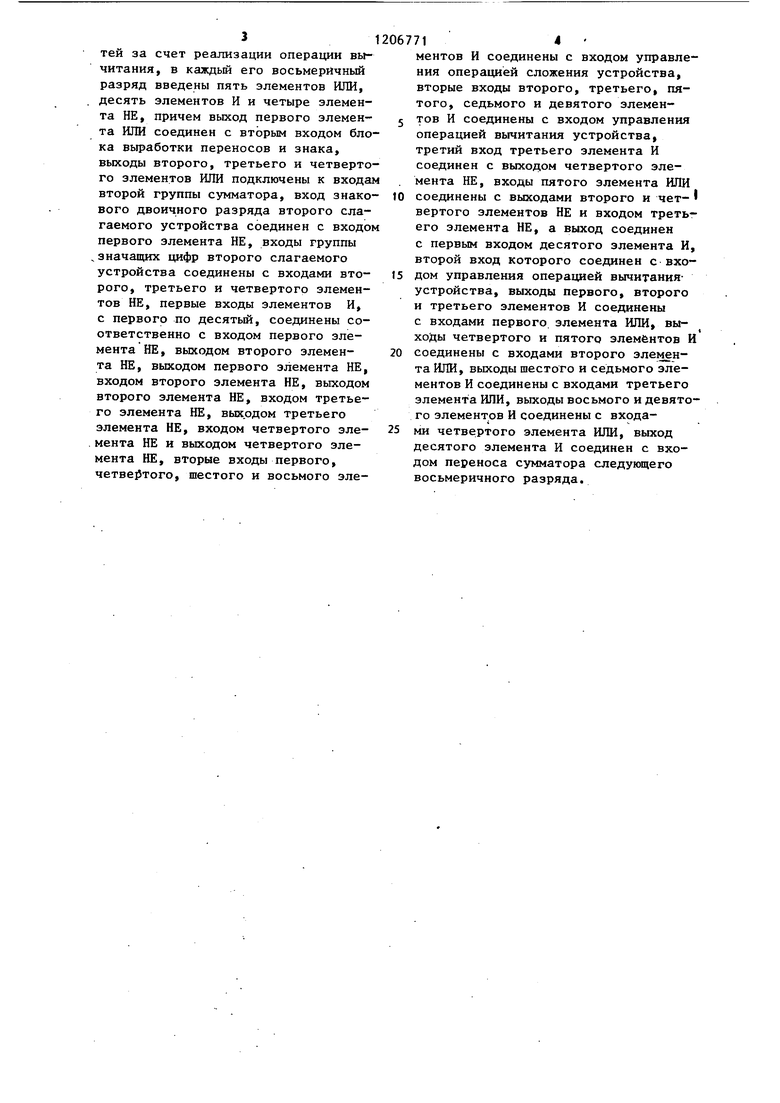

На чертеже показана функциональная схема одного восьмеричного разряда устройства.

Каждый восьмеричный разряд устройства содержит входы 1-4 первого слагаемого (вход 1- вход знакового двоичного разряда первого слагаемог входы 2-4 - входы группы значащих двоичных цифр первого слагаемого), входы 5-8 второго слагаемого (вход 5 вход знакового двоичного разряда второго слагаемого, входы 6-8 - входы группы значащих двоичных цифр второго слагаемого), вход 9 управления операцией сложения, вход 10 управления операцией вычитания,блок вьфаботки переносов и знака, сумматор 12, счетчик 13, триггер 14 знака, группу выходов 15 результата выходы 16 и 17 переноса, входы 18 и 19 синхронизации, входы 20 и 21 переноса, элементы НЕ 22-25, элементы И 26-35, элементы ИЛИ 36 - 40 вход 41 переноса сумматора 12, вы- .ход 42 элемента И 35, который подключен на вход 41 сумматора 12 следующего восьмеричного разряда устройства.

На входы 1-4 поступает восьмеричный разряд первого слагаемого (уменьшаемого) . На входы 5-8 поступает второе слагаемое (вычитаемое). На входы 20 и 21 приходит перенос из соседнего младшего разряда. Сумма (разнрсть) формируется на группе выходов 15. Перенос в старший разряд формируется на выходах 16 и 17. Сигнал перехода в старший разряд П формируется на выходе из элемента И 35 . Сигнал перехода из младшего разряда поступает на вход 41 сумматора 12. На вход 9 поступает сигнал СЛ управления операцией сложения. На вход 10 - сигнал В управления операцией вычитания.

cm

, - 11

10

15

20

25

30

35

40

45

50

Вход .19 самого младшего разряда полноразрядного сумматора - вычитателя соединен с входом 22 устройства. Элементы НЕ 22-25 формируют инверсии знакового третьего, второго и первого (младшего) разрядов второго слагаемого (вычитаемого) соответственно. Элемент ИЛИ 36 и элементы И 26-28 формируют знаковый разряд второго числа после присвоения ему знака операции в соответствии с вьфажением C-TV (y,v , )В4 , где у , у , у, , у, - восьмеричный разряд, поступающий на входы 5-8 соответственно.

Аналогично элемент ИЛИ 37, элементы И 29 и 30 формируют третий разряд

Z,y,. CЛvy, В4,

Элемент ИЛИ 38 и элементы И 31 и 32 - второй разряд

г2 У4-СЛуу- В.

Элементы ИЛИ 39 и И 33 и 34 - пер- вьм разряд

Z,y. СЛуу,.В.

Элемент ИЛИ 40 и элемент И 35 формируют сигнал перехода в старший разряд

n,(y,vy,,vy,)B4.

Устройство работает следующим образом.

На входы 1-4 поступает первьй операнд, на входы 5-8 - второй. Если выполняется операция сложения, на выходе 9 сигнал 1, на выходе 10 - О, Элементы И 26, 29, 31 и 33 открываются и на входы сумматора 12 второе число проходит без изменений и в сумматоре 12 отыскивается их сумма. Если выполняется операция вычитания, на входе 9 сигнал О, на выходе 10 сигнал 1. Открываются

элементы И 27,28,30,32 и 34. На входы сумматора 12 поступает восьмеричная инверсия второго числа. На выходе элемента И 35 формируется коррекция равенства, которая поступает на вход 41 сумматора 12 следующего разряда устройства.

В сумматоре 12 сформируется разность операндов.

Формула изобретения

Устройство для сложения в избыточ- ной восьмеричной системе счисления по авт. св. № 1040485, о -т л и- . чающееся тем, что, с целью расширения функциональных возможноетей за счет реализации операции вычитания, в каждый его восьмеричный разряд введены пять элементов ИЛИ, десять элементов И и четыре элемента НЕ, причем выход первого элемен- та ИЛИ соединен с вторым входом блока выработки переносов и знака, выходы второго, третьего и четвертого элементов ИЛИ подключены к входам второй группы сумматора, вход знако- tO вого двоичного разряда второго слагаемого устройства соединен с входом первого элемента НЕ, входы группы значащих цифр второго слагаемого устройства соединены с входами вто- 15 рого, третьего и четвертого элементов НЕ, первые входы элементов И, с первого по десятый, соединены соответственно с входом первого элеента НЕ, выходом второго элемен- 20 та НЕ, выходом первого элемента НЕ, входом второго элемента НЕ, выходом второго элемента НЕ, входом третьего элемента НЕ, выходом третьего элемента НЕ, входом четвертого эле- 25 ента НЕ и выходом четвертого элеента НЕ, вторые входы первого, етвертого, шестого и восьмого элегментов И соединены с входом управления операцией сложения устройства, вторые входы второго, третьего, пятого, седьмого и девятого элементов И соединены с входом управления операцией вычитания устройства, третий вход третьего элемента И соединен с выходом четвертого элемента НЕ, входы пятого элемента ИЛИ соединены с выходами второго и четвертого элементов НЕ и входом третьего элемента НЕ, а выход соединен с первым входом десятого элемента И, второй вход которого соединен с-входом управления операцией вычитания- устройства, выходы первого, второго и третьего элементов И соединены с входами первого элемента ИЛИ, вы- хойы четвертого и пятого элементов И соединены с входами второго элемента ИЛИ, выходы шестого и седьмого элементов И соединены с входами третьего элемента ИЛИ, выходы восьмого и девятого элементов И соединены с входами четвертого элемента ШШ, выход десятого элемента И соединен с входом переноса сумматора следующего восьмеричного разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения в избыточной восьмеричной системе счисления | 1982 |

|

SU1040485A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Последовательный сумматор кодов с иррациональными основаниями | 1985 |

|

SU1259249A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для суммирования п-разрядных двоичных чисел | 1976 |

|

SU634275A1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

Изобретение относится к области вычислительной техники. Целью изобретения является расширение функциональных возможностей устройства путем реализации операции вычитания. Это достигается тем, что устройство содержит в каждом разряде пять элементов ИЛИ, десять элементов И и четыре элемента НЕ с соответствующими связями. 1 ил. Дополнительное к авт.св.№ 1040485.

| Устройство для сложения в избыточной восьмеричной системе счисления | 1982 |

|

SU1040485A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-23—Публикация

1984-07-10—Подача