Изобретение относится к вычислительной технике и может быть использовано для суммирования, и вычитания многоразрядных последовательных кодов с иррациональными основаниями.

Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности вьшолнения операции вычитания чисел, представленных кодами с иррациональными основаниями.

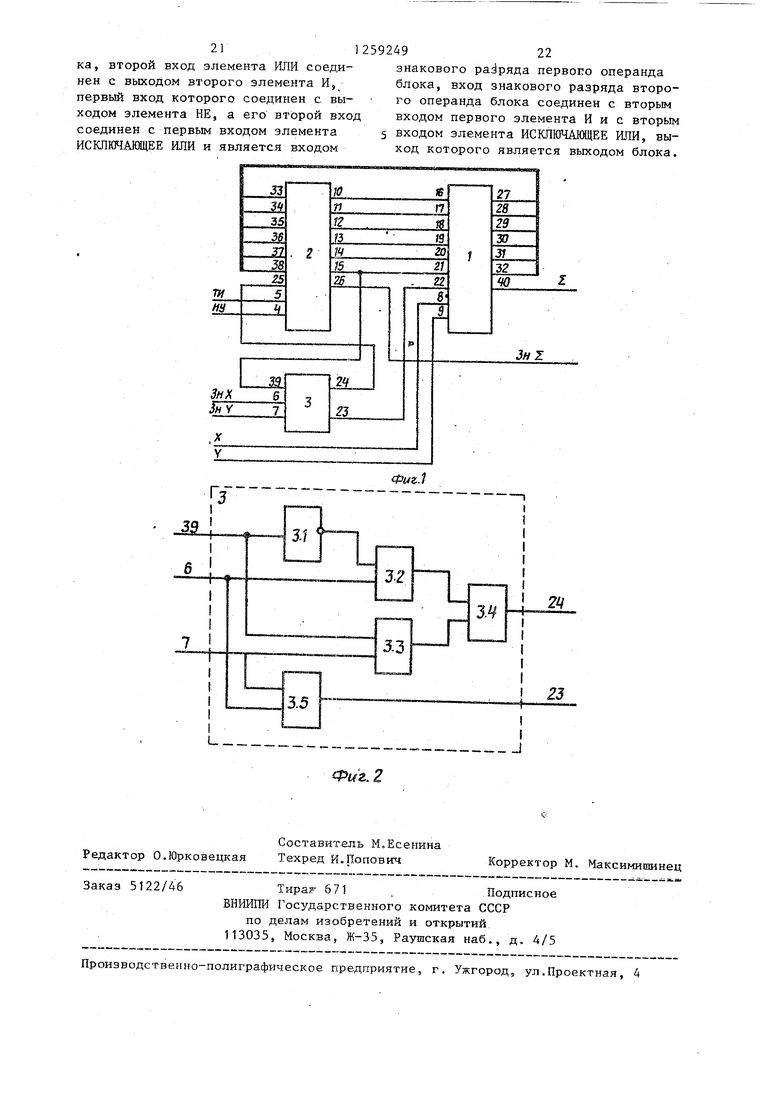

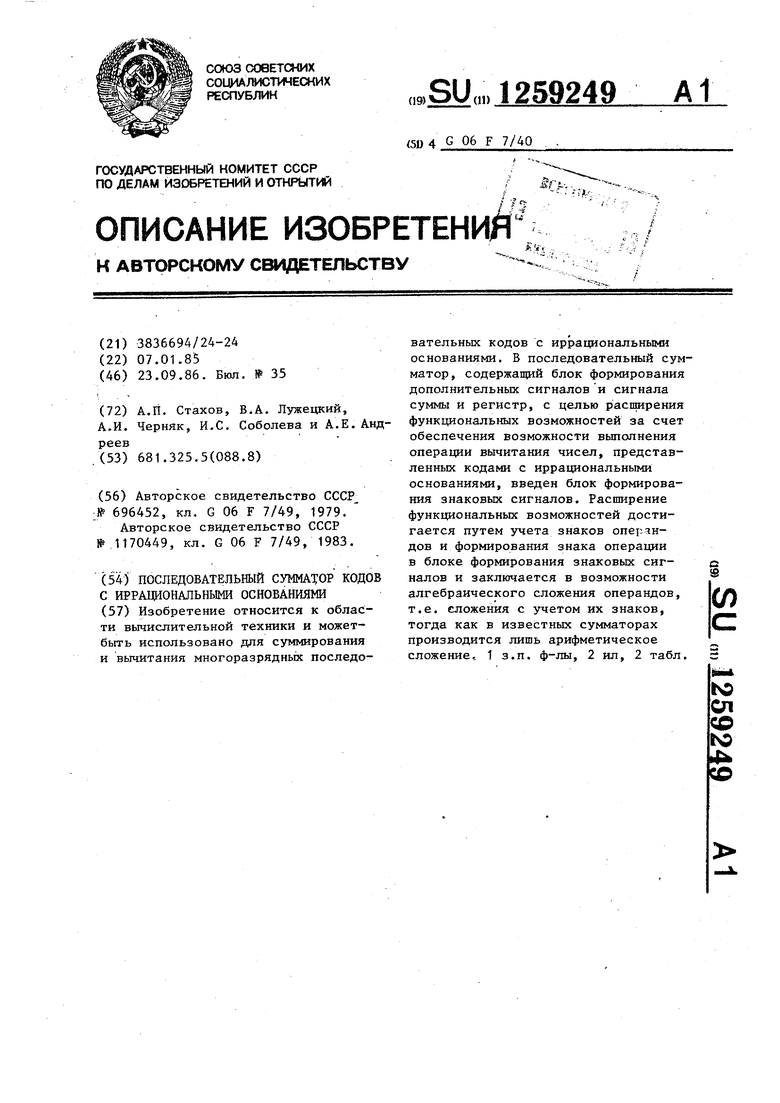

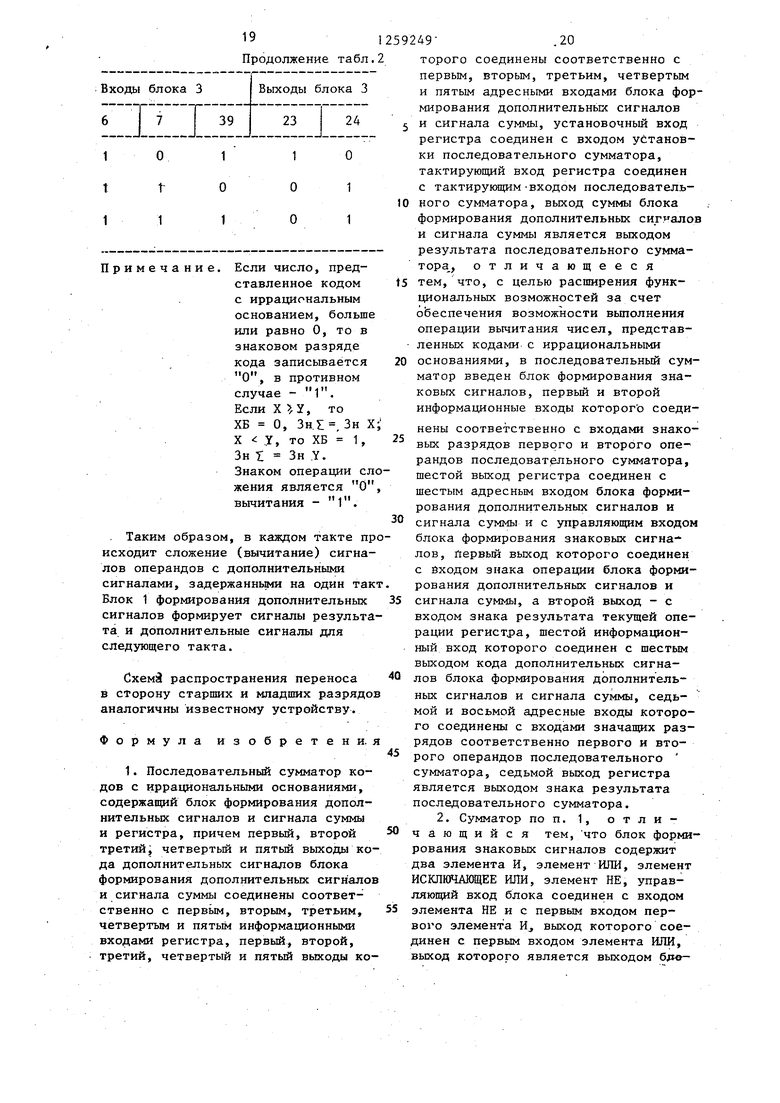

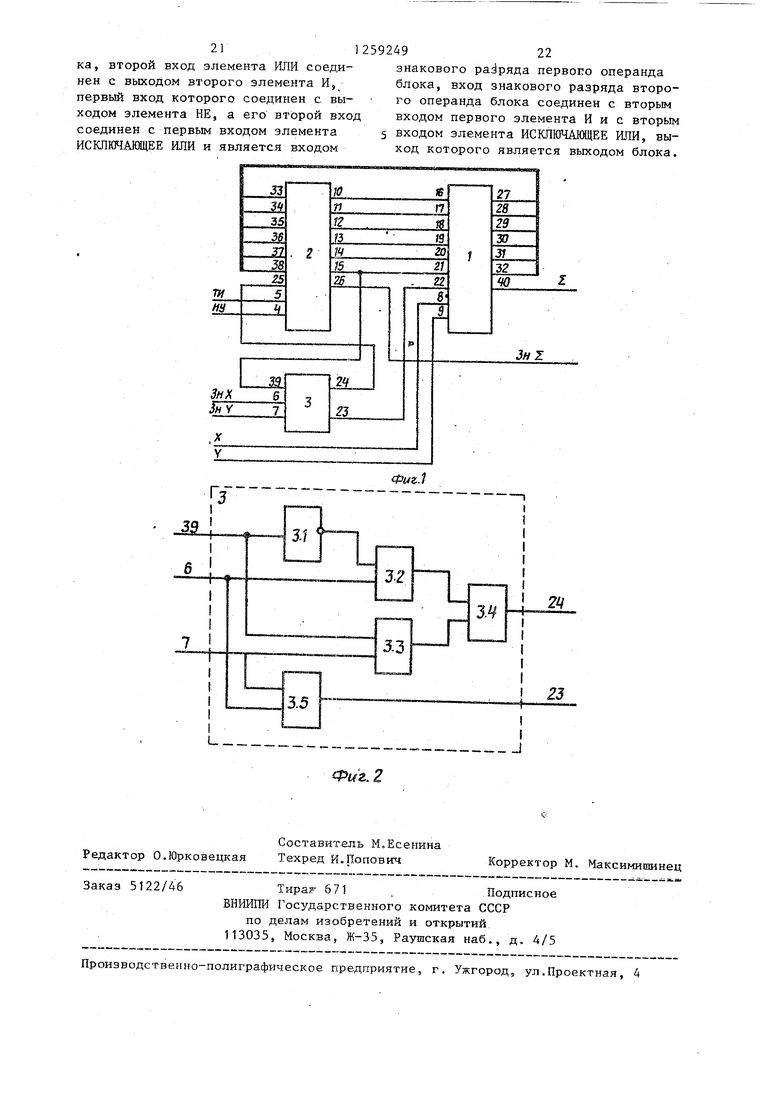

На фиг. 1 представлена структурная схема последовательного сумматора кодов с иррациональными основаниями j на фиг. 2 - функциойальная схема блока формирования знаковых сигналов.

Сумматор содержит блок 1 формирования дополнительных сигналов и сигнала суммы, регистр 2, блок 3 формирования знаковых сигналов, включающий элемент НЕ 3.1, элементы И 3.2 и 3.3, элемент ШШ 3.4 и элемент ИСКЛЮЧАНЩЕЕ ИЛИ 3.5, вход 4 установки, тактирующий вход 5, входы 6 и 7 знакового разряда первого и второго слагаемых соответственно, входы 8 и 9 значащих разрядов первого и второго слагаемьк соответственно, выходы 10-15 регистра, адресные входы 16-21 блока формирования дополнительных сигналов, вход 22 знака операции блока формирования дополнительных сигналов, первый и второй

5

0

5

0

выходы 23 и 4 блока формирования знаковых сигналов, вход 25 знака результата текущей операции регистра, выход 26 знака результата последовательного сумматора, выходы 27-32 блока формирования дополнительных сигналов и сигнала суммы, информационные входы 33-38 регистра, управляющий вход 39 блока формирбвания знаковых сигналов и выход 40 результата.

I Устройство работает следующим образом.

При поступлении единичного сигнала на вход 4 устройства регистр 2 устанавливается в нулевое состояние. ТГри поступлении сигналов на входы-6 и 7 знаков операндов блок 3 формирования знаковых сигналов формирует знак операций сложения или вычитания.

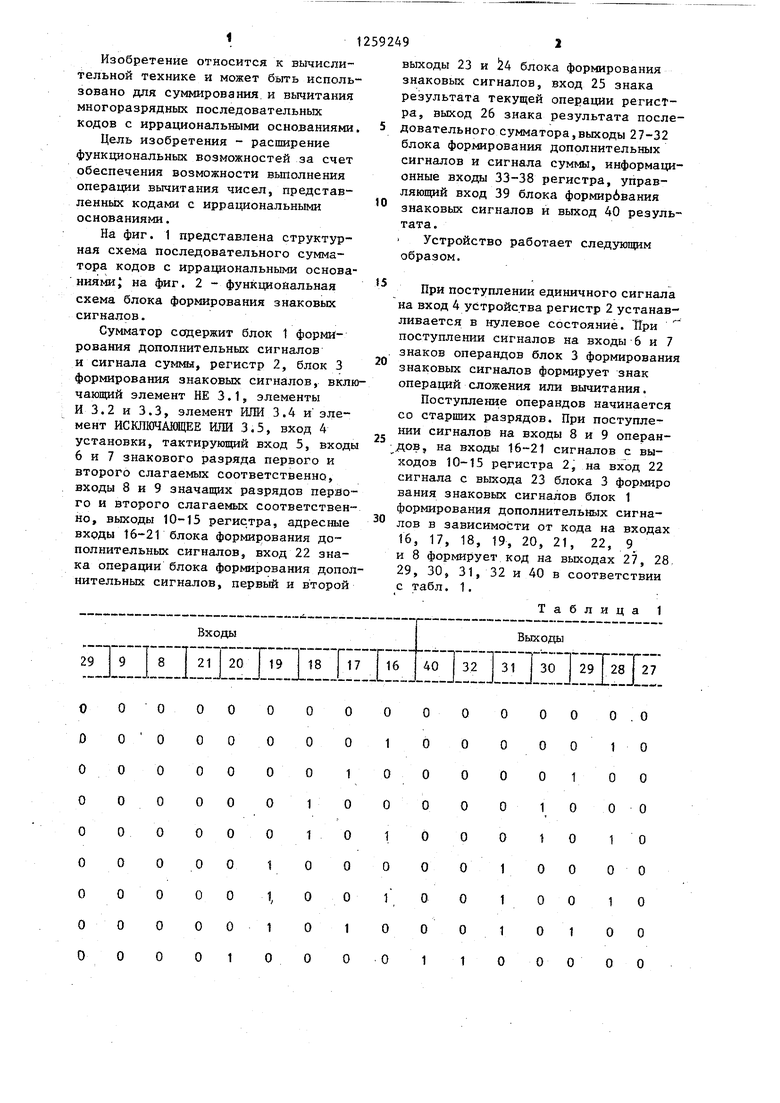

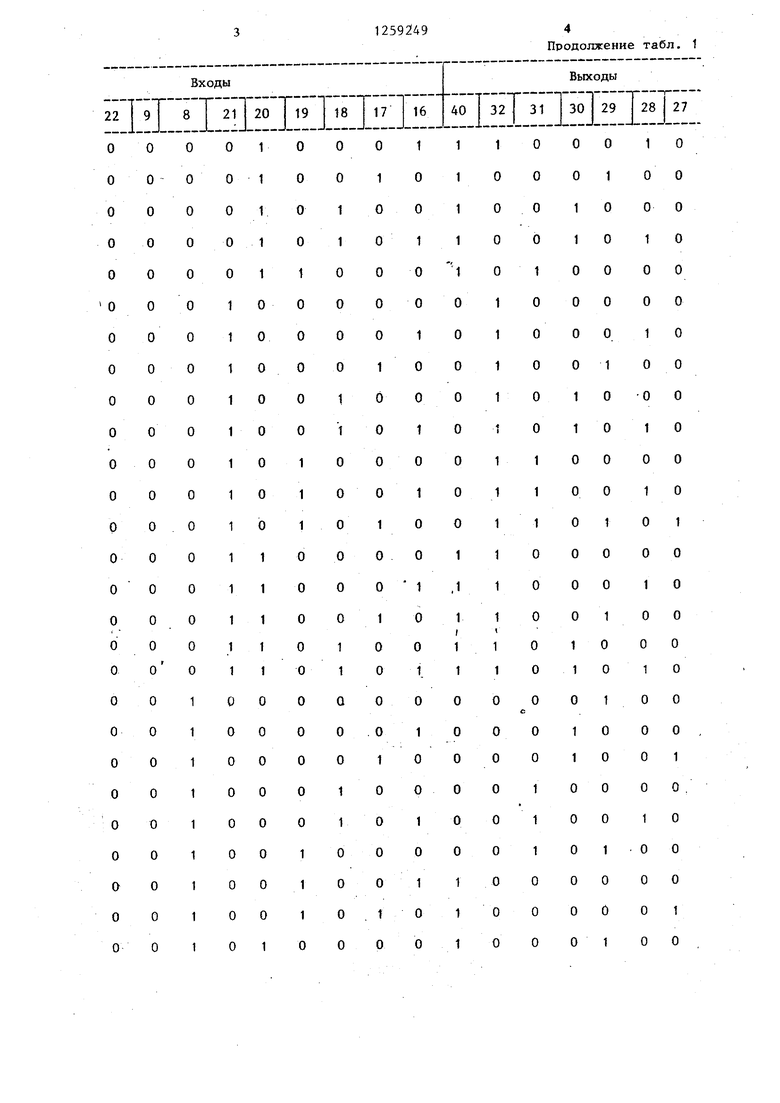

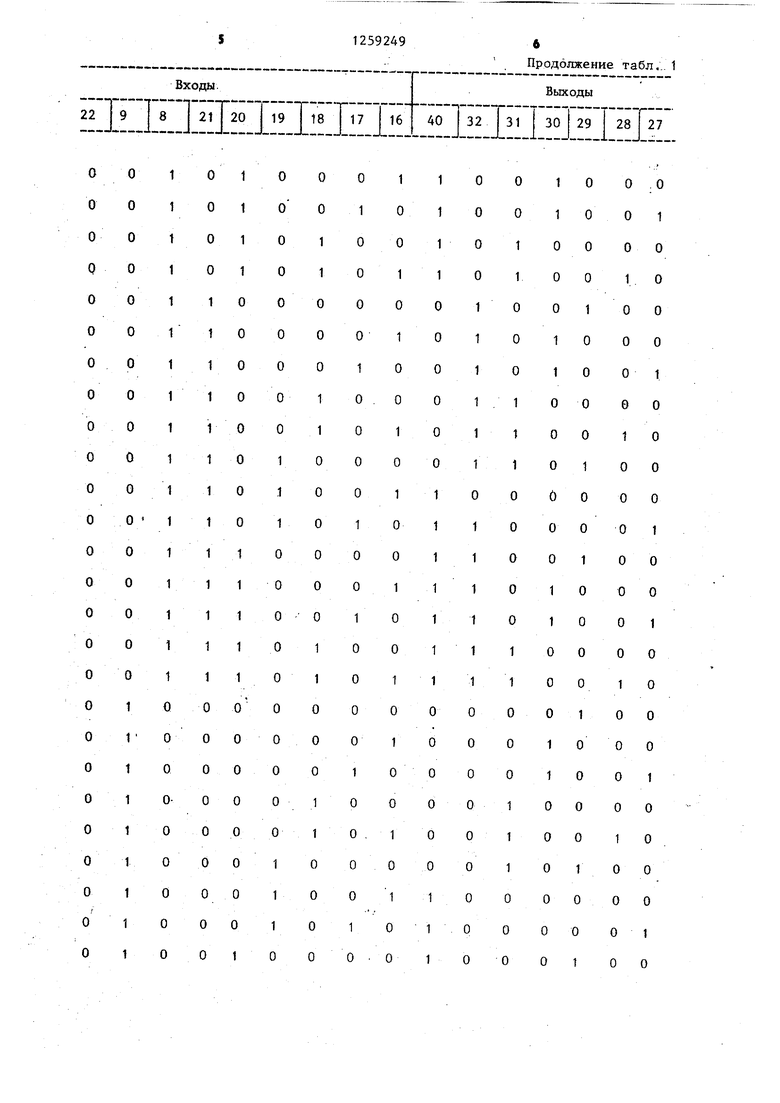

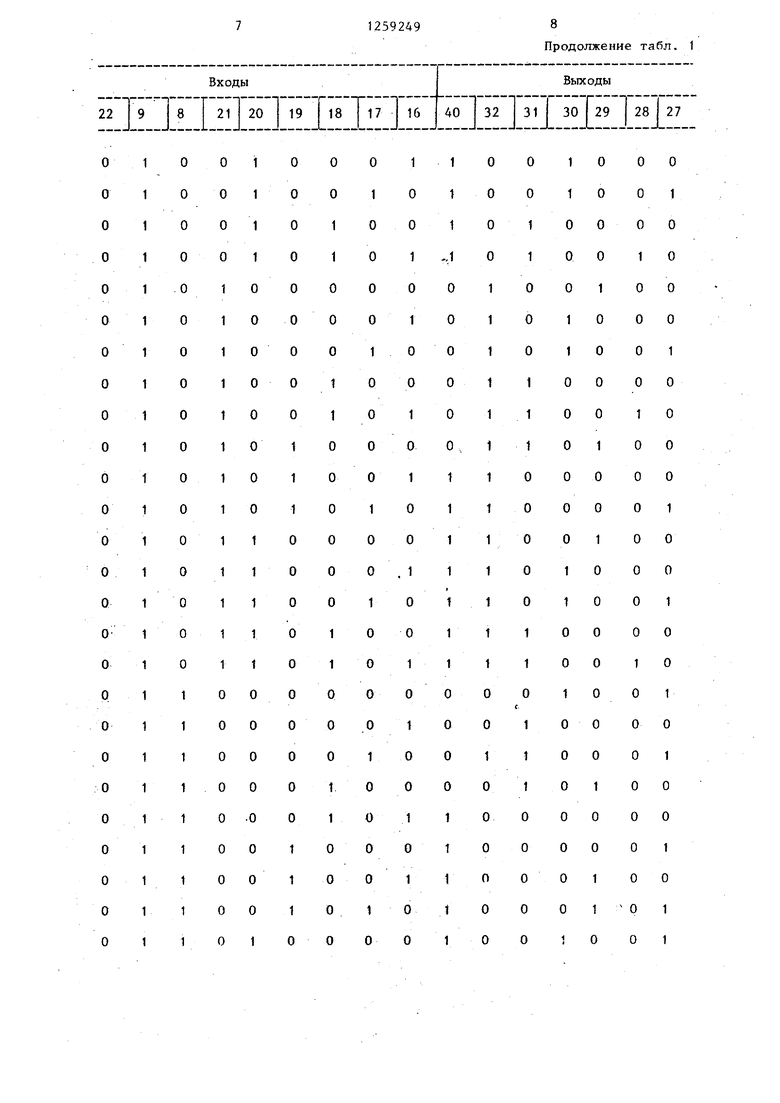

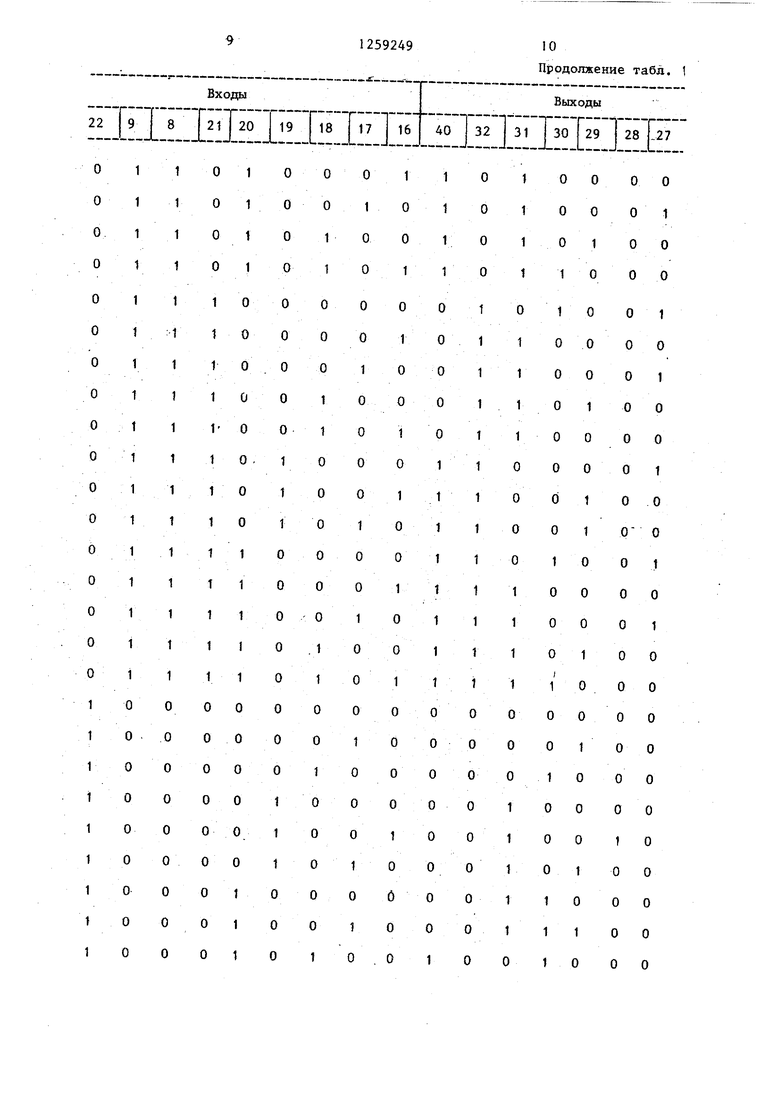

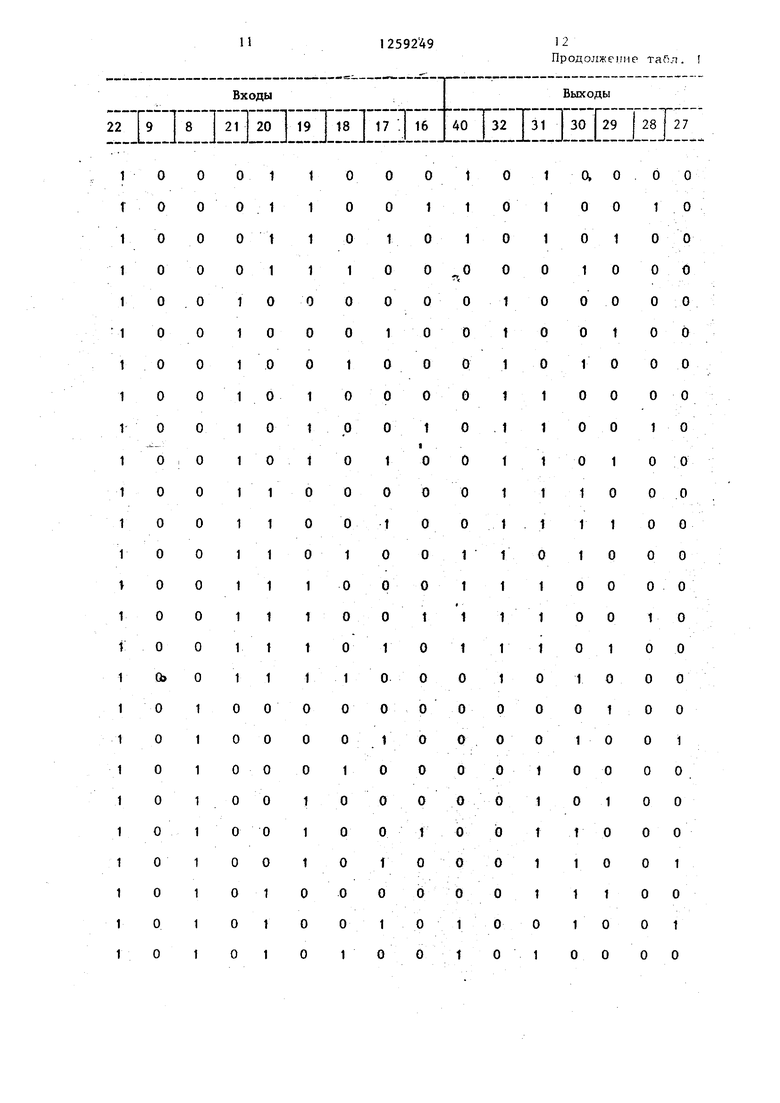

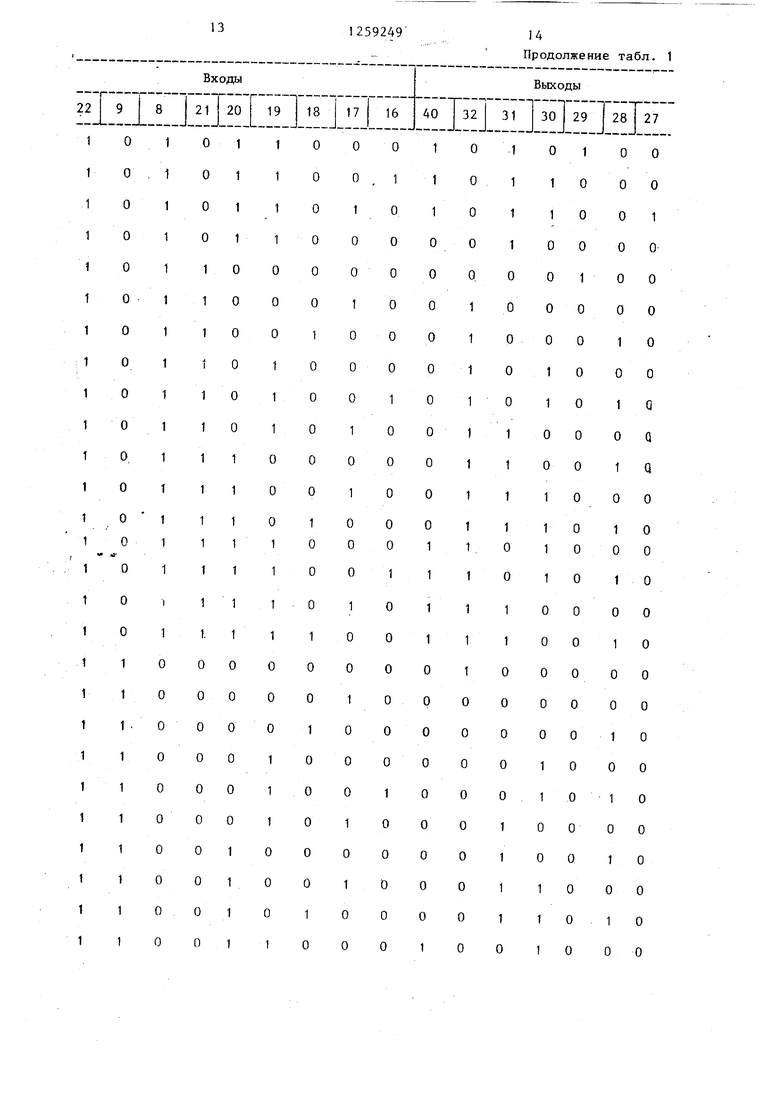

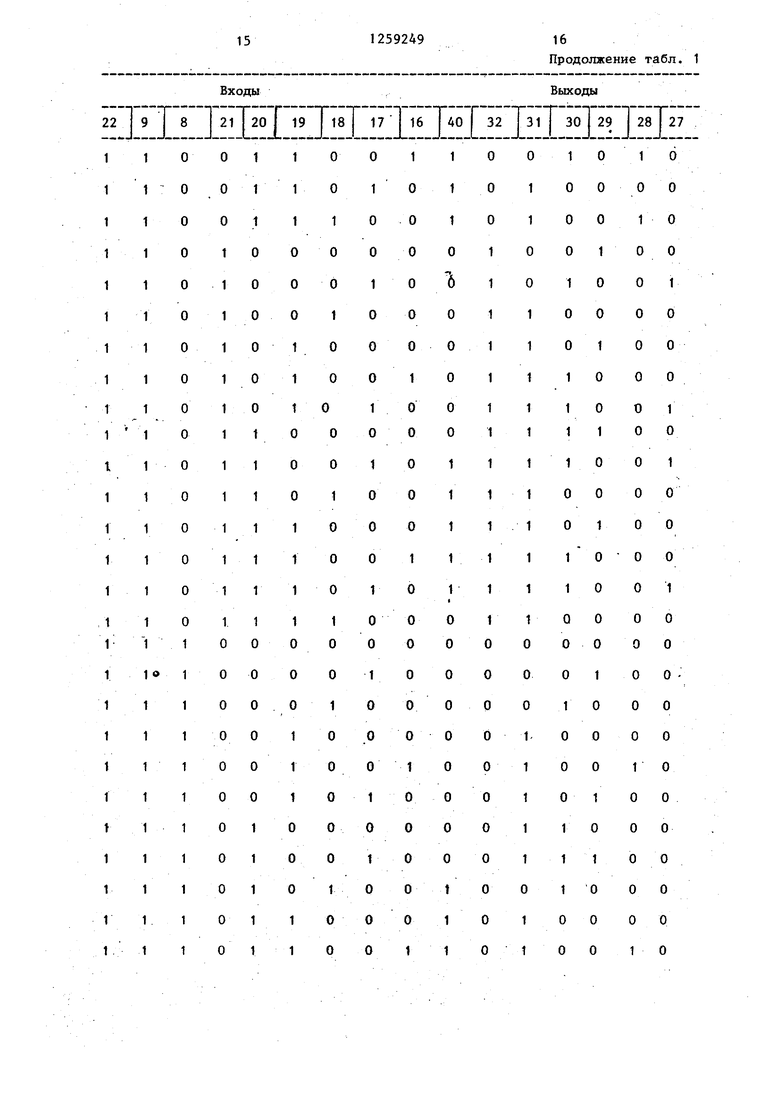

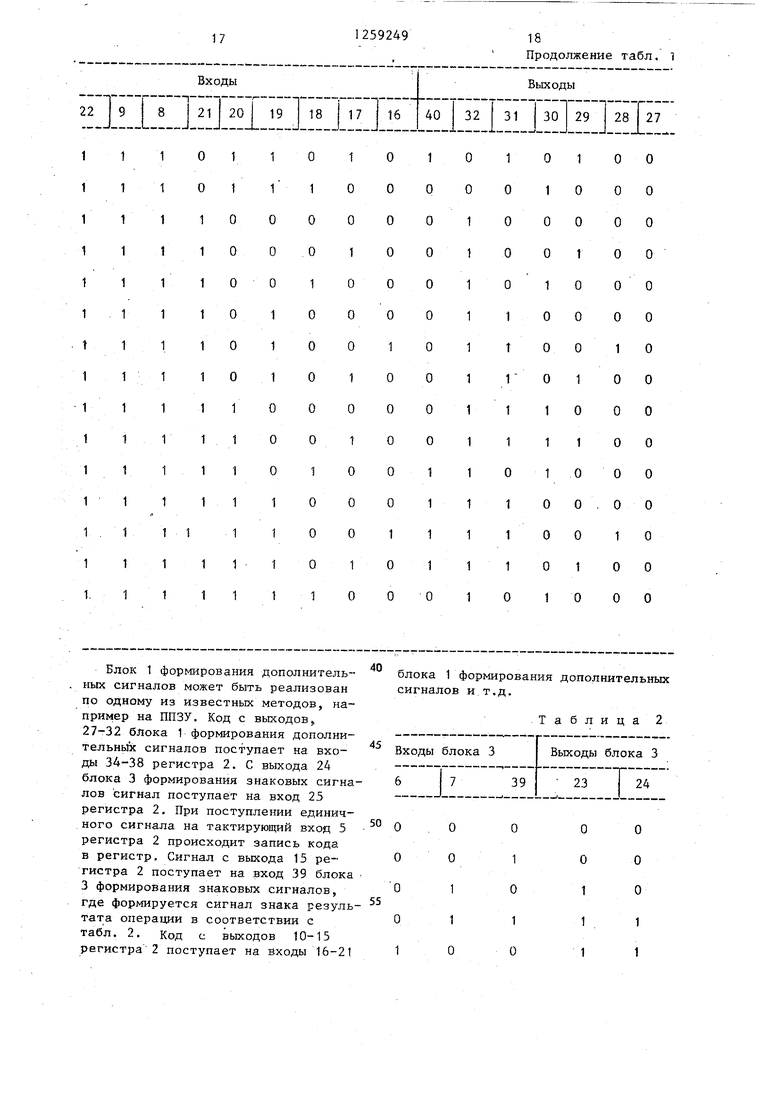

Поступление операндов начинается со старших разрядов. При поступлении сигналов на входы 8 и 9 операндов, на входы 16-21 сигналов с выходов 10-15 регистра 2, на вход 22 сигнала с выхода 23 блока 3 формиро вания знаковых сигналов блок 1 формирования дополнительных сигналов в зависимости от кода на входах 16, 17, 18, 19, 20, 21, 22, 9 и 8 формирует код на выходах 27, 28, 29, 30, 31, 32 и 40 в соответствии с табл. 1.

Таблица 1

Продолжение табл. 1

Продолжение табл... 1

8

Продолжение табл. 1

1259249

К)

Продолжение табл.

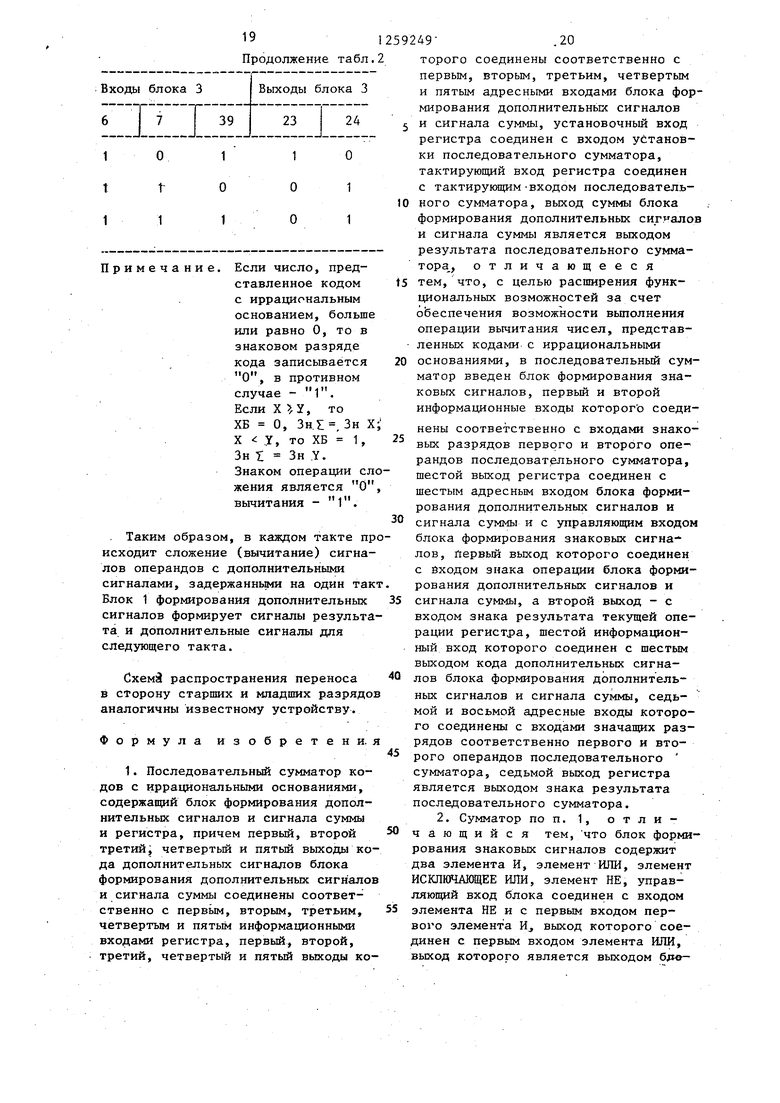

Блок 1 формирования дополнительных сигналов может быть реализован по одному из известньк методов, например на ППЗУ. Код с выходов., 27-32 блока 1 формирования дополнительных сигналов поступает на вхо- дь 34-38 регистра 2. С выхода 24 блока 3 формирования знаковых сигналов сигнал поступает на вход 25 регистра 2, При поступлении единичного сигнала на тактирующий вход 5 регистра 2 происходит запись кода в регистр. Сигнал с выхода 15 ре- тистра 2 поступает на вход 39 блока 3 формирования знаковьпс сигналов, где формируется сигнал знака резуль тата операции в соответствии с табл. 2. Код с выходов 10-15 регистра 2 поступает на йходы 16-2

Входы блока 3 О О 1

блока 1 формирования дополнительных сигналов и т.д.

-Таблица 2

ло

О

ло

о

Вх О О

О

55

Входы О О 1

О

ло

о

Примечание.

Если число, представленное кодом с иррациональным основанием, больше или равно О, то в знаковом разряде кода записывается О, в противном случае - 1, Если X , У, то ХБ О, Зн.5:. Зн Xi X У, то ХБ 1, Зн I Зн Y. Знаком операции сложения является О, вычитания - 1.

. Таким образом, в каждом такте происходит сложение (вычитание) сигналов операндов с дополнительными сигналами, задержаннь1ми на один такт Блок 1 формирования дополнительных сигналов формирует сигналы результата и дополнительные сигналы для следзтощего такта.

СхемЗ распространения переноса в сторону старших и младших разрядов аналогичны известному устройству.

Формула изобретен и. я

1. Последовательный сумматор кодов с иррациональными основаниями, содержащий блок формирования дополнительных сигналов и сигнала суммы и регистра, причем первый, второй третий, четвертый и пятый выходы кода дополнительных сигналов блока формирования дополнительных сигналов и сигнала суммы соединены соответственно с первьм, вторым, третьим, четвертым и пятым информационными входами регистра, первый, второй, третий, четвертый и пятый выходы ко

торого соединены соответственно с первым, вторым, третьим, четвертым и пятым адресными входами блока формирования дополнительней сигналов и сигнала суммы, установочный вход регистра соединен с входом установки последовательного сумматора, тактирующий вход регистра соединен с тактирукицим входом последовательного сумматора, выход суммы блока формирования дополнительных сигналов и сигнала суммы является выходом результата последовательного сумматора.

отличающееся

тем, что, с целью расширения функциональных возможностей за счет оЬеспечения возможности выполнения операции вычитания чисел, представленных кодами с иррациональными основаниями, в последовательный сумматор введен блок формирования знаковых сигналов, первый и второй информационные входы которого соединены соответственно с входами знаковых разрядов первого и второго операндов последовательного сумматора, шестой выход регистра соединен с шестым адресным входом блока формирования дополнительных сигналов и сигнала суммы и с управляющим входом блока формирования знаковых сигналов. Первый выход которого соединен с входом знака операции блока формирования дополнительных сигналов и сигнала суммы, а второй выход - с входом знака результата текущей операции регистра, шестой информационный вход которого соединен с шестым выходом кода дополнительных сигналов блока формирования дополнительных сигналов и сигнала суммы, седьмой и восьмой адресные входы которого соединены с входами значащих разрядов соответственно первого и второго операндов последовательного сумматора, седьмой выход регистра является выходом знака результата последовательного сумматора.

2. Сумматор по п. 1, отличающийся тем, что блок формирования знаковых сигналов содержит два элемента И, элемент ИЛИ, элемент ИСКЛЮЧАЩЕЕ ИЛИ, элемент НЕ, управляющий вход блока соединен с входом элемента НЕ и с первым входом первого элемента И выход которого соединен с первым входом элемента ИЛИ, выход которого является выходом бдю21

ка, второй вход элемента ИЛИ соединен с выходом второго элемента И,/ первый вход которого соединен с выходом элемента НЕ, а его второй вхо соединен с первым входом элемента ИСКПЮЧАКЩЕЕ ИЛИ и является входом

L.

Фиг.. 2

Редактор О.Юрковецкая

Составитель М.Есенина Техред И.Попович

Заказ 5122/46

Тирак 671 .Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий. 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул.Проектная, 4

49

22

знакового разряда первого операнда блока, вход знакового разряда второго операнда блока соединен с вторым входом первого элемента И и с вторым входом элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход которого является выходом блока.

J

Корректор М. Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор | 1989 |

|

SU1633392A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Устройство для сложения и вычитания | 1984 |

|

SU1193664A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для алгебраического вычитания | 1985 |

|

SU1297036A1 |

Изобретение относится к области вычислительной техники и может- быть использовано для суммирования и вычитания многоразрядньЬс последовательных кодов с иррациональными основаниями. В последовательный сумматор, содержащий блок формирования дополнительных сигналов и сигнала суммы и регистр, с целью распшрения функциональных возможностей за счет обеспечения возможности выполнения операции вычитания чисел, представленных кодами с иррациональными основаниями, введен блок формирования знаковых сигналов. Расширение функциональных возможностей достигается путем учета знаков операндов и формирования знака операции в блоке формирования знаковых сигналов и заключается в возможности алгебраического сложения операндов, т.е. сложения с учетом их знаков, тогда как в известных сумматорах производится лишь арифметическое сложение, 1 з.п. ф-лы, 2 ил, 2 табл. (Л с: 1C СП ;о

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-01-07—Подача