Л ИЛ IV

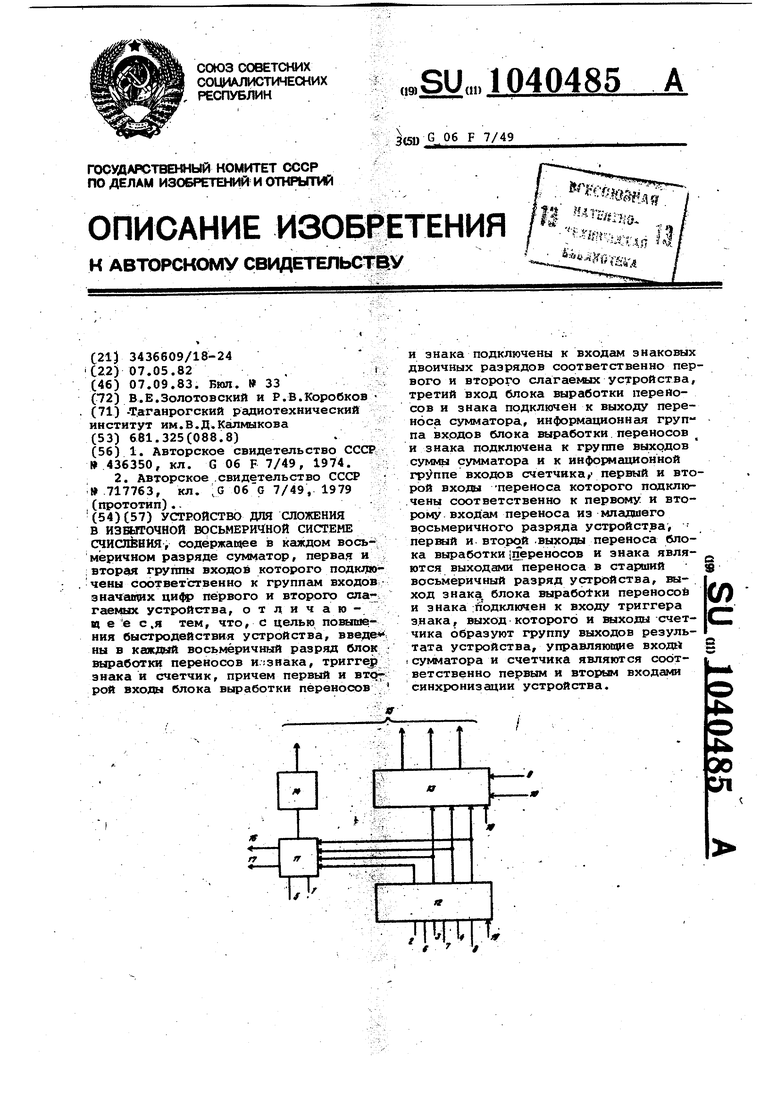

t V Изобретение относится к вычислительной технике и может быть использовано в специализированных и уливерсальных арифметико-логических устройствах (ДЛУ/. , Известно много различных типов суммирующих устройств, работающих в двоичной или связанной с ней {8-16ричмых системах счисления. В качестве основного элемента в них ИС пользован трехвходовой комбинационный сумматор. Соединяя комбинационные сумматоры последовательно по цепи переноса, можно получить устройство для параллельного сложения чисел Cl . Недостатком таких устройств явля втся низкое быстродействие, обуслов. ленное последовательным распространением переноса по разрядам сумматора. Попытки увеличить быстродействие таких суммирующих устройств сопряжено с увеличением затрат оборудования. Наиболее близким по технической сущности к предлагаемому является устройство для сложения в избыточной системе счисления, содержащее два сумматора, три линии задержки и функ циональный блок, первые входы (д и А2) сумматора соединены с входом уст ройства л,вторые входы сумматора (В1 и В2 ) соединены с входом устройс ва В, третий вход сумматора (вход пе реноса ) соединен с третьим входом устройства В, первый выход суммы S соединен через линии задержки с первыми входами второго сумматора,второ выход суммы $2 соединен с третьим входом второго сумматора (вход переноса , вторые входы через линию задержки соединены со входом устройства А, первый выход второго сумматора через линию задержки соединен с первым-входом функционального блока, а второй выход сумматора с вторым входом функционального блока, первый ( второй (2) выходы которого яв ляются выходами Недостатком устройства-прототипа является невысокое быстродействие ввиду роета задержки получения сумкы с увеличением разрядности устройства Цель изобретения - повьшение быст родействия устройства. Поставленная цель достигается тем что устройство для сложения в избыточной восьмеричной системе счисления, содержащее в каждом восьмеричном разряде сумматор, первая и втора группы входов которого подключены со ответственно к группам входов значащих цифр первого и второго слагаемых устройства, введены в каждый восьмеричный разряд блок выработки переносов и знака, триггер знака и счетчик причем первый и второй входы блока выработки переносов и знака подключе ны к входам знаковых двоичныхразрядов соответственно первого и второго слагаемых устройства, третий вход блока выработки переносов и знака подключен к выходу переноса сумматора, информационная группа входов блока выработки переносов и знака подключена к группе выходов суммы сумматора и к информационной группе входов счетчика, первый и второй входы переноса которого подключены соответственно к первому и второму входам переноса из младшего восьмеричного разряда устройства, первый и второй выходы переноса блока выработки переносов и знака являются выходами Переноса в старший восьмеричный разряд устройства, выход знака блока выработки переносов и знака подключен к входу триггера знака, выход которого и выходы счетчика образуют группу выходов результата устройства, управляющие входы сумматора и счетчика являются соответственно первым и втоым входами синхронизации устройства. На чертеже показана схема устройства. На входы группы входов первого слагаемого устройства 1-4 подаются разряды первого слагаемого AJ, Л, А2, А, причем на вход 4 подается младишй разряд первого слагаемого А. На входы группы входов второго слагаемого устройства 5-8,подаются разряды второго слагаемого Ь., . Ъ, Ър, Ь, причем на вход 8 подается младший разряд второго слагаемого Ъ. На входы переноса 9 и 10 подаются переносы П, П из младшего восьмеричного разряда устройства. Входы устройства 1 и 5 соединены с первым и вторым входами блока 11 выработкипереносов и знака входы 2-4 соединены с соответствук цими входами первой группы сумматора 12, а входы 6-8 соответствукнцими входс1ми второй группы сумматора 12, группа входов суммл подключена к информационной группе входов счетчика J.3 и информагщонной группе входов блока 11J выход переноса сумматора 12 соединен с третьим, входом блока 11, выход знака блока 11 соединен с входом 14 триггера зцдка, выходы счетчика триггера знака образуют группу выходов 15 результата устройства, выходы переноса 16 и 17 блока 11 являются выходами переноса в старший восьмеричный разряд устройства, входы переноса 9 и 10 подключены к входам переноса счетчика 13. Входы 18 и 19 являются первым и вторым йходами синхронизации устройства. Устройство работает следующим образом. Восьмеричная цифра представляется четырьмя двоичными разрядами: значащих и один знаковый. При предст быть использо гательное коди кодировании и цифры. Восьмеричн -4 -3 , -2 . -1: О +1 +3 +4 +5 Ее двоично 1100 1101 1110 0000 0101 Остальные д запрещены. При ровании исполь Восьмерична

П

-1 +1 i +4-3 +3 +4-3

Полная

1 +3-1+1 -2 +5 -3 +2 +4-4 О

сумма

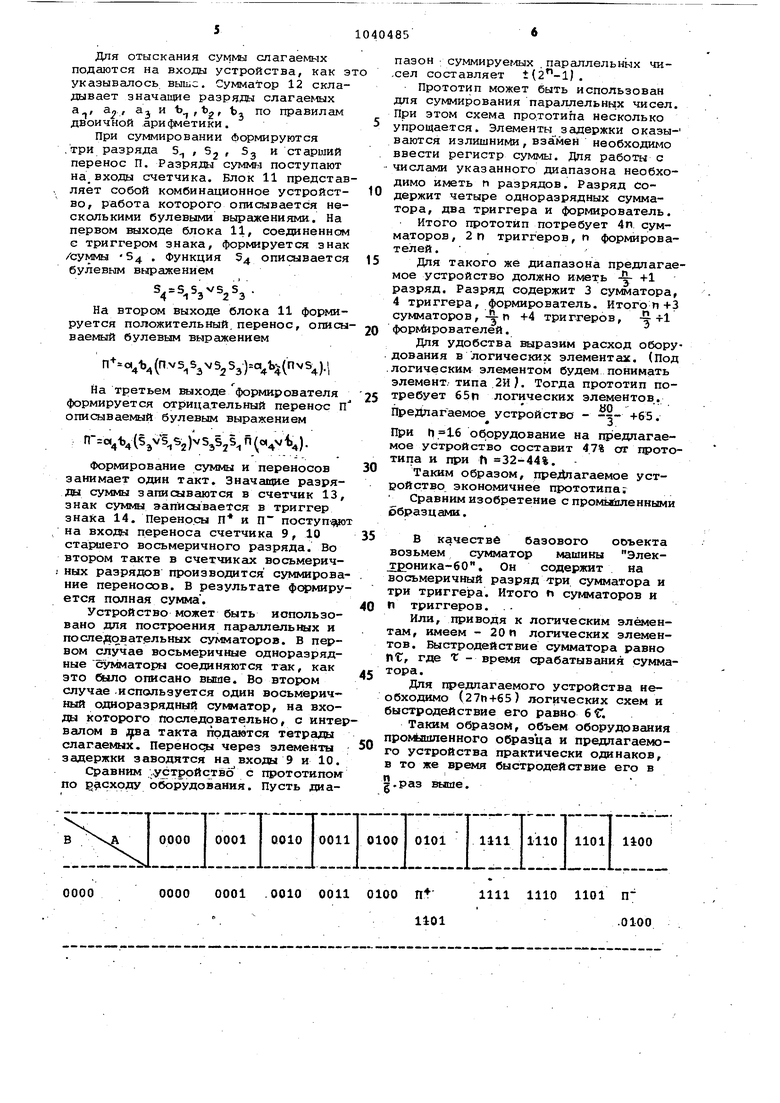

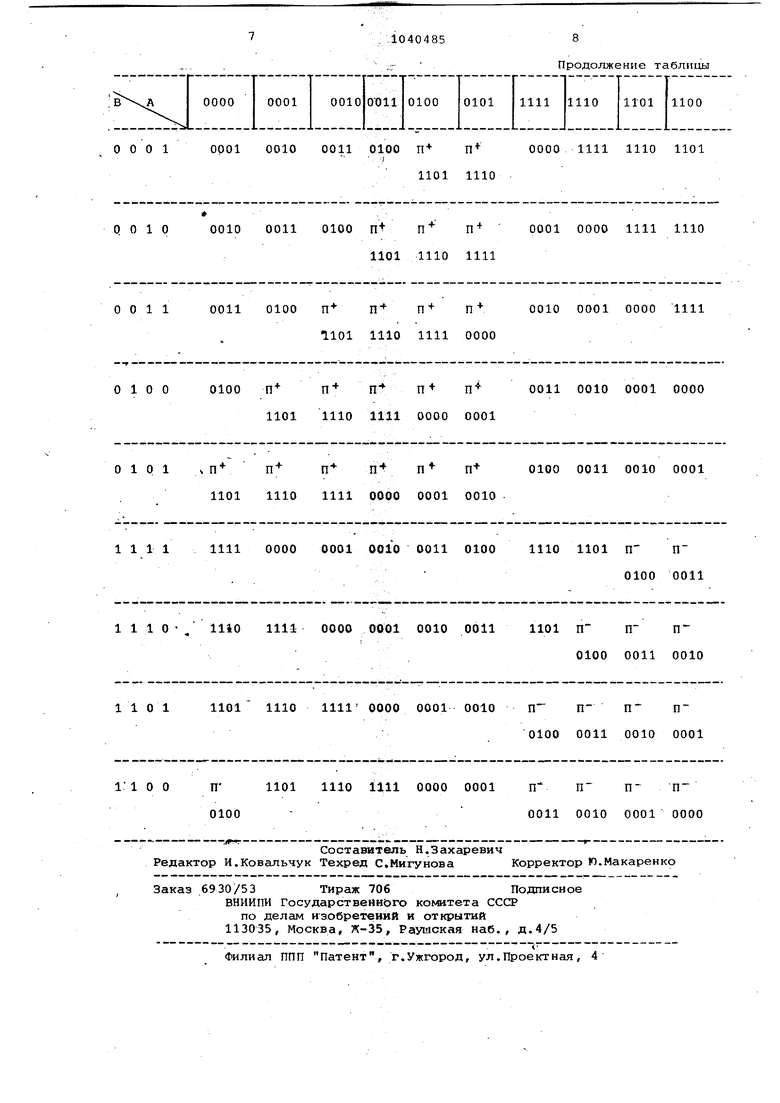

- - П п+ - п- -. + 4 Ее двоичное кодирование 1101 1110 . 1111 0000 0001 0010 ООН 010,0 Выполнение операции суммирования требует двух тактов. В первом такте формируется частичная сумма в вспомогательном коде и перенос в старший разряд. Перенос в старший разряд может быть положительным П или отрицательным П . В таблице показано сложе:ние сумматора. В верхней строке приведены все возможные значения восьмеричного разряда первого слагаемого (А). В левом столбце - все возможные значения восьмеричного разряда второго слагаемого. В ячейках таблицы указываются значения частичной сукмы. Если при суммировании возникает положительный или отрицательный перенос, в ячейке ставится П или П. Так как при формировании частичной суммы перенос распространяется не более, чем на три разряда, время формирования частичной суммы не превосходит такта. Во втором такте к частичной сумме прибавляются переносы. При этом формируются полные суммы. При формиро-вании полной суммы перенос такта распространяется не более, чем на три разряда, поэтому время формирования также невелико, не более такта. Пример. Пусть необходимо сложить два слагаемых 0 +0 -1 -2 -3 -4 4+5 +4-2 0.-4

Для отыскания суммы слагаемых подаются на входы устройства, как э указывалось выше. Сумматор 12 складывает значащие разряды слагаемых а , ар , aj и Ь , 2 Ь, по правилам двоичной .арифметики.

При суммировании Формируются .три разряда 5 , Sj , Sg и старший перенос П. Разряды суммгл поступают на входы счетчика. Блок 11 представляет собой комбинационное устройство, работа которого описывается несколькими булевыми выражениями. На первом выходе блока 11, соединенном с триггером знака, формируется знак /суммы -54 . функция $4 описывается булевым выражением

втором выходе блока 11 формируется положительный, перенос, опйсы булевым выражением

,Ъ4(Пv5 SзV525з)c,Ъ(ПvS).

На третьем выходе формирователя формируется отрицательный перенос П описываемый булевым выражением

(.2)5э525-, ();

Формирование суммы и переносов занимает один такт. Значащие разряды суммы записываются в счетчик 13, знак суммы записывается в триггер знака 14. Перено.сы П и П поступи на входы переноса счетчика 9,10 старшего восьмеричного разряда. Во втором Тсжте в счетчиках восьмеричных разрядов производится суммироваиие переносов. В результате фармкруется полная сумма.

Устройство может быть использовано для построения параллельных и после;аовательных сумматоров. В первом случае восьмеричные одноразрядные сумматоры соединяются так, как это было описано выше. Во втором случае .используется один восьмеричный одноразрядный сумматор, на входы которого последовательно, с интервалом в такта прда1втся тетрады слагаемых. Пepeнoqы через элементы задержки заводятся на входы 9 и 10.

Сравним .устройство с прототипом по сходу оборудования. Пусть диапазон ; суммируег/1ых параллельных чи,сел составляет ±().

Прототип может быть использован для суммирования параллельных чисел. При этом схема прототипа несколько упрощается. Элементы задержки оказываются излишними, взамен необходимо ввести регистр суммы. Для работы с числами указанного диапазона необходимо иметь h разрядов. Разряд содержит четыре одноразрядных сумматора, два триггера и формирователь.

Итого прототип потребует 4п сумматоров, 2п триггеров, п формирователей. .

Для такого же диапазона предлагаемое устройство должно иметь -у +1 разряд. Разряд содержит 3 сумматора, 4 триггера, формирователь. Итогоп+3 сумматоров, -4-п +4 триггеров, з форл 1рователей.

Для удобства выразим расход оборудования в логических элементах. (Под .логическим элементом будем понимать элемент/типа .2И К Тогда прототип потребует 65п логических элементов.

Пред1пагаемое устройство - -S- +65.

При оборудование на предлагаемое устройство составит 47% сгг прототипа и при h 32-44%.

Таким образом, предлагаемое устройство экономичнее прототипа;

Сравним изобретение с промышленными образцами.

В качестве базового ооъекта возьмем сумматор машины ЭлекХерника-60. Он содержит на восьмеричный разряд три сумматора и три триггера. Итого п сумматоров и п триггеров.

Или, приводя к логическим элементам, имеем - 20П логических элементов. Выстродействие сумматора равно , где t - время срабатывания сумматора.

Для щ едпагаемого устройства необходимо (27П+65) логических схем и быстродействие его равно 6 С.

Таким образом, объем оборудования промЬшшенного образца и предлагаекюго устройства практически одинаков, в то же время быстродействие его в

5.раз выше. о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения в избыточной восьмеричной системе счисления | 1984 |

|

SU1206771A2 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для суммирования | 1977 |

|

SU734678A1 |

| Устройство для умножения в избыточной системе счисления | 1983 |

|

SU1124286A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ В ИЗБЫТОЧНОЙ ВОСЬМЕРИЧНОЙ СИСТЕМЕ СЧИСЛЬНИЯ, содержавшее ie каждом восьмеричном разряде сумматор, первая и ; вторс1Я группы входов которого подюрочены соответственно к группам входовзначащих цифр первого и второго сла. гаекоях устройства, отличаю- ц е е с .я тем, что, с целью повыше,ния быстродействия устройства, введе ны в каждый восьмеричный разряд блок выработки переносов и.гэнака, тригг знака и счетчик, причем первый и вто7 рой входы блока выработки переносов и знака подключены к входам знаковых двоичных разрядов соответственно первого и второго слагаемых устройства, третий вход блока выработки переносов и знака подключен к выходу переноса сумматора, информационна группа входов блока выработки переносов и знака подключена к группе выходов суммы сумматора и к информационной входов счетчика,- первый и второй входы -переноса которого подклю.чены соответственно к первому и второму, входам переноса из младшего восьмеричного разряда устройства, первый и второй .выходы переноса блока выработки(Переносов и знака явля% ются выходами переноса в старший восьмеричный разряд устройства, вы(Л ход знак. блока выработки переносов и знака ;пЪдключен к входу триггера з.нака, выход которого и выходы счетчика образуют группу выходов результата устройства, управляющие входи I сумматора и счетчика являются соответственно первым и вторым входами синхронизации устройства. 4 1.1 4 X) ./ :п JV

0010 ООН 0100 п

0000 0001

0000

1111 1110 1101 П.0100

1101

Продолжение таблицы

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ДВОИЧНЫЙ СУММАТОР | 1971 |

|

SU436350A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сложения в избыточной двоичной системе | 1977 |

|

SU717763A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

Авторы

Даты

1983-09-07—Публикация

1982-05-07—Подача